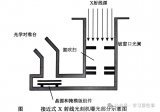

光刻是芯片制造技术的主要环节之一。目前主流的芯片制造是基于193nm***进行的。但是193nm的光刻技术依然无法支撑40nm以下的工艺生产,为了突破工艺极限,厂商不得不将193nm液浸技术和各种多重成像技术结合起来使用,但这在无形中提升了制造成本,拉长了工艺周期。为了通过提升技术成本来平衡工序成本和周期成本,厂商们将底牌压在了EUV***身上,但是EUV真的能够满足厂商们的期盼吗?

EUV技术再度突破

在半导体制程中,光刻工艺决定了集成电路的线宽,而线宽的大小直接决定了整个电路板的功耗以及性能,这就凸显出***的重要性。传统的***,按照光源的不同,分为DUV***(深紫外光)以及EUV***(极紫外光)。工艺制程还在28nm徘徊时,DUV***无疑是最佳的选择,但是随着工艺制程的升级,想要迈向更小的线路,就只能使用EUV光刻工艺。

目前最先进的EUV光刻工艺使用的是13nm光源,能够满足7nm线宽制程工艺的要求。全球能够达到这种水平的***制造商暂时只有一家——ASML。据记者了解,目前ASML具有16500人,研发人员超过6000人,占比约为36%,整个公司主要的业务为***,技术绝对处于世界领先水平,市占率100%,处于轻松垄断全球市场的地位。

2018年,ASML财报全年营收净额达到109亿欧元,净收入26亿欧元,虽然火灾影响了2019年第一季度的业绩,但是其2019年第一季度的营收净额依然达到了21亿欧元,毛利率约为40%。ASML总裁兼首席执行官Peter Wennink介绍,ASML在2018年完成了技术创新的里程碑突破,并表示这一突破将为未来几年不断筑能。

据了解,在2017年,ASML就曾表示达到过“里程碑的突破”,原因便是完成了250瓦的EUV光源技术的升级迭代,让EUV的生产率达到125片/小时的实用化。

EUV***的极限挑战

据ASML 2018年财报,目前ASML推出的NXE:3400C极紫外***EUV,产量可达每小时170片晶元,妥善率高达90%以上。该机型预计于2019年下半年出货至客户。除此之外,对于3D NAND客户,ASML还提供了一系列处理翘曲的晶圆的辅助方案,扩大可处理晶圆变形范围。据ASML官方透露,目前其产品可帮助用户实现每天超过6000片晶圆的产量。

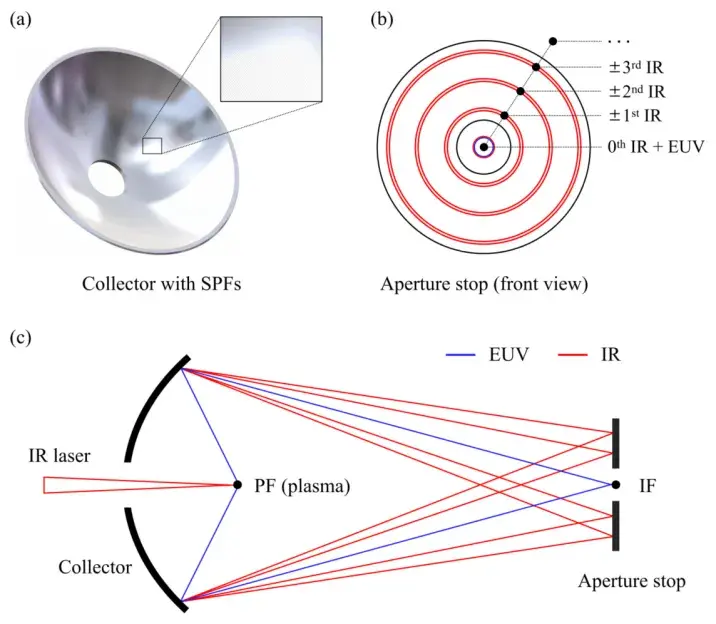

“要实现强大的功能,EUV就必须克服电能消耗以及光源等因素的影响。”中国电子科技集团公司第四十五研究所集团首席专家柳滨向记者表示,EUV虽然售价超过了一亿美元,但是高额的价格并不是它最大的问题。“EUV最大的问题是电能消耗。电能利用率低,是传统193nm***的10倍,因为极紫外光的波长仅有13.5nm,投射到晶圆表面曝光的强度只有光进入EUV设备光路系统前的2%。在7nm成本比较中,7nm的EUV生产效率在80片/小时的耗电成本将是14nm的传统光刻生产效率在240片/小时的耗电成本的一倍,这还不算设备购置成本和掩膜版设计制造成本。”柳滨说。

据了解,除了电能以及光源,光刻胶也是EUV技术另一个需要面对的问题。据专家介绍,光刻胶本身对于光的敏感度就十分高,但是对于不同波长的光源,光刻胶的敏感度也有差异,这就对EUV***产生了一些要求。***选择的波长必须要和光刻胶对应的波长处于同一个波段,这样才能提升光刻胶对于光源的吸收率,从而更好地实现化学变化。但是目前,EUV***在材料搭配方面还不成熟,很多专家将这个问题列为“***极限挑战之一”。

发展EUV仍需大力支持

虽然EUV***设备还有诸多挑战尚未克服,但不得不承认的是,高端工艺制程的发展依旧难以离开EUV***的辅助。“一代器件,一代工艺,一代设备”点出了当今半导体工业发展的精髓。尤其是当线程工艺进入纳米时代之后,工艺设备对于制造技术的突破越发重要。

自上世纪90年代起,中国便开始关注并发展EUV技术。最初开展的基础性关键技术研究主要分布在EUV光源、EUV多层膜、超光滑抛光技术等方面。2008年“极大规模集成电路制造装备及成套工艺”专项将EUV技术列为下一代光刻技术重点攻关的方向。中国企业将EUV列为了集成电路制造领域的发展重点对象,并计划在2030年实现EUV***的国产化。

然而,追求实用技术是企业的本能,追求最新技术却不符合企业效益。因此先进的EUV技术,光靠企业和社会资本是无法支撑起来的,对于企业来说,研发技术缺少资金的支持;对于社会资本来说,缺乏热情的投入,因此,这项技术需要政府的支持,需要国家政策的推进。

-

半导体

+关注

关注

339文章

31192浏览量

266324 -

EUV

+关注

关注

8文章

615浏览量

88948 -

ASML

+关注

关注

7文章

738浏览量

43628

发布评论请先 登录

国产光芯片大突破,算力超百倍,绕开EUV

中国打造自己的EUV光刻胶标准!

俄罗斯亮剑:公布EUV光刻机路线图,挑战ASML霸主地位?

台阶仪在集成电路制造中的应用:高端光刻胶材料纯化研究进展

垄断 EUV 光刻机之后,阿斯麦剑指先进封装

今日看点:华为2025年销售收入超8800亿元;ASML公布EUV光源技术突破

EUV光源重大突破!ASML:芯片产量将提升50%

泽攸科技 | EBL和EUV光刻机有何区别?如何影响半导体行业?

白光干涉仪在EUV光刻后的3D轮廓测量

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

EUV光刻胶材料取得重要进展

中科院微电子所突破 EUV 光刻技术瓶颈

EUV技术再度突破 但发展EUV仍需大力支持

EUV技术再度突破 但发展EUV仍需大力支持

评论