Testbench

testbench是一种验证的手段。首先,任何设计都是会有输入输出的。但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估。那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟平台”的产生。在这个平台上你可以对你的设计从软件层面上进行分析和校验,这个就是testbench的含义。

简单的Testbench设计

//timescale 仿真时间单位/时间精度(时间精度不能比时间单位还要大)

timescale 1ns/1ps

//定义一个无输入无输出的Moudle

module Led_clg_tst();

//被测设计的输入信号,对应测试脚本的输出信号(注意要定义成reg)

reg clk;

reg rst_n;

//被测设计的输出信号,对应测试脚本的输入信号(注意要定义成wire)

wire led;

//例化待测模块

Led led_test

(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

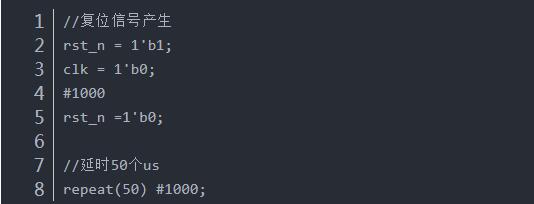

//使用Initail生成rst_n激励

initial

begin

//监控Led信号变化

monitor(monitor(time,”led value= %b\n”,led);

end

//使用alwasys模拟产生25M的时钟信号

always #20 clk = ~clk;

endmodule

-

设计

+关注

关注

4文章

829浏览量

71490

发布评论请先 登录

简单高效的鸿蒙编译提速技巧

linux-arm开发环境的简单配置

合科泰教你如何焊接简单LED闪烁电路

在verilog testbench中运行测试用例时,运行到make run_test出错怎么解决?

求助,关于C代码中的printf打印的疑问求解

想调用VCS+VERDI测试蜂鸟,按照网上的弄了,但是没有波形,为什么?

求助,关于testbench仿真的问题求解

看似简单的自动泊车需要哪些技术支撑?

【精选直播】openDACS 2025 开源EDA与芯片大赛 赛题二 赛题四 直播宣讲会

语法纠错和testbench的自动生成

分享---简单快速实现烘烤设备UI界面的方法

莱姆传感器接线指南:简单易懂的步骤

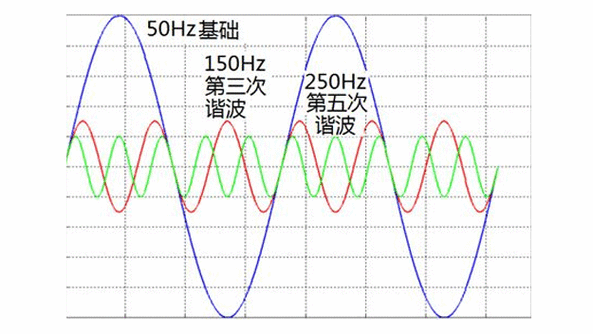

谐波怎么处理最简单的方法

简单的Testbench设计

简单的Testbench设计

评论