LVDS 基础系列旨在提供低压差分信号技术的基础知识。 本视频系列分为五个部分。 分别为 LVDS技术概述,LVDS 的优点, M-LVDS 和三种常用的通信架构,LVDS 数据速率, 以及 LVDS 接口的典型用例。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ti

+关注

关注

114文章

8084浏览量

220031 -

通信

+关注

关注

18文章

6450浏览量

140269 -

lvds

+关注

关注

2文章

1242浏览量

70233

发布评论请先 登录

相关推荐

热点推荐

嵌入式分享#51:为什么手机屏常用MIPI,而车载屏用LVDS?

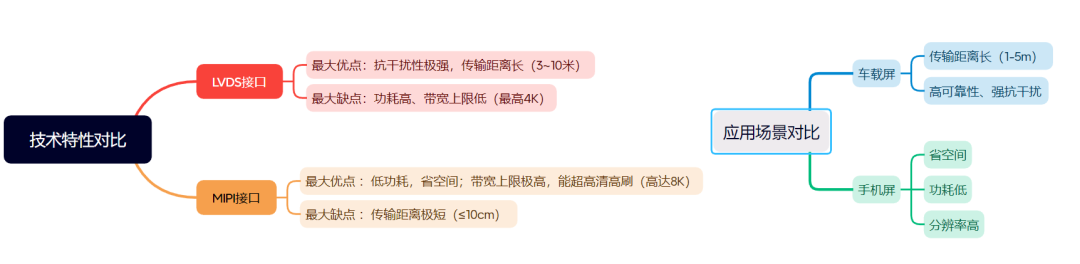

为什么? 原因无非就是 MIPI 与 LVDS 两者技术特性与应用场景结合的必然结果 。因此,要想知道为什么,直接对比两者的技术特性以及两种应用场景的特点就能得到结论。 技术特性对比 (1)LVDS 接口 最大优点:抗干扰性极强

SN65LVDS311:可编程27位显示串行接口发射器的设计与应用

SN65LVDS311:可编程27位显示串行接口发射器的设计与应用 在电子设计领域,对于显示接口的需求日益增长,尤其是在需要高效数据传输和低功耗的应用场景中。TI的SN65LVDS31

深入剖析SN65LVDS95 LVDS 串行器:特性、应用与设计要点

的 SN65LVDS95 作为一款典型的 LVDS 串行器,在数据传输系统中发挥着重要作用。今天,我们就来深入了解一下这款芯片。 文件下载: sn65lvds95.pdf 芯片概述

SN75LVDS32与SN75LVDS9637高速差分线接收器:设计与应用指南

(TI)的SN75LVDS32和SN75LVDS9637高速差分线接收器,就是LVDS技术的典型代表。本文将深入探讨这两款接收器的特点、性能参数以及应用场景,为电子工程师在实际设计中提

《SN65LVDS109与SN65LVDS117:LVDS重复器的卓越之选》

《SN65LVDS109与SN65LVDS117:LVDS重复器的卓越之选》 在电子设计领域,数据传输的高效性、稳定性与精确性一直是工程师们追求的目标。今天,我们聚焦于德州仪器(TI)推出的两款

深入剖析SN75LVDS83A:LVDS显示发射机的卓越之选

、SN75LVDS83A的特性亮点 2.1 接口与兼容性 直接连接LCD面板 :LVDS显示串行解串器接口可直接连接集成LVDS的LCD显示

【新品】ZYNALOG徴格半导体推出ZGN4XXX系列LVDS/M-LVDS高速接口芯片

ZYNALOG徴格半导体正式推出ZGN4XXX系列高速接口芯片。该系列涵盖LVDS线路驱动器、LVDS线路接收器以及M-LVDS收发器,为您的背板数据传输、有线数据传输、时钟分配提供高

STMicroelectronics B-LVDS7-WSVGA 7英寸LCD模块技术解析与应用指南

STMicroelectronics B-LVDS7-WSVGA 7" TFT LCD模块集成了一块7” TFT LCD和电容式触摸面板。超宽视角模块具有LVDS接口模式。提供LVDS

LVDS接口的显示屏,显示偏暗问题的解决方法

问题:点亮屏幕后画面显示偏暗

可能原因:

主板输出的LVDS 模式与屏幕的不一致;

PWM亮度并未调节到最亮;

解决方法

检查主板的LVDS输出模式是否和屏幕一致;

一般主板端的LVDS模式是可以配置的,配置成与屏幕相同的模式

发表于 10-09 15:55

液晶显示屏LVDS接口JEIAD 、VESA、18bit LVDS关联和区别

分享下液晶显示发展史上一个重要且有趣的阶段。LVDS接口不同格式的形成,根本上是成本、带宽和市场需求之间博弈和演进的结果。

下面我将详细解释它们的历史成因、关联与区别。

核心概念:什么是LVDS

发表于 08-30 09:13

嵌入式接口通识知识之LVDS接口

的特点是每对信号线(正负极性)之间的电压差是信号的有效部分,而不是单独的电平。这种差分传输方式使得LVDS接口在长距离传输时能够保持较高的抗干扰能力和数据传输速率。它的主要工作原理就是将发送端将输入信号

发表于 08-29 15:52

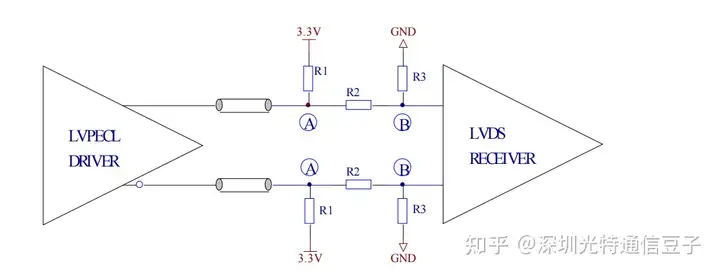

LVPECL 与 LVDS 及 PECL 与 LVDS 的互连技术解析

在高速光通信系统中,LVPECL(低压正射极耦合逻辑)、PECL(正射极耦合逻辑)与 LVDS(低压差分信号)是常用的高速接口电平标准。LVPECL/PECL 以高速度、低噪声特性广泛应用于光模块

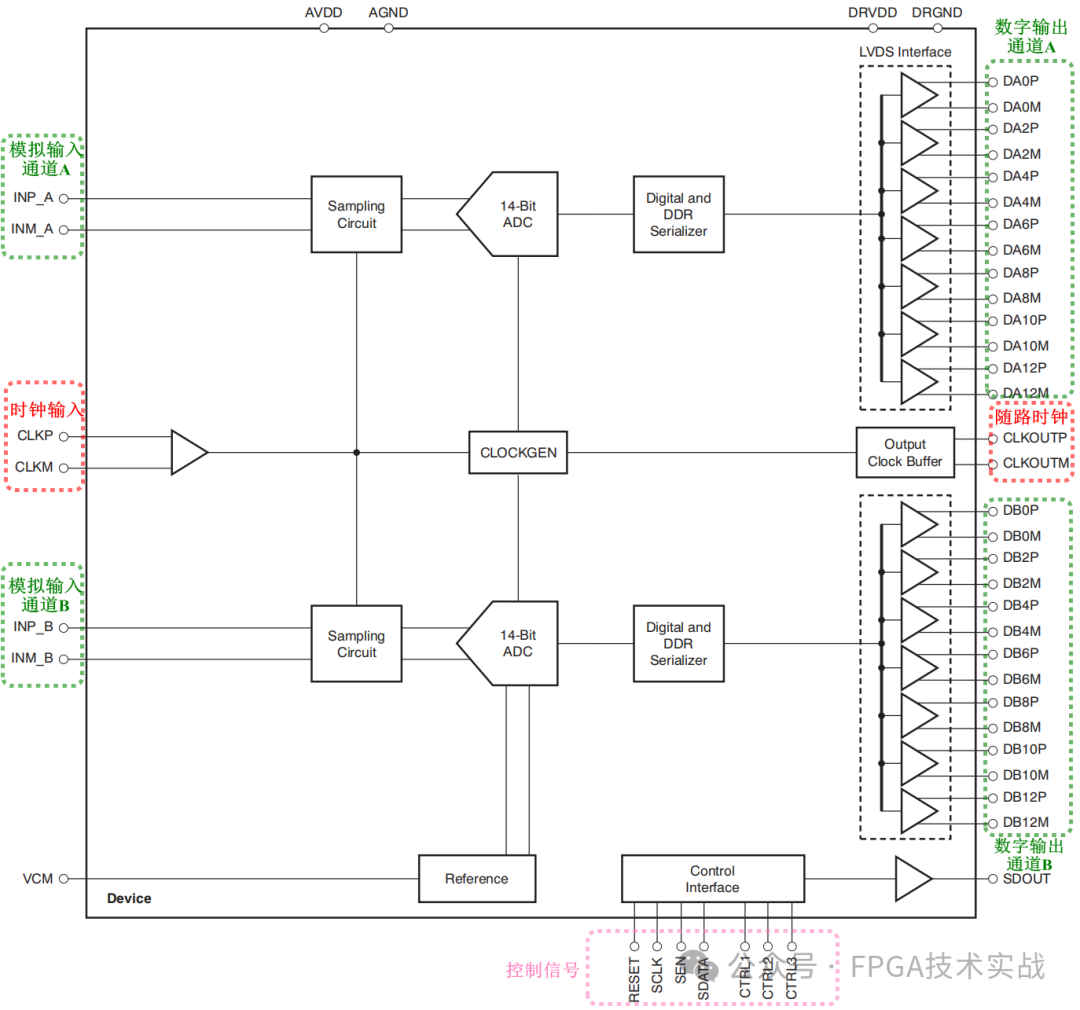

Altera FPGA与高速ADS4249和DAC3482的LVDS接口设计

引言: 本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。本文

LVDS接口的典型用例分析

LVDS接口的典型用例分析

评论