最近圈里都在聊涨价,英特尔、AMD从3月开始陆续上调价格,桌面端涨个10%—15%还能接受,但服务器那边,64核、96核的型号上涨20%,交期半年。

但对一线工程师来说,卡住项目的往往不是算力,而是系统的持续稳定运行。往下排查,你会发现容易被忽视的地方是晶振。

当AI从训练走向Agent推理,系统结构也随之变化:CPU参与更多,链路更长,同步要求更高。结果是——GPU算错还能重来,但时钟一旦出问题,系统通常没有“重来的机会”。

一、为什么AI服务器更“挑”晶振?

以前做服务器,时钟是“够用就行”。现在不行了,400G / 800G互联上来之后,整个系统的状态变得很“敏感”:

接口变多:PCIe 5.0 / 6.0、SerDes、以太网,全都挂在参考时钟上,一颗156.25MHz往往带整条链路

链路变长:CPU ↔ GPU ↔ NIC ↔ 光模块,抖动不是被吸收,而是一路被放大。

负载变复杂:Agent推理带来的调度、IO、中断明显增加,时钟问题会直接体现为 latency 抖动。

挺直观的对比:GPU算错,大不了重算。时钟一旦抖或者失锁,系统直接异常。

AI服务器不是需要高频,而是需要“干净的频率”。

二、服务器里的三类晶振,分工明确

拆一台2U服务器看,会发现时钟大致分三类,不是一个东西能搞定的。

1)156.25MHz差分晶振:高速链路的“中枢”

主要用在:PCIe,以太网 PHY,光模块链路。

为什么几乎都用156.25MHz?

不是标准规定死的,而是工程上筛出来的最优解——它和主流高速协议是整数倍关系,PLL倍频简单,抖动更好控制。

常见搭配基本已经形成“默认答案”:GPU主板:2520 + HCSL(空间紧,密度优先)

时钟分发:3225 6Pin(带OE)(方便控功耗、压EMI)

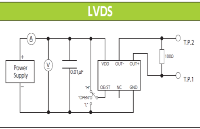

简单记一条就够:PCIe → HCSL,板内通用差分 → LVDS,更高速链路 → LVPECL。

2)50MHz / 25MHz无源晶振:容易被“低估”的频率

50MHz关键不是频率,而是负载电容(CL)匹配

不匹配的结果很直接:频偏,甚至不起振

25MHz看的是高温起振能力,这块一旦不稳,远程管理会非常“玄学”

现场很多问题最后会发现:参数都对,但系统就是不稳,根因其实是匹配没算清楚。

3)32.768KHz RTC:不影响性能,但很“烦人”

它不参与高速链路,但决定系统时间。

问题往往出在这里:分布式训练日志对不齐,定时任务乱跑,证书校验异常。

选型其实不复杂,就两点:精度:±20~50ppm,功耗:耗电低。

三、最常见的4个坑,基本每个项目都踩过

很多问题不是没有,而是排查太晚才意识到是晶振。

坑1:只看频率,不看抖动

现象很典型:PCIe误码率压不下去,偶发掉包。

结论很简单:频率只是门槛,抖动才是决定因素。

坑2:输出格式选错

常见翻车方式:PCIe用成LVDS,HCSL没做端接。

结果就是:链路不稳定,EMI变差,调试时间直接翻倍。

这类问题没有“调一调就好”,本质是选型错了。

坑3:无源晶振匹配问题

表现很迷惑:BMC高温重启,系统偶发起不来。

但你看规格书,全部都“对”。

真正的问题在于:CL没匹配好 / 起振裕量不够

这类是典型的:看起来没问题,其实早就埋雷了。

坑4:RTC被忽略

平时没人关注,一出问题就很烦:多节点时间漂移,日志对不上。

原因通常是:不同批次精度不一致,它不影响性能,但会拖慢整个系统调试节奏。

四、为什么这些问题现在更容易爆?

其实这些坑以前就有,只是现在更“敏感”了。

原因很现实:CPU更贵,容错空间变小,项目周期更紧,调试时间被压缩

AI负载更复杂,对时钟更敏感。以前能“凑合用”的,现在基本都会出问题。

实际项目,推荐按这个来:先定接口 → 再定频率 → 再选输出 → 最后看封装和成本。

比如:

1)先确认:PCIe / SerDes / Ethernet

2)再定:156.25MHz / 50MHz / 25MHz

3)再选:HCSL / LVDS / LVPECL

4)最后才是:2520 / 3225 / 2016

很多问题不是晶振不行,而是:接口和输出没对上,后面再怎么调参数,都很难救回来。CPU在涨价,交期在变长,这些短期都不会变。

但真正影响项目交付的,往往不是那颗最贵的芯片,而是这些基础器件:156.25MHz差分晶振,50MHz系统时钟,25MHz网络时钟。

它们决定的是:链路能不能跑满,系统稳不稳定,项目能不能按时交付。

在算力越来越贵的阶段,有时候,晶振选对,比多上一颗CPU更有价值。

说到底,选晶振跟选IC很像:参数对得上只是基础,交期稳、服务跟上,才是项目里真正有价值的部分。

关于SJK晶科鑫:几个工程师关心的常见问题。

Q:无源晶振的精度和稳定性怎么样?

25MHz、50MHz常规做到±30ppm,出货前全检频率,服务器BMC、SoC够用。

另外CL覆盖8pF / 9pF / 12pF / 16pF / 18pF,不用改外围。

Q:156.25MHz差分晶振交期能不能稳?

现在是需求高峰,常规型号4–6周交付。

3225、2520都有产线,不会出现“换封装还是要等”的情况。

打样阶段可以给Phase Noise实测数据,方便直接评估。

Q:RTC有什么区别?

SJK的32.768KHz RTC晶振功耗偏低;智能电表、保护设备上大量在用,兼容JXR151T/JXR191T系列,户外场景都能扛。

Q:小批量支持吗?

前期可以先拿样验证,确认OK再上量。对验证周期长的服务器项目比较友好。

-

晶振

+关注

关注

35文章

3649浏览量

73861 -

AI服务器

+关注

关注

3文章

193浏览量

5574 -

差分晶振

+关注

关注

0文章

193浏览量

2101

发布评论请先 登录

高稳定低抖动156.25 MHz LVDS晶振:破解高速AI与云计算时钟瓶颈

NDK有源晶振与FPGA的协同设计

AI服务器晶振选型:156.25MHz差分晶振封装2016/2520/3225怎么选?

AI服务器晶振选型:156.25MHz差分晶振封装2016/2520/3225怎么选?

评论