文章来源:十二芯座

原文作者:MicroX

本文介绍了芯片设计中的版图效应。

为了降低成本和提高性能,芯片尺寸一直在不断缩小。密度的增加是通过推动器件尺寸和缩小图案尺寸来实现的。随着CMOS缩放扩展到28nm技术,晶体管不再以其宽度和长度来充分表征,而是进一步取决于其他版图几何参数和周围的邻域。因此,布局依赖效应(LDE) 成为一个严重的问题,不容忽视。

LDE, Layout Dependent Effect

就是“版图相关效应”或“布局依赖效应”,指的是在集成电路等电子电路设计及制造领域,电路的性能、制造良率以及电磁兼容性等方面会受到电路版图布局情况影响的一系列效应。其具体表现为不同的版图布局方式会对信号传输、功耗、电磁干扰以及制造过程中的成品率等诸多方面产生不同程度的影响。

Layout相关效应(LDE)主要包含以下几个方面:

1. WPE(Well Proximity Effect)

2. LOD(Length of Diffusion)

3. OSE(OD Space Effect)

4. PSE(Poly Space Effect)

5. MBE(Metal Boundary Effect

6. CPO(Cut-Poly Effect)

1. WPE

WPE(Well Proximity Effect)阱邻效应是指在半导体制造过程中,由于离子注入工艺导致的掺杂浓度在阱边缘附近不均匀分布的现象。这种现象在先进工艺技术下尤为明显,会对器件的电特性产生显著影响,主要体现在阈值电压、迁移率和体效应上。

原因:在进行阱离子注入工艺时,离子在光刻胶边界和侧面上发生散射和反射,这些离子会进入到硅的表面,从而影响阱边界附近区域的掺杂浓度,well 边缘掺杂浓度偏高,浓度越高,越难反型,阈值电压越高。

对MOS管的影响

阈值电压(Vt):靠近阱边缘的MOS管阈值电压会发生变化,距离阱边界越近,阈值电压越高。

迁移率:WPE效应也会影响载流子的迁移率,进而影响器件的电流特性,离子浓度越高,迁移率越低。

2. LOD

在CMOS集成电路制造工艺中,在0.13um以下,为了防止MOS管之间的相互干扰,通过在硅片上刻蚀浅沟槽并填充氧化硅,从而形成隔离层,这一过程就称为STI(Shallow Trench Isolation)工艺。

OSE和LOD效应都来自于于STI,但它们的影响和形成机制有所不同。LOD效应主要受到STI到Gate的距离影响,而OSE主要由STI自身宽度的不同所引起的应力变化进而影响 device performance。

LOD(Length of Diffusion)Effect,也称为STI Stress Effect,顾名思义就是有源区外的STI隔离会对其带来应力作用,由器件间的浅沟隔离造成的这种应力会影响器件中的载流子迁移率,从而从而影响晶体管阈值电压,影响电流。这被称为“扩散长度”效应(Length of Diffusion effect,LOD),其中器件的特性根据其栅极与扩散边缘的距离而变化。通常用Poly到有源区边界的距离(SA/SB,如下图所示)来描述。

channel方向:拉应力让NMOSFET更快,压应力使PMOSFET更快,为了提高电路的性能,我们更希望在PMOS上施加一个压应力(Compress stress),在NMOS上施加一个拉应力(Tensile stress)。

LDE效应的设计技巧 为了在设计中考虑LDE效应,可以使用各种布局技术: 1.使用相似的扩散尺寸、形状和方向 2.增加器件与井边缘的分离距离 3.添加虚拟器件(dummy device)和或虚拟多晶硅(dummy poly),以使指状器件更加均匀

3.OSE

OSE(OD space effect, AA to AA space effect),也代表 STI 隔离的宽度。在65nm之前的工艺制程中,OSE的影响并不明显,所以STI stress effect单纯指LOD effect。 而45nm以下的工艺制程,OSE的影响就不能再被忽略了。

首先 OSE 越宽,就表示 STI 的宽度越大,也就是说 STI 所提供的压应力越大。

对于 OSEX, NMOS 希望受到拉应力,PMOS希望受到压应力。因此随着 OSEX 效应的加剧,PMOS 的电流(性能)会提升,NMOS 的电流(性能)会下降。这对于 PMOS 的性能是有好处的,可是对于 NMOS 的性能则是不利的。因此OSEX 对 N/PMOS 性能影响理论上趋势相反。

对于 OSEY, NMOS 和 PMOS 都希望受到拉应力,STI 对 N/PMOS 影响一致。故看 OSEY 对 MOS 器件的性能影响,N/PMOS 理论上趋势一致。

4.PSE

器件Poly与附近Poly间距的不同,对器件性能产生影响的一种效应。对target gate poly影响的大小:1st poly影响大于2nd poly。一般情况下2nd poly之外的poly对器件本身影响就会很小,通常忽略不计。

根据相关Design rule,控制target gate到1st poly的距离和到2nd poly的距离使其满足规则。

如何降低影响:增加dummy PO,一般利用工艺自带撒dummy的rule来添加,满足PO密度要求的同时,也可以减小PSE效应的影响。

5.MBE

N/PMOS管金属边界之间的距离也会影响晶体管特性,这一特性称为MBE.

6.CPO

Poly Cut的位置也会影响晶体管特性,这一特性称为CPO. poly cut 的作用就是利用一张新的 mask 做曝光,将连在一起的 poly 分成两个不同的 poly.

这个的优势在于可以省一定的面积,单独的 poly 伸头的地方不能完全与AA平齐,会有一个 rule 限制,如果使用poly cut 可以大程度的降低这个伸头距离。

如何降低LDE?

1.将同一电位的器件放在一个阱里,适当拉大有源区AA到阱WELL边界的距离(WPE),NMOS距离阱边界较近时,距离越大,阈值电压受的影响越低,但是为了面积成本的考量,不会拉很大,需要权衡;

2.提高管子的对称性并加入dummy,减小STI应力的同时增大了非dummy器件到阱边界的距离;

3.对于电路设计而言,尽可能保持mos管周围及自身环境(AA to AA, Poly space等)一致。

-

CMOS

+关注

关注

58文章

6240浏览量

243459 -

芯片设计

+关注

关注

15文章

1174浏览量

56788 -

版图

+关注

关注

0文章

15浏览量

9533

原文标题:芯片设计中的版图效应

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高薪诚聘IC版图工程师

招聘芯片版图layout讲师

诚聘芯片版图(layout)兼职讲师

诚聘芯片版图兼职老师

版图设计的遵循原则

版图设计资料推荐

在模拟版图设计中堆叠MOSFET

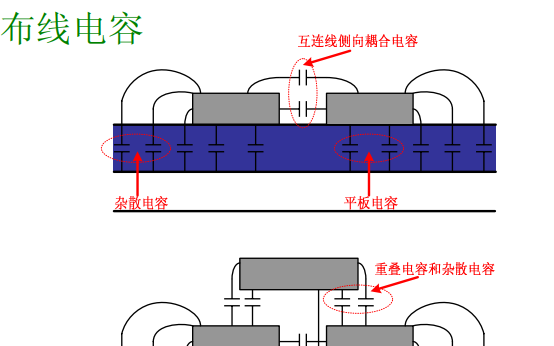

IC工艺和版图设计的电容版图设计的详细中文资料概述

芯片设计中的版图效应

芯片设计中的版图效应

评论