虽然1947年由贝尔实验室的J.Bardeen、W.H.Brattain和W.Shockley等科学家发明的第一个晶体管是双极型晶体管,而且是在锗衬底上,但场效应器件概念的提出比双极型器件更早,20世纪20年代J.Lilienfeld就提出用金属-绝缘层-半导体结构来制作固态三极管的专利申请。图3.28为Lilienfeld提出用来制作场效应器件的结构示意图。它是一个由Al-Al2O3-Cu2S组成的MIS结构,铝作为栅电极,Al2O3为栅介质,Cu2S为半导体,在半导体上有两个电极作为源漏。其工作原理是想通过调节栅电压来改变半导体层中的电导率,从而实现改变源漏电流大小的目的。有趣的是Lilienfeld设想的Al2O。栅厚度约为0.1pm,栅压为100V数量级,所以,在栅介质上的电场强度为10'V/cm,非常接近于当今的硅MOS器件。但由于绝缘层与半导体之间的界面质量问题,当时无法制作具有晶体管特性的器件,不能实现其专利构想。

后来随着双极型晶体管的研究成功,人们对半导体的认识不断加深,从理论上建立了电子、空穴的输运模型,技术上 pn结制备越发成熟,1952年Shockley又提出了以反偏pn结作为栅极的结型场效应晶体管(JFET)。JFET类似于一个电压控制电阻器,为单一载流子导电,因此,Shockley把它称作单极型场效应晶体管。根据这一思路,很快有人做出了JFET原型器件,但是,这种器件沟道厚度依赖于 pn结深的精确控制,只有当60年代出现离子注入技术后,该器件才有制作可行性。这种器件虽然可以避免绝缘层-半导体界面问题的困扰,但其明显缺点之一为栅电压受pn结反偏电压所限制。所以,这种器件目前实际应用不多,倒是与这种器件比较接近的另一种器件肖特基栅或金属-半导体栅场效应晶体管(MESFET)获得较多应用,尤其在那些无法获得高质量绝缘层界面的GaAs等l-V族化合物半导体器件中。无论是JFET还是MESFET,栅极都是一个反偏的结,所以,栅极漏电流都比较大,这对于大规模集成电路极为不利。

随着硅平面工艺特别是热氧化技术的发展,对 SiO2/Si界面的认识越来越深入,使得制备高质量SiO:/Si界面成为可能,因此,人们又致力于研制绝缘栅场效应晶体管。1960年,贝尔实验室的D.Kahng和M. M.Atalla研制出第一个SiO2-Si体系的MOSFET。

MOSFET的基本特性参数只与一种载流子(即半导体表面反型少子)的输运有关,因此,这种器件又称为单极型半导体器件。MOS器件具有一系列独特优点:1高输人阻抗;2高线性度;3具有负温度系数,因而导致均匀温度分布;4器件结构简单,易于高密度集成;5宜于形成互补型MOS器件,大幅降低功耗;6与少子寿命无关,抗辐射能力强,噪声低等。相比于双极型器件,MOS器件也存在一些弱点:1工艺要求高,特别对SiO/Si界面质量控制要求高;2驱动能力较弱;3频率范围小,工作频率较低。随着制造技术进步和器件尺寸缩微,MOS器件的这些弱点正在不断被克服。

3.6.1 MOS晶体管工作原理

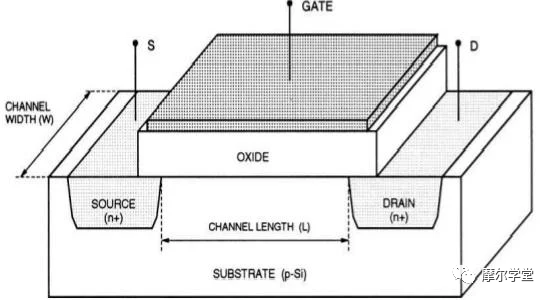

在MOS电容半导体一侧增加两个重掺杂的pn结,就构成一个MOSFET,这两个重掺杂的结区分别称为源(S)极和漏(D)极。以图3.29所示的n-MOSFET为例,分析其工作原理。当栅极电压小于某一值,即阈值电压(V)时,半导体表面未形成强反型层,n源漏与P型衬底之间存在着反偏Pn结,因而不导通。当栅电压大于V时,半导体表面达到强反型,即形成可以导电的n型沟道,只要在源漏之间加上一定电压,就会有电流从源漏端流过。除了具有前面讨论的栅(G)、漏(D)、源(S)等3个电极外,MOSFET还有一个衬底电极(B)。在单管应用时,衬底电极通常与源极一起接地;在集成电路中,源极不一定与衬底同电位。

下面以图3.29所示的坐标系推导 n-MOSFET的电流-电压特性。当栅源电压Ves>V时,n-MOSFET开启,栅极下形成n型沟道,源漏两端的外加电压(Vs),将产生一个从源端(0V)到漏端(Vs)的沟道电位分布V(y),沿沟道的横向电场为

从(3.47)式可见,在Vs由零起始邻近小值范围内,括号中的Vs平方项可忽略,因而Is随V增大呈线性上升。此时可近似认为,V仅起提供y方向漂移电场的作用,而对沟道电荷没有影响,沟道可看成只受Vcs调控的均匀薄电荷层,如图3.30(a)所示,Is随Vs的关系类似线性欧姆定律。当漏电压增大到VomtVes一V+时,由(3.46)式可知,沟道在漏端的反型电荷浓度降至零,此时沟道被夹断。但沟道夹断并不意味着没有电流流过,因为在夹断点(沟道的尽头)另一侧存在着漏端反向np结,在其电场作用下,到达沟道尽头的载流子将被收集到漏端流出,如图3.30(b)所示。继续增大V,使夹断点向源端移动,如图3.30(c)所示,若夹断点位移远小于沟道长度,则Is保持不变,即电流达到饱和,进入饱和区,形成如图3.31所示MOSFET典型Igs-Vs特性曲线C。饱和电流可写为

在上述简单模型中,忽略了体电荷效应,即忽略耗尽层空间电荷(Q:)随源漏电势变化,考虑V或V(y)对体电荷影响后,应将(3.45)式改写为

从(3.50)式可以看出,考虑体电荷效应后,MOSFET的I-V特性就不存在统一的V。另外,从(3.49)式可见,考虑体电荷效应后,反型层电荷浓度会变小,因此,最终MOSFET的电流会变小,饱和电压Vrku也会相应变小。

3.6.2 MOS晶体管类型

前述介绍的是n型沟道MOSFET(简称NMOS),与之相对应的是以空穴为反型载流子的p型沟道MOSFET(简称 PMOS)。其所需施加的电压极性正好与NMOS相反,即栅极和漏极需要施加负电压,才能使器件工作。

对于MOSFET,根据不加栅压时是否形成沟道,可分为两种类型:零栅压下无沟道形成的MOSFET称为增强型;而零栅压下已形成沟道的MOSFET称为耗尽型,即:需要在栅极上施加相反方向的电压才能使器件截止。按以上定义,增强型NMOS、耗尽型NMOS、增强型PMOS、耗尽型PMOS这4种器件的输出特性和转移特性,如图3.32所示。

3.6.3 MOS晶体管的阈值电压

在数字MOS集成电路中,最基本的单元反相器,可由一个驱动管和一个负载构成,负载可以是电阻或MOS管。为降低电路功耗,通常希望驱动管是增强型。根据不同沟道MOSFET的分类,可以将NMOS和 PMOS的阈值电压分别表示为

其中,Vm由(3.37)式确定。上式表明,阈值电压由衬底掺杂浓度、栅极功函数(Wm)、氧化层厚度及其中电荷密度等因素确定,

由于早期硅MOS结构中氧化层正电荷密度较高,VmB常为较大负值,因而增强型PMOS器件较易实现,而较难使NMOS的Vr变为正值,即不易实现增强型NMOS器件。所以,最早研制成功的 MOS晶体管是铝栅增强型PMOS器件。后来人们发现重掺杂多晶硅也可以作为MOSFET栅极,由于多晶硅栅工艺具有自对准特性,可以降低栅漏交叠电容,有益于显著提高MOS器件速度。最初采用的多晶硅栅是n型重掺杂材料,其功函数约等于硅的亲合能gX(4.05eV),与铝的功函数(4.20eV)接近,最初仍然用于增强型PMOS工艺由于硅中电子迁移率高于空穴迁移率,制备增强型 NMOS成为早期MOS技术研究的聚焦点。随着离子注人技术进展,人们可以把适当剂量的杂质(如硼)精确地注人半导体,把NMOS的V从负调整为正。如硼注入剂量为Nm,假设其位于靠近半导体表面极薄区域内,则可证明阈值电压的增加幅度为

后来,人们发现由NMOS和PMOS组成的CMOS具有特别低的静态功耗,所以,需要在单一芯片同时制造NMOS和PMOS。由于n型多晶硅具有较低电阻率,因此,在早期CMOS中无论对于NMOS还是PMOS,均采用了n多晶硅栅。随着衬底浓度提高,NMOS的V变得越来越正,而PMOS的Vr变得越来越负,这两种变化趋势均有利于二者制作增强型器件。但对于CMOS反相器,希望NMOS和PMOS具有对称的Vr,而且希望|Vr|随着器件尺寸缩小而有一定降低,所以,在0.5um以下的CMOS工艺中,就开始采用双多晶硅栅技术,即NMOS用n多晶硅栅、PMOS用p多晶硅栅,这样,可将|Vr|控制在1V以内且比较对称。随着器件尺寸进人纳米领域,硅CMOS器件制造技术不断创新,在45 nm及更小器件尺寸技术代中,这种SiO2/多晶硅栅叠层结构逐步被高k介质/金属栅取代。

在上述讨论中,假定MOSFET的源和衬底是短接的。在实际情况中,如全由增强型晶体管构成的EE MOS反相器中,负载管的源衬是反偏的,这时MOSFET的阈值电压就会比源衬短接时的要来得大,这种效应称为衬偏效应。当存在衬偏电压Ves时,若要使MOSFET的沟道反型载流子浓度达到无衬偏时同样的浓度,即:沟道相对于源端的势垒高度必须不变,沟道位置的表面势必须增加一V的,空间电荷面密度按规律增加,则阈值电压变为

在离子注人发展成熟以前,TBM的研究人员曾利用衬偏效应增大V1,使NMOS成为增强型器件,以便在IBM-370/158计算机制造中能采用比PMOS速度更快的 NMOS。

3.6.4 MOS器件跨导和短沟道特性

MOS器件除了V+这一关键参数外,还有其他多个重要参数。MOSFET是一种栅控电流器件,衡量其栅控能力的物理参数可以定义为gm0I,称为跨导,线性区和饱和区的跨导分别可由(3.47)式和(3.48)式计算得到。当器件工作在线性区时,还有另一个重要参数,即沟道电导,定义为gb=0Vv,其大小也可由(3.47)式计算得到。有趣的是,线性区的电导正好等于饱和区的跨导,它们都与跨导因子K有关,即与载流子迁移率、栅电容、器件宽长比成正比。

要提高跨导因子K,一般可以选择迁移率高的导电沟道(如NMOS),减薄栅介质,增加宽长比。当然几何尺寸的改变不是无限的,在某一技术节点下它们通常遵循一定比例。但在同一技术节点下,若想使PMOS达到与NMOS相类似的跨导,常用方法为增大PMOS器件宽长比的方法。例如,选择宽长比为NMOS器件的2~4倍。

MOS器件应用于数字电路时,有两个电流值也很关键,即通态电流IoN和关态电流LoFF。其中,Ioy定义为当Vs=Vu、Vs=Vaa(电源电压)时的I,它标志器件驱动能力与逻辑电路速度;IoFF定义为当Ves=0V、V=V。s时的Igs,它与MOSFET的亚阈值特性有关它标志器件截止时的功耗或者CMOS的静态功耗。所以,对于电路应用而言,Io越大越好,IoFF越小越好。

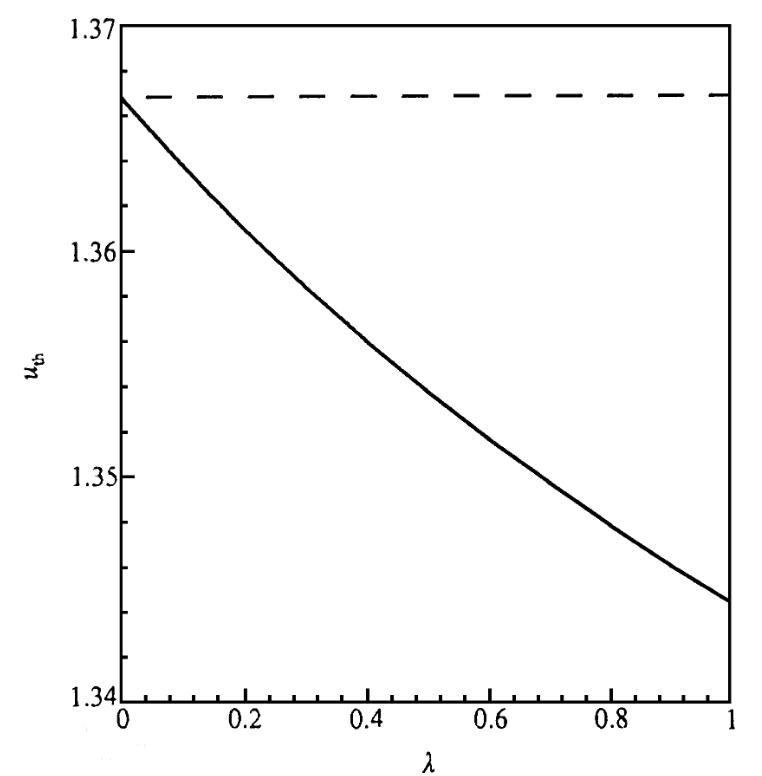

前面讨论的都是针对长沟道器件,即沟道长度比源漏结耗尽层宽度要大得多的MOS器件。当沟道长度缩短时,就会出现一些新现象。第一个效应是沟道长度调制效应,如图3.30(c)所示,当MOSFET进入饱和区后,沟道夹断点不断地向源端移动,使得有效沟道长度不断变短,若本身沟道长度较短时,这种夹断点的移动将使Is略微增大,即Irs的"饱和"变得不饱和,这类似于双极型晶体管中的基区宽度调制效应,即Early效应。这一效应使MOSFET饱和区的输出阻抗从理想的无穷大变成有限值,在输出特性曲线图上可以看到,输出特性饱和区曲线反向延长会与电压轴相交于一点,该点电压为一VA,VA即为Early电压。第二个效应是短沟道效应(SCE),即对于同样 MOS结构,当沟道长度缩短时,由于栅极下耗尽层电荷同时被栅极和源漏分享,使得Vr的绝对值减小。第三个效应是漏致势垒降低(DIBL)现象,指在短沟道MOS晶体管中,Va可能产生使表面势垒降低及Vr减小的效应,如图3.33所示。这种效应可以用DIBL因子=-Vr/Vas标志,单位为mV/V。DIBL是一种有害现象,V随Vs变化意味着MOS栅控能力变弱。在极端情形下,VT趋向于零,即IDS无法关断。

3.6.5亚阈值特性

以上讨论的Is表达式,描述MOS表面形成强反型沟道后的电流。在MOSFET实际应用中,许多时候MOS表面处于弱反型状态,即工作在亚阈值区域,此时Is称为亚阈值电流。由于处于弱反型状态,反型载流子浓度很低,因此漂移电流很小。此时MOSFET与BJT类似,其表面和体内能带如图3.34所示,亚阈值电流主要由载流子扩散流构成。根据沟道两端电子浓度n(0)和n(L),通过下式可以计算出这种扩散电流:

由(3.56)式可见,亚阈值电流与表面势呈指数依赖关系。另一方面,在亚阈值区MOSFET表面势与栅压基本呈线性关系,所以,Is与Ves也基本呈指数依赖关系,如图3.35所示。可以用亚阈值斜率判断MOSFET亚阈值特性的优劣。斜率越大,曲线越陡峭,意味着开关转换越快。亚阈值特性常用亚阈值摆幅(参数S)作定量描述。参数S反比于亚阈值斜率,其定义为漏源电流降低一个数量级对应的栅电压减小量,如下式所示:

所以,S的大小最终可归结为栅压对表面势的调控能力。在弱反型时,dVcs/dy,可以通过MOS电容串联模型得到,即dVcs被分配到串联着的C.和C。上,因此,亚阈值摆幅可由下式表达:

室温下S不可能小于60mV/dec,通常约为70~100mV/dec。为得到陡峭的亚阈值特性,在器件设计中需要减小氧化层厚度、降低沟道掺杂浓度,在工艺中降低界面态密度。MOS晶体管在低温下工作时,亚阈值特性也可改善。

IoN和IoFF除了主要取决于阈值电压Vr,IoFF还与亚阈值斜率有关。图3.35中标出了IoN和IorF的位置。如前所述,基于扩散-漂移输运机制的参数S,室温下不可能小于60mV/dec。因此,对于固定Va,降低Vr可以提高Iov,但同时会增大IoFe,而增大Vr则可以降低IorFF,但同时又使Iox降低。当然,倘若某种基于其他输运机制器件的S可以突破60mV/dec的限制,则Vr的设计将变得更为容易,即可以将Vr设计得更低(如0.2V),这样就可以使器件在相同IorFF下得到更高的IoN,当然也可以将电源电压Va设计得更低,这有利于降低电路功耗。

3.6.6CMOS器件

为避免早期增强型-增强型MOS反相器和增强型-耗尽型MOS反相器功耗大的问题,Wanlass和 Sah在20世纪60年代初提出了互补型MOS反相器(即CMOS器件)[10],其结构和电路如图3.36所示。CMOS由一对NMOS/PMOS组成,静态时,NMOS和 PMOS只有其中一个导通,另一个处于截止状态,所以,它的静态功耗极低。另外,CMOS输出电平对NMOS/PMOS器件的宽长比没有依赖关系,所以,它又可称为无比电路,低电平可接近于0V.高电平接近于电源电压,输出电平无损失。这种不依赖于器件宽长比的无比电路对于器件缩微和提高集成度是有利的。

由图3.36(b)可见,为保证CMOS反相器能有较高速度、导通管能工作在强反型区,要求电源电压V。>Vm+|Vnl。这样,CMOS反相器就可以得到如图3.37所示的电压传输特性和电流传输特性

当0

为分析简便起见,假设NMOS和PMOS具有对称的阈值电压和相同的跨导因子(当然具有不同的宽长比),即Vrp=一Vm和K,=K,这样转折点V"=Va/2,Ip达到最大。

当VT

CMOS集成电路的工作原理及其低功耗特性,可用图3.38进一步说明。该图显示,CMOS的瞬态功耗取决于信号传输和电平转换。图3.38中CL代表电路输出端的电容性负载,它通常由漏结电容、下一级栅极输入电容和输出信号线-衬底电容等构成。图3.38(a)说明输入信号由高电平("1")向低电平("0")跃变,引起的输出电平变化过程。漏极输出端由"o"向"1"的转换取决于负载电容CL的充电过程。此时,NMOS管由通态转向关态,而PMOS管由关态变为通态,恰好为负载电容CL提供充电电流。图3.38(b)则显示,当CMOS输人端电平由"0"向"1"转换时,进人导通态的NMOS管,为负载电容积累的电荷提供泄放通路。

由图3.37可知,当CMOS工作在静态时,其功耗是很低的。但当它工作在动态时,如输入信号为方波脉冲,则会有明显的功耗产生,这就是CMOS的动态功耗。CMOS的动态功耗可以这样来理解:在一个脉冲周期T内,共有CV』大小的电荷从电源流出,最终流到地,所以,可以认为在这个周期内,电源平均电流为C,V。/T=fC,Vs(f为CMOS工作频率),因而电源功耗应为fCLV%。在CMOS集成电路技术发展过程中,器件几何尺寸缩微及电源电压降低,使单元电路的动态功耗减小,电路的传输速度上升。但电路工作频率的提高会使其动态功耗增加。CMOS在工作时还需注意一个特别问题,即所谓的闩锁效应(L.atch-up)。本书第5章5.5节将讨论闩锁效应及其抑制方法。

-

三极管

+关注

关注

145文章

3727浏览量

128548 -

MOSFET

+关注

关注

151文章

10829浏览量

234997 -

半导体

+关注

关注

339文章

31273浏览量

266675 -

晶体管

+关注

关注

78文章

10443浏览量

148666

原文标题:MOS晶体管------硅基集成芯片制造工艺原理

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

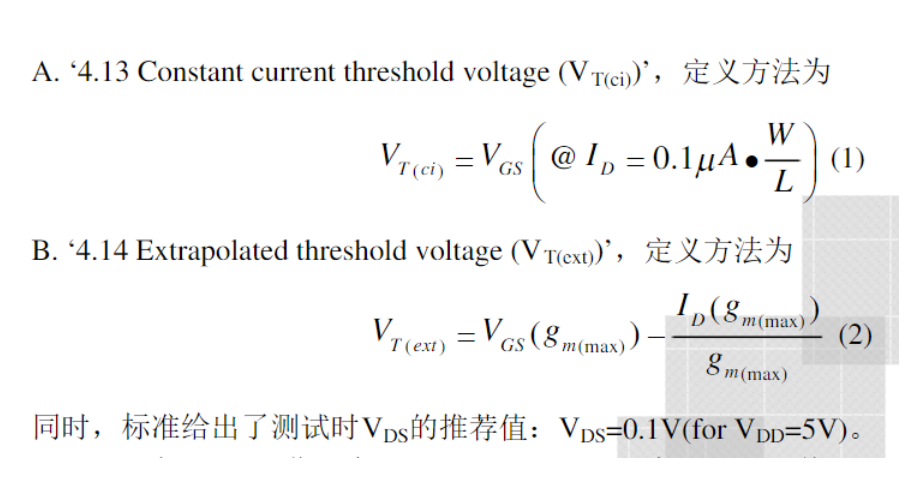

MOS管阈值电压的问题

MOS管阈值电压与沟长和沟宽的关系

NMOS晶体管的阈值电压公式 nmos晶体管的阈值电压与哪些因素有关

什么是MOS管亚阈值电压?MOSFET中的阈值电压是如何产生的?

浅谈影响MOSFET阈值电压的因素

MOSFET阈值电压是什么?影响MOSFET阈值电压的因素有哪些?

IBM与Rapidus在多阈值电压GAA晶体管技术的新突破

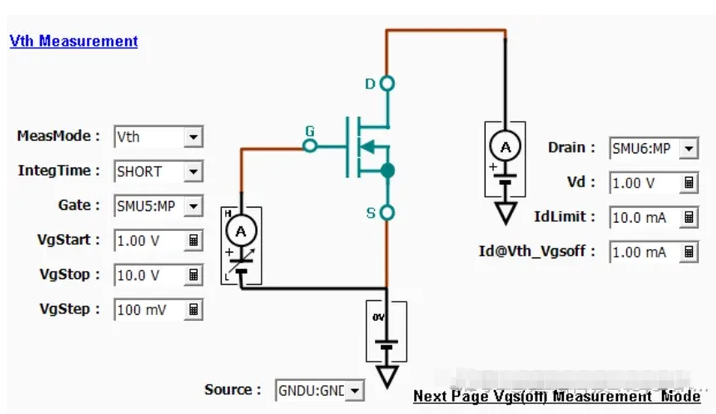

MOS管阈值电压的测量方法与优化实践

MOS晶体管的工作原理和阈值电压

MOS晶体管的工作原理和阈值电压

评论