本篇主要讨论Xilinx A7 FPGA的上电启动的时间分析··········加快从flash启动时间

在测试板卡时,发现FPGA板卡上电启动后,从flash读取配置信息的时间大约需要5、6秒的时间,这个时间个人感觉有点长了。

FPGA型号:XC7A35T-FGG484-2

Flash型号:n25q128

那为什么是5、6秒呢?

下面我们分析一波:

FPGA板卡上电启动后,需要从flash读取配置信息。

flash的接口为spi。

我们在利用vivado设计时,一般默认spi的模式为spix1,也就是一个时钟一根数据线传输一个bit。

那么我们一共需要从flash中读取出来多少bit呢?

从上述综合结果来看,大概是2141x1024x8个bit(注:配置文件的大小之和选择的芯片有关系,和设计的复杂度无关)。

那么从flash读取的时钟是多少频率呢?

我们在利用vivado设计时,一般默认为3MHz(这个不一定呦,和芯片也有一定的关系)。

如何查看这个默认时钟呢?

笔者使用软件为vivado 2019.2,(其他版本应该类似吧-----)。

打开下述的任何一个即可。

点击tools,选择edit device properties····

选择Configuration···················

可以看到默认的配置时钟的数据。

那么我们可以大概算一算了,bit文件的大小为:2141x1024x8个bit,利用3MHz的时钟读取,需要5.84秒左右(实际启动的时间要比这个长,需要包括上电延迟、模式检测、读取时间、配置等等,不过这个读取时间占据了主要比例)。

如果想着加快这段时间的话,我们可以通过加快这个配置时钟,来进行缩短这段时间。

笔者尝试将此时钟设置为6MHz。

上述改为6MHz后,点击ok。然后点击保存。xdc文件中会多一句话:

通过这句话来看,这个数字就是我们配置的时钟速率,后续设计时,如果需要更改此频率,可以直接在xdc中加入这句话,然后修改数字即可。

重新编译,生成配置文件,然后配置。

经过测试,重新上电后,时间大概3秒钟左右即可启动成功(时钟速率快了一半,时间也差不多缩小了一半)。

那我们设置为多少呢?觉得肯定是越高越好哈。那能不能写成100呢?

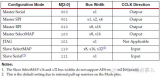

这个是不能的哈。我们来看看软件里面的值:

只能够设置为这个里面的值,不能自己随便写。

那么我们可以选择最大的那个(66MHz)吗?

答案是不一定能选择,这个去确定flash是否支持66MHz的读写速率,以及FPGA和flash之间的PCB连接线是否能够跑这个速率。

笔者的flash经过查看手册,可以看到读取的最大速率为54MHz。

结合一下,可以选择50MHz(可以尝试一下,需要看PCB连接线是否支持这个速率)。

经过测试,是可以使用的,启动的速度是可以的。

很多的“教程”中一般要求学习者,不论三七二一,先把这句话写入到xdc中,用于加速配置。

这个是不对的,不要养成习惯(下述实例为网络查询,笔者没有验证)。

当选择不同的芯片时,配置所支持的速率是不同的。

如果在xdc中依然写入50MHz的配置速率,那么就会出现无法匹配,进而使用默认最低速率配置。

关于配置的速率,在此告一段落。

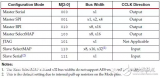

我们还可以通过配置spi的模式,来进行加快速率。有很多的flash是支持spix1、spix2、spix4(可以同时用多根线传输数据)的,另外也需要看flash与FPGA之间硬件连接是否支持。

通过查看硬件的链接方式,选择自己模式。在选择spix4时,如果选择的频率过高,并且pcb链接没有等长(线长差距较大时),可能会导致配置失败,可以酌情降低配置速率。

配置模式选择,然后点击OK即可。

xdc中就会多出下面这句话:

笔者经过测试,在笔者的板卡中,时间确实缩短了。

另外还有一种方式可以缩短这段时间,就是压缩配置文件。方式可以参考:

Xilinx的A7 FPGA板卡上电启动后,从flash读取配置信息的时间太长····(一)

-

FPGA

+关注

关注

1663文章

22493浏览量

638953 -

接口

+关注

关注

33文章

9588浏览量

157595 -

Xilinx

+关注

关注

73文章

2205浏览量

131825

原文标题:Xilinx A7 FPGA的上电启动的时间分析···加快从flash启动时间

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

cmos的slvs-ec协议40针引脚该如何连接到xilinx a7开发版上?

请问HMC8413的上电启动时间大概为多少?

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

xilinx A7 200t PCI协议使用问题

为xilinx a7生成.mcs,无法编程为a7

如何在a7 fpga中实现回退多重启动

Linux系统启动时间优化方案

Xilinx FPGA的快速启动配置

台积电20nm制程获将用于苹果A7试产

Xilinx7系列基于PCIe的设计如何满足PCIe启动时间的要求

不同场景的FPGA外围电路的上电时序分析与设计

索尼a7现在还值得买吗_索尼a7的报价_参数_图片_评论分析

基于FPGA的PCIe设备如何才能满足PCIe设备的启动时间的要求?

Xilinx A7 FPGA的上电启动时间分析

Xilinx A7 FPGA的上电启动时间分析

评论