MAXIM DS1243Y:64K NV SRAM 与幻影时钟的完美结合

在电子设计领域,非易失性静态随机存取存储器(NV SRAM)和实时时钟(RTC)是两个非常重要的组件。今天,我们要介绍的是 Maxim 公司的 DS1243Y,一款集成了 64K NV SRAM 和幻影时钟功能的芯片,它为电子设备提供了可靠的数据存储和精确的时间记录解决方案。

文件下载:DS1243.pdf

1. 产品特性

1.1 实时时钟功能

DS1243Y 的实时时钟能够精确跟踪百分之一秒、秒、分钟、小时、天、日期、月份和年份等信息。它还具备自动闰年补偿功能,有效期至 2100 年,确保时间记录的准确性。

1.2 64K NV SRAM

该芯片拥有 8K x 8 的 NV SRAM,可直接替代易失性静态 RAM 或 EEPROM。嵌入式锂能源电池能够维持日历操作并保留 RAM 数据,即使在断电的情况下,数据也能保存超过 10 年。

1.3 其他特性

- 标准 28 引脚 JEDEC 引脚排列,方便与其他电路集成。

- 全 ±10% 的工作范围,适应不同的电源电压。

- 在 +25°C 时,时钟精度优于 ±1 分钟/月。

- 锂能源电池在首次通电前处于电气断开状态,以保持其新鲜度。

2. 订购信息

DS1243Y 有多种封装可供选择,其中 DS1243Y - 120+ 适用于 0°C 至 +70°C 的温度范围,采用 28 引脚 EDIP(0.720a)封装,“+” 表示该封装为无铅/RoHS 兼容封装。

3. 引脚配置与描述

3.1 引脚配置

DS1243Y 的引脚配置采用标准的 28 引脚 JEDEC 引脚排列,包括复位输入(RST)、地址输入(A0 - A12)、数据输入/输出(DQ0 - DQ7)、芯片使能(CE)、输出使能(OE)、写使能(WE)等引脚。

3.2 引脚描述

每个引脚都有其特定的功能,例如:

- RST:低电平有效复位输入,内部有上拉电阻连接到 VCC。

- CE:低电平有效芯片使能输入,用于选择芯片。

- OE:低电平有效输出使能输入,控制数据输出。

- WE:低电平有效写使能输入,用于写入数据。

4. 工作模式

4.1 RAM 读模式

当写使能((overline{WE}))无效(高电平)且芯片使能((overline{CE}))有效(低电平)时,DS1243Y 执行读周期。13 个地址输入(A0 - A12)指定要访问的 8192 字节数据中的哪一个。在最后一个地址输入信号稳定后的 (t_{ACC})(访问时间)内,有效数据将出现在八个数据输出驱动器上。

4.2 RAM 写模式

当地址输入稳定后,(overline{WE}) 和 (overline{CE}) 信号处于有效(低电平)状态时,DS1243Y 进入写模式。写周期由 (overline{CE}) 或 (overline{WE}) 的后一个下降沿开始,由 (overline{CE}) 或 (overline{WE}) 的前一个上升沿结束。在写周期内,所有地址输入必须保持有效。

4.3 数据保留模式

DS1243Y 在 (V{CC}) 大于 (V{TP}) 时提供完整的功能,并在 4.25V 时进行写保护。在没有 (V{CC}) 的情况下,无需额外的支持电路即可保持数据。当电源电压下降时,RAM 会自动进行写保护,所有输入变为 “无关” 状态,所有输出为高阻抗。当 (V{CC}) 降至约 3.0V 以下时,电源切换电路将锂能源电池连接到 RAM 以保留数据;当 (V{CC}) 上升到约 3.0V 以上时,电源切换电路将外部 (V{CC}) 连接到 RAM 并断开锂能源电池。当 (V_{CC}) 超过 4.5V 时,RAM 可恢复正常操作。

5. 幻影时钟操作

5.1 模式识别

与幻影时钟的通信通过对 64 位串行位流的模式识别来建立。必须执行 64 个连续的写周期,在 DQ0 上提供正确的数据,以匹配该模式。在识别 64 位模式之前的所有访问都指向内存。

5.2 数据传输

识别成功后,接下来的 64 个读或写周期将提取或更新幻影时钟中的数据,同时禁止内存访问。数据传输由芯片使能((overline{CE}))、输出使能((overline{OE}))和写使能((overline{WE}))控制。

5.3 寄存器信息

幻影时钟信息包含在 8 个 8 位寄存器中,每个寄存器在 64 位模式识别序列完成后按顺序逐位访问。更新幻影时钟寄存器时,每个寄存器必须以 8 位为一组进行处理,否则可能会产生错误结果。

6. 电气特性

6.1 绝对最大额定值

DS1243Y 的绝对最大额定值包括引脚电压范围、工作温度范围、存储温度范围和引脚焊接温度等。在使用时,必须确保不超过这些额定值,以避免损坏芯片。

6.2 推荐工作条件

推荐的工作条件包括电源电压、输入逻辑电平、直流电气特性和交流电气特性等。在这些条件下,芯片能够正常工作并保证性能。

6.3 电容特性

芯片的输入电容和输入/输出电容在 (T_{A}= +25^{circ}C) 时的典型值为 5 - 10 pF。

7. 应用注意事项

7.1 焊接与清洗

DS1243Y 可以通过传统的波峰焊技术进行焊接,但要确保锂能源电池的温度不超过 +85°C。焊接后可以使用水洗技术进行清洗,但应避免使用超声波振动。

7.2 电池备份

在电池备份模式下,严禁出现任何幅度的负下冲。

总结

MAXIM DS1243Y 是一款功能强大的芯片,它集成了 64K NV SRAM 和幻影时钟功能,为电子设备提供了可靠的数据存储和精确的时间记录解决方案。在实际应用中,我们需要根据其电气特性和应用注意事项进行合理设计,以确保芯片的正常工作和性能。你在使用类似芯片时遇到过哪些问题呢?欢迎在评论区分享你的经验。

-

幻影时钟

+关注

关注

0文章

4浏览量

5639

发布评论请先 登录

NXP K64F 微控制器:低功耗与高性能的完美结合

Z8 Encore! XP 64K 系列闪存微控制器产品详解

Z8 Encore! XP 64K系列闪存微控制器:高性能8位解决方案

深入剖析DS1556:1M非易失性Y2K兼容计时RAM

深入解析DS1501/DS1511:Y2K兼容的看门狗实时时钟

深入解析DS1554:256k非易失性Y2K兼容计时RAM

深入解析DS1557:功能强大的非易失性计时RAM

深入剖析DS1340:I2C实时时钟与涓流充电器的完美结合

深入解析DS1338:一款功能强大的I2C实时时钟芯片

探索DS1248/DS1248P 1024K NV SRAM:集实时时钟与非易失存储于一体

深度解析DS1244/DS1244P:256K NV SRAM与幻影时钟的完美融合

ST25DV04K/16K/64K:动态NFC/RFID标签IC的深度剖析

探索DS1312:非易失性控制器与锂电池监测的完美结合

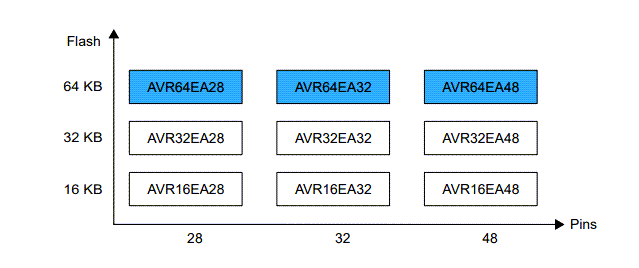

AVR64EA微控制器:高性能与灵活性的完美结合

MAXIM DS1243Y:64K NV SRAM 与幻影时钟的完美结合

MAXIM DS1243Y:64K NV SRAM 与幻影时钟的完美结合

评论