DS1094L:多相扩频经济振荡器的技术解析与应用指南

在电子设计领域,时钟发生器的性能对于系统的稳定性和电磁兼容性至关重要。DS1094L作为一款多相扩频经济振荡器,为开关模式电源等应用提供了出色的解决方案。本文将深入剖析DS1094L的特性、工作原理、电气参数以及应用要点,帮助电子工程师更好地理解和应用这款产品。

文件下载:DS1094L.pdf

一、DS1094L概述

DS1094L是一款硅振荡器,可产生四个多相、扩频方波输出。其输出频率范围为2MHz至31.25kHz,支持两相、三相或四相模式。通过对内部主振荡器进行0%、2%、4%或8%的抖动处理,能够显著降低系统级的电磁干扰(EMI)辐射。该产品非常适合作为开关模式电源的时钟发生器,其输出可用于DC - DC电路,实现电压的高效升降转换。

二、主要特性

2.1 多相输出

支持两相、三相或四相输出,满足不同应用场景的需求。

2.2 频率可编程

输出频率可在2MHz至31.25kHz之间进行编程,灵活性高。

2.3 扩频抖动

抖动输出可有效降低EMI辐射,提高系统的电磁兼容性。

2.4 无需外部定时组件

内部集成了必要的定时功能,简化了设计。

2.5 非易失性配置

配置设置具有非易失性,断电后数据不丢失。

2.6 可编程选项

支持用户编程和工厂预编程两种方式。

2.7 宽工作温度范围

工作温度范围为 - 40°C至 + 85°C,适用于各种恶劣环境。

三、电气参数

3.1 直流电气特性

- 电源电压(VCC):3.0V至3.6V。

- 输入逻辑电平:输入逻辑1(SDA、SCL)为0.7 x VCC至VCC + 0.3V;输入逻辑0(SDA、SCL)为 - 0.3V至0.3 x VCC。

- 输出电压:高电平输出电压(OUT1 - 4)在IOH = - 4mA、VCC = min时为2.4V;低电平输出电压(OUT1 - 4)在IOL = 3.5mA时为0.4V。

3.2 交流电气特性

- 主振荡器频率(fMOSC):1MHz至2MHz。

- 输出频率容差(∆fOUT):在VCC = 3.3V、TA = + 25°C时为 - 2.5%至 + 2.5%。

- 电压频率变化(∆fOUT):在TA = + 25°C时为 - 0.5%至 + 0.5%。

- 温度频率变化(∆fOUT):在VCC = 3.3V时,0°C至 + 70°C为 - 1.1%至 + 1.1%, - 40°C至 + 85°C为 - 2.5%至 + 1.1%。

四、工作原理

4.1 主振荡器

主振荡器负责产生输出的时序和频率,其频率fMOSC可在1MHz至2MHz之间以100kHz的步长进行编程。通过DAC寄存器进行编程,公式为fMOSC = 1MHz + (DAC值 x 100kHz),DAC值范围为0至10(十进制)。

4.2 预分频器

预分频器将主振荡器频率fMOSC除以1、2、4或8,得到输出频率fOSC,计算公式为fOSC = fMOSC / 2^PRESCALER,其中PRESCALER取值为0至3。

4.3 相位发生器

四个振荡器输出(OUT1至OUT4)可配置为两相、三相或四相模式,通过PRESCALER寄存器中的Ph1和Ph0位进行选择。

4.4 三角波发生器

用于对主振荡器频率进行抖动处理,增加扩频功能。抖动量和抖动频率均可编程,分别由PRESCALER寄存器中的J1、J0和D1、D0位控制。

五、2 - 线串行接口

DS1094L通过2 - 线串行接口进行编程,包括SDA(数据输入/输出)和SCL(时钟输入)。该接口支持读写控制寄存器,默认从地址为B0h,可通过ADDR寄存器中的3个地址位(A2、A1、A0)进行更改,最多允许8个DS1094L共享同一2 - 线总线。

5.1 数据传输定义

- 主设备:控制总线上的从设备,产生SCL时钟脉冲、起始和停止条件。

- 从设备:根据主设备的请求发送和接收数据。

- 总线空闲:SDA和SCL均处于高电平的状态。

- 起始条件:SDA从高电平变为低电平,同时SCL保持高电平。

- 停止条件:SDA从低电平变为高电平,同时SCL保持高电平。

- 重复起始条件:用于连续数据传输。

- 位写入:SDA在SCL低电平时进行数据转换,数据在SCL高电平期间保持有效。

- 位读取:主设备在读取位之前需释放SDA总线。

- 确认(ACK和NACK):第9位用于确认数据传输。

5.2 通信流程

- 单字节写入:主设备生成起始条件,写入从地址字节(R/W = 0)、内存地址、数据字节,最后生成停止条件,并读取从设备的确认信息。

- 单字节读取:使用虚拟写入周期,主设备生成起始条件,写入从地址字节(R/W = 0)、要读取的寄存器内存地址,生成重复起始条件,写入从地址字节(R/W = 1),读取寄存器并发送NACK,最后生成停止条件。

六、应用要点

6.1 SDA和SCL上拉电阻

SDA为开漏输出,需要上拉电阻来实现高逻辑电平。SCL可使用开漏输出加电阻或CMOS输出驱动器。上拉电阻值应确保上升和下降时间符合交流电气特性要求。

6.2 独立运行

如果DS1094L独立运行(无2 - 线主设备),SDA和SCL不应悬空,建议使用上拉电阻,以防止引脚浮动到未知电压。

6.3 电源去耦

为了获得最佳性能,建议在IC电源引脚使用去耦电容,典型值为0.01µF和0.1µF,应选择高质量的陶瓷表面贴装电容,并尽量靠近IC的VCC和GND引脚安装,以减小引线电感。

七、总结

DS1094L作为一款高性能的多相扩频经济振荡器,具有丰富的功能和良好的电气性能。其可编程的输出频率、多相输出模式以及扩频抖动功能,使其在开关模式电源等应用中具有显著优势。电子工程师在设计过程中,应充分了解其工作原理和电气参数,合理选择上拉电阻和去耦电容,以确保系统的稳定性和可靠性。在实际应用中,你是否遇到过类似振荡器的使用问题?又是如何解决的呢?欢迎在评论区分享你的经验。

-

开关模式电源

+关注

关注

1文章

81浏览量

10153

发布评论请先 登录

聚焦LTC6909:多相硅振荡器的技术解析与应用探索

探索LTC6902多相振荡器:特性、原理与应用全解析

DS1099低频率双输出经济型振荡器:设计与应用全解析

低功耗DS1090:低频率扩频经济振荡器的详细解析

探索DS1080L:低抖动扩频晶体倍增器的卓越性能

深入解析DS32kHz:高精度温度补偿晶体振荡器

高性能超低抖动振荡器LMK61XX:技术解析与设计指南

高性能超低抖动振荡器LMK61XX:技术解析与应用指南

高性能超低抖动振荡器LMK61XX:技术解析与设计指南

LMK62XX高性能低抖动振荡器:技术解析与应用指南

CDC6Cx-Q1低功耗LVCMOS输出BAW振荡器:技术解析与应用指南

汽车时钟MC - K系列时钟振荡器:设计与应用指南

CD4098B:高性能CMOS双单稳态多谐振荡器的技术解析与应用指南

CD4098B:CMOS 双单稳态多谐振荡器的技术解析与应用指南

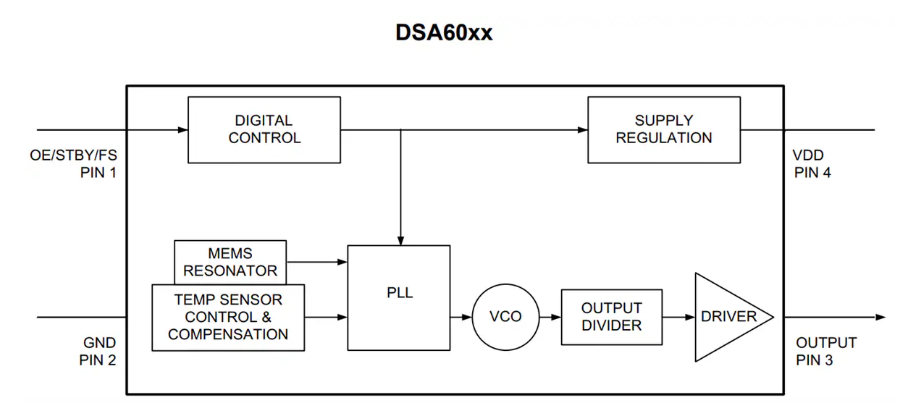

Microchip DSA60XX MEMS振荡器技术解析与应用指南

DS1094L:多相扩频经济振荡器的技术解析与应用指南

DS1094L:多相扩频经济振荡器的技术解析与应用指南

评论