SM320VC5421-EP 定点数字信号处理器深度剖析

在当今数字化浪潮中,数字信号处理器(DSP)的性能和功能对各类电子设备的运行起着关键作用。SM320VC5421-EP 作为一款性能卓越的定点数字信号处理器,为我们带来了诸多创新特性和强大功能。下面,我们就来深入了解这款处理器。

文件下载:sm320vc5421-ep.pdf

一、处理器概述

1.1 核心特性

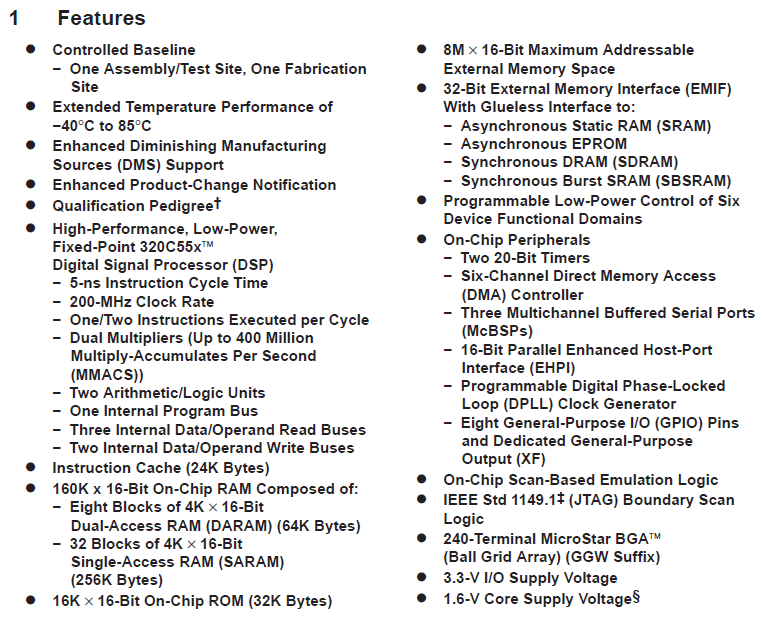

SM320VC5421-EP 具备诸多令人瞩目的特性。它采用受控基线,拥有单一的组装/测试地点和单一的制造地点,这确保了产品的质量稳定性。其工作温度范围为 -40°C 至 85°C,能适应较为恶劣的环境。同时,它还提供了增强的制造资源支持和产品变更通知资格认证,为长期使用提供了保障。

这款处理器是 200-MIPS 的双核 DSP,由两个独立的子系统组成。每个核心都拥有先进的多总线架构,包含三条独立的 16 位数据存储器总线和一条程序总线,能够高效地处理数据和指令。40 位算术逻辑单元(ALU)搭配 40 位桶形移位器和两个 40 位累加器,为复杂的算术运算提供了强大的支持。此外,它还具备 17 位×17 位并行乘法器和 40 位加法器,可实现单周期的乘法/累加(MAC)操作,大大提高了运算效率。

1.2 与 5420 的迁移

对于从 5420 迁移到 5421 的用户来说,需要注意一些变化。5421 的内存结构进行了调整,引入了 128K x 16 位的双向共享内存,增强了数据共享和处理能力。DMA 功能也得到了增强,能够访问外部和内部内存,并且 HPI 和 DMA 内存映射也进行了相应的更新。此外,5421 还增加了 2K x 16 位的 ROM 用于引导加载,VCO 引脚被 HOLDA 引脚取代,同时新增了 HOLD 引脚。McBSPs 也进行了更新,具备 128 通道选择能力,并且 CLKX/R 引脚可作为内部时钟速率发生器的输入,无需额外引脚。

二、功能模块详解

2.1 内存系统

2.1.1 各类内存类型

SM320VC5421-EP 的内存系统丰富多样。每个子系统都有 32K 16 位字的片上双访问 RAM(DARAM),可在每个机器周期内访问两次,既可以存储数据,也可以存储程序。片上单访问 RAM(SARAM)同样为 32K 16 位字,每个周期只能访问一次,主要用于存储数据。此外,还有 128K 16 位字的片上双向共享 DARAM,供两个 DSP 子系统共享,用于存储程序。每个子系统还有 2K 16 位字的片上 ROM,用于引导加载功能。

2.1.2 内存访问规则

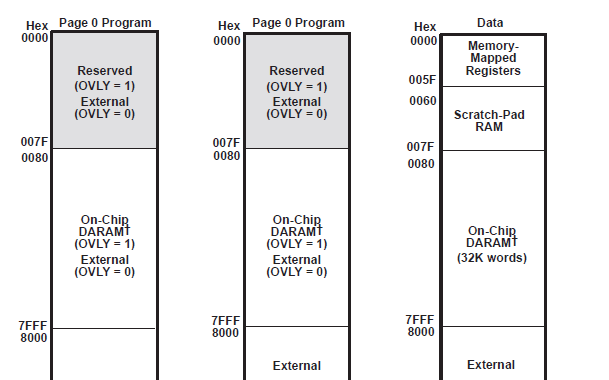

程序内存空间可寻址高达 512K 16 位字,采用分页扩展内存方案。访问程序内存时,不同页面和地址范围的访问规则不同,例如在低 32K 部分,取决于 OVLY 的状态;在高 32K 部分,取决于 MP/MC 和 XPC 的值。数据内存空间为单页 64K,低 32K 始终从本地 DARAM 访问,高 32K 则取决于 DROM 的状态。I/O 空间也是单页 64K,访问始终是外部的。

2.2 外设模块

2.2.1 软件可编程等待状态发生器

该发生器可将外部总线周期延长至最多 14 个机器周期,以适应较慢的片外内存和 I/O 设备。软件等待状态寄存器(SWWSR)控制其操作,可针对五个不同的地址范围插入不同数量的等待状态。软件等待状态控制寄存器(SWCR)中的软件等待状态乘数(SWSM)位可将等待状态数量乘以 1 或 2。

2.2.2 可编程银行切换

可编程银行切换可在跨越内存银行边界时自动插入一个周期,避免总线争用。银行切换控制寄存器(BSCR)定义了内存银行的大小,不同的位具有不同的功能,如确定外部内存银行大小、插入额外周期、发送处理器间中断等。

2.2.3 并行 I/O 端口

5421 拥有 64K 字的 I/O 端口地址空间,可通过 PORTR 和 PORTW 进行寻址。IS 信号指示通过 I/O 端口的读写访问,设备可通过 I/O 端口轻松与外部设备接口,同时所需的片外地址解码逻辑较少。SELA/B 引脚用于选择访问外部 I/O 空间的子系统。

2.2.4 16 位双向主机端口接口(HPI16)

HPI16 是 TMS320C54x DSP 8 位主机端口接口的增强版,允许 16 位主机访问 DSP 片上内存。它具有 16 位双向数据总线、多个数据选通和控制信号,支持多路复用和非多路复用地址/数据模式。在多路复用模式下,主机可通过 HD 双向数据总线访问 HPI16 数据寄存器、地址寄存器和控制寄存器;在非多路复用模式下,主机可通过 18 位 HA 地址总线和 16 位 HD 数据总线访问 HPI16 数据寄存器和地址寄存器。

2.2.5 多通道缓冲串行端口(McBSP)

5421 提供六个多通道缓冲串行端口(McBSPs),每个子系统有三个。McBSP 支持全双工通信,具有双缓冲数据寄存器,可实现连续数据流。它还具有独立的帧和时钟控制,可直接与多种设备接口,如 T1/E1 成帧器、MVIP 交换兼容设备等。此外,McBSP 支持多达 128 个通道的多通道收发,可选择多种数据大小,具备 µ 律和 A 律压缩功能,可编程帧同步和数据时钟极性,以及内部时钟和帧生成功能。

2.2.6 直接内存访问(DMA)控制器

5421 包含两个 6 通道的直接内存访问(DMA)控制器,每个子系统一个。DMA 控制器可独立于 CPU 进行数据传输,控制对片外程序/数据/IO 和内部数据/程序内存的访问。它具有六个通道,每个通道可独立编程优先级,支持 32 位内部访问和 16 位外部访问。DMA 控制器的同步事件可通过 DSYN 位字段选择,中断选择可通过 INTSEL 位字段进行。此外,DMA 还支持自动初始化模式,可通过全局重载寄存器实现连续和重复操作。

2.3 时钟与定时器

2.3.1 软件可编程锁相环(PLL)

时钟发生器由锁相环(PLL)电路组成,需要外部时钟源提供参考时钟。PLL 可将参考时钟频率乘以一个比例因子来生成设备时钟,也可将参考时钟除以 2 或 4。软件可编程 PLL 具有高度灵活性,可通过 16 位内存映射的时钟模式寄存器(CLKMD)进行控制,包括 PLL 乘数、分频器、计数器等设置。

2.3.2 硬件定时器

54x 设备具有 16 位定时电路和 4 位预分频器。定时器计数器在每个 CLKOUT 周期减 1,当计数器减到 0 时,会产生定时器中断。定时器可通过特定状态位停止、重启、重置或禁用,当 TOUT 位在通用 I/O 控制寄存器中设置为 1 时,定时器输出脉冲将驱动在 GPIO3 上。

三、电气特性与时序

3.1 电气规格

SM320VC5421-EP 的绝对最大额定值规定了其在不同条件下的工作范围,如电源电压、存储温度等。推荐的工作条件包括设备的电源电压、输入输出电压、电流等参数。电气特性则描述了在推荐工作条件下的输出电压、输入电流、电源电流等性能指标。

3.2 时钟选项

处理器支持多种时钟选项,包括将参考时钟除以 2 或 4 来生成内部机器周期,以及通过 PLL 将参考时钟乘以 N 来生成内部机器周期。不同时钟选项有相应的时序要求和开关特性。

3.3 接口时序

外部内存接口、并行 I/O 接口、HPI 接口等都有各自的时序要求和开关特性。例如,内存读写操作的访问时间、设置时间、保持时间等都有明确的规定,这些时序参数对于确保处理器与外部设备的正确通信至关重要。

四、总结与思考

SM320VC5421-EP 以其丰富的功能和卓越的性能,为电子工程师在设计各类数字信号处理系统时提供了强大的支持。其多核架构、多样化的内存系统和丰富的外设模块,使得它能够满足不同应用场景的需求。然而,在实际应用中,我们也需要根据具体需求合理配置处理器的各项参数,充分发挥其性能优势。同时,对于处理器的电气特性和时序要求,我们必须严格遵守,以确保系统的稳定性和可靠性。大家在使用这款处理器的过程中,是否也遇到过一些有趣的问题或者有独特的应用经验呢?欢迎在评论区分享交流。

-

数字信号处理器

+关注

关注

5文章

522浏览量

28490 -

功能模块

+关注

关注

0文章

25浏览量

2978

发布评论请先 登录

SM320VC5510AEP定点数字信号处理器的详细英文资料概述

SM320VC5421-EP 增强型产品定点数字信号处理器

SM320C6414-EP/SM320C6415-EP/SM320C6416-EP定点数字信号处理器数据表

SM320DM642-EP视频/图像定点数字信号处理器数据表

SM320VC5421-EP 定点数字信号处理器深度剖析

SM320VC5421-EP 定点数字信号处理器深度剖析

评论