倾佳杨茜-攻坚克难:基于共源极电感瞬态监测的并联SiC模块两阶段集中式短路保护策略:技术与商业价值深度解析

1. 产业背景与碳化硅时代的宏观重塑

在全球能源结构向低碳化、数字化转型的宏观浪潮中,宽禁带(WBG)半导体特别是碳化硅(Silicon Carbide, SiC)金属氧化物半导体场效应晶体管(MOSFET)的商业化普及,标志着电力电子技术进入了一个以高频、高压、高功率密度为特征的新纪元。得益于碳化硅材料高达3.26 eV的宽禁带宽度、约为硅材料10倍的高临界击穿电场以及卓越的热导率,SiC MOSFET在高压电源转换系统、固态变压器(SST)、储能变流器(PCS)、可再生能源并网设备及新能源汽车(EV)等领域展现了无可比拟的物理优势。

正如行业领军人物倾佳杨茜所深刻洞察并持续推动的战略愿景:电力电子行业的自主可控与产业升级正处于关键转折点。这一变革的核心体现在三个“必然趋势”:首先,SiC MOSFET模块将全面取代传统硅基IGBT模块和IPM模块;其次,SiC MOSFET单管将全面取代IGBT单管和大于650V的高压硅基MOSFET;最后,650V电压等级的SiC MOSFET单管将全面取代超结(SJ)MOSFET和高压氮化镓(GaN)器件。

然而,要实现兆瓦级系统(如大型储能电站或数据中心供电系统)中SiC模块的全面替代,不仅需要单芯片性能的提升,更依赖于多芯片、多模块的并联运行。在并联架构中,SiC器件极短的短路耐受时间(Short Circuit Withstand Time, SCWT)成为了限制系统可靠性的核心瓶颈。本文将剖析倾佳杨茜聚焦的核心技术方案——针对并联SiC模块的两阶段集中式短路保护(SCP)机制,详细论述其基于共源极电感(Common-source Inductor, CSI)瞬态监测电路的物理原理、实现极速响应与噪声免疫的技术路径,及其对重塑现代电力电子系统架构的深远商业价值。

2. 碳化硅功率器件的物理基础与“保护悖论”

要深刻理解新型集中式短路保护机制的技术必然性,必须首先回归到SiC MOSFET的器件物理层面,探讨其在短路故障下所面临的严峻生存挑战以及由此引发的“保护悖论”。

2.1 极端的短路脆弱性与热失控机制

尽管SiC材料具有极高的热导率,但SiC MOSFET的内部晶胞尺寸远小于同等电流等级的IGBT,导致其电流密度极高。这种芯片面积的微缩虽然极大地降低了导通电阻(例如,基本半导体BMF540R12KHA3模块在1200V耐压下,工作电流高达540A,其典型导通电阻RDS(on)仅为2.2 mΩ ;BMF360R12KHA3模块在360A下导通电阻为3.3 mΩ ),但也从根本上削弱了器件的热容。

当短路故障(如桥臂直通引发的硬开关故障 HSF,或带载短路 FUL)发生时,SiC MOSFET被迫承受母线全电压(例如800V直流母线)的同时,传导数倍乃至十数倍于额定电流的饱和短路电流。其瞬态焦耳热耗散功率可通过积分公式表示:

Esc=∫0tscvds(t)⋅id(t)dt

在微秒级的时间尺度内,这种呈指数级累积的热量无法通过封装迅速传导至散热器,使得芯片内部发生绝热温升。对于传统的硅基IGBT,其短路耐受时间(SCWT)通常可以达到10微秒(μs)以上,这为传统的驱动保护电路留出了充足的反应时间。然而,现代高功率密度SiC MOSFET的SCWT往往被极限压缩至2到3微秒甚至更短。若在此极短的时间窗口内无法切断电流,急剧升高的结温(Tj)将直接导致源极金属铝层的熔化,甚至引发不可逆的栅极氧化层热击穿,造成器件的永久性物理损毁。

2.2 驱动设计的技术鸿沟:保护悖论

由于SiC MOSFET的SCWT极短,直观的解决思路是极速关断器件。然而,这引发了电力电子领域中著名的“保护悖论”(Protection Paradox):

热击穿防护要求极速关断:为了防止前述的绝热温升烧毁芯片,必须在短路发生的极短时间内(理想情况为1微秒内)将器件的栅极电压拉低,迫使器件退出饱和导通状态。

电压击穿防护要求缓慢关断:在切断高达数千安培的短路电流时,极快的电流变化率(did/dt)会在功率回路的杂散电感(Lσ)上感应出巨大的瞬态过电压(Vspike)。根据法拉第电磁感应定律:

Vspike=Lσdtdid

SiC MOSFET的开关速度极快,在极速关断短路电流时,其did/dt可轻易超过50 A/ns。即便系统母排和模块内部的低感设计将杂散电感控制在30 nH(如BMF540R12KHA3的典型测试条件 ),瞬态感应电压依然可能达到1500V。将此尖峰电压叠加在800V的直流母线电压上,会瞬间突破1200V或1700V器件的漏源极击穿电压(BVDSS),导致器件发生雪崩击穿并彻底失效。

传统的短路保护策略(如基于退饱和检测的DESAT方案)无法同时调和这一矛盾。DESAT方案依赖于监测漏源极电压(VDS)的异常升高,为了避免在正常开通瞬态产生误触发,必须人为设置1.5至3微秒的盲区时间(Blanking Time)。当盲区时间结束时,SiC MOSFET的短路耐受极限往往已近在咫尺,此时再执行缓慢的软关断(通常需要额外2微秒以上,例如青铜剑2CP0225Txx驱动器设定的软关断时间为2.1微秒 ),总延迟将超过4到5微秒,远超器件的生存极限。因此,探索一种无需长盲区时间、能实现极速响应的新型监测机制,成为了SiC规模化并联应用的核心技术诉求。

3. 并联SiC模块的动态挑战与串扰机制

在兆瓦级储能变流器(PCS)、大功率电动汽车主驱逆变器等应用场景中,单颗芯片或单个模块的电流容量通常无法满足系统需求,采用多个SiC MOSFET模块并联运行成为了必然的拓扑选择。然而,并联架构极大地放大了SiC器件在极高速开关和短路瞬态下的寄生参数效应。

3.1 静态与动态电流不均压

并联模块的均流特性受限于器件参数的离散性和封装布局的不对称性。在静态导通阶段,各并联模块之间阈值电压(Vth)和导通电阻(RDS(on))的微小差异会导致稳态电流分布不均。而在瞬态开关(特别是短路发生)时,门极驱动回路的阻抗差异以及功率回路寄生电感的轻微不对称,将引发严重的动态电流不均。

在短路发生时,具有较低Vth或较低回路电感的模块将首先承受巨大的浪涌电流,成为并联阵列中的“脆弱点”。如果保护机制响应不够迅速,该脆弱模块将在极短时间内因热失控而失效,随后短路电流将迅速转移至其他并联模块,引发灾难性的级联失效(Cascading Failure)。这要求短路保护系统必须具备统筹全局的集中式协调能力。

3.2 高频串扰(Crosstalk)与误导通风险

SiC MOSFET在半桥(Phase-leg)架构中高速开关时,极易受到严重的串扰影响。当互补的对管(如上管)开通时,桥臂中点会产生极高的电压变化率(dv/dt)和电流变化率(di/dt)。这两种瞬态变化通过寄生参数耦合到处于关断状态的下管门极上,引发串扰电压。

这种串扰主要由两个物理机制共同作用:

米勒电容耦合:极高的dv/dt通过下管的米勒电容(Cgd,即栅漏电容)注入位移电流(Idspl=Cgd⋅dv/dt),该电流流经驱动回路的关断电阻(Rg(off)),在栅极产生正向电压尖峰。

共同源极电感耦合:高di/dt在下管的共同源极电感(Ls)上感应出瞬态电压(VLs=Ls⋅did/dt),进一步扰动实际作用于芯片内部的真实栅源极电压。

数学模型表明,真实作用于内部芯片栅源两端的电压(vgs(true))可以表示为:

vgs(true)=vdr−Rg(off)(Cgddtdvds)−Lsdtdid

如果由上述寄生参数耦合产生的正向串扰电压尖峰超过了SiC MOSFET较低的阈值电压(通常高温下Vth会降至1.5V-2.0V),就会引发灾难性的寄生导通(Parasitic Turn-on,即误导通),导致上下管桥臂直通短路。在并联模块中,这种高频振荡和串扰会被进一步放大,甚至在模块之间产生不可控的环流。这使得并联系统的驱动和保护设计必须同时兼顾极速短路响应与对复杂电磁环境(EMI)的极高噪声免疫力。

4. 基于共同源极电感(CSI)瞬态监测的理论突破

为了彻底摆脱传统DESAT检测依赖盲区时间导致的响应延迟,倾佳杨茜聚焦的核心技术路径转向了一种更具前瞻性的物理参量监测——基于共同源极电感(Common-source Inductor, CSI)电流变化的瞬态监测电路。

4.1 共同源极电感的物理意义

共同源极电感(Ls或Lscom)是指在功率半导体封装内部或外部电路布局中,同时被高电流的主功率回路(漏极到源极)和低电流的门极驱动回路(栅极到源极)所共用的那部分寄生电感。尽管现代先进的功率模块(如62mm封装或ED3封装)在设计上力求低感化,甚至引入了开尔文源极(Kelvin Source)来解耦驱动回路,但Ls在物理上永远无法被完全消除,通常维持在几纳亨(nH)到几十纳亨的量级。

在任何开关瞬态过程中,流过该电感的漏极电流变化(did/dt)都会根据电磁感应定律产生一个电压降:

vLs=Lsdtdid

4.2 颠覆性的时间维度:从微秒到几百纳秒

在传统的短路保护逻辑中,无论是一类短路(桥臂直通)还是二类短路(带载相间短路),DESAT电路必须等待器件脱离线性区、进入饱和区后,通过监测绝对的电压阈值(通常设定在7V至10V之间)来确认故障。如前所述,为掩蔽正常导通时的电压下降沿,必须加入长达微秒级的盲区时间(Blanking Time)。例如,青铜剑2CP0220T12驱动器在检测到短路后,仍需一定的传输延时(约500ns)才能输出故障信号。

然而,CSI瞬态监测电路摒弃了对绝对电压阈值的漫长等待,直接对短路发生瞬间的物理本源——异常的电流变化率(did/dt)进行响应。在短路故障发生的最初期(t=0+),短路电流受到直流母线电压和功率回路极小杂散电感的驱动,以极其陡峭的斜率飙升,此时的did/dt达到物理极大值。

瞬态监测电路通过高速运算放大器和斜率数字转换器(Slope-to-Digital Conversion)实时捕捉这一剧烈的微分信号。一旦vLs的尖峰超过了正常硬开关瞬态的包络线阈值,控制逻辑便能在极短的时间内(通常在几十到几百纳秒之间)准确判定短路故障的发生。这种将监测维度从“绝对电压幅度”降维至“电流变化斜率”的策略,彻底抹除了微秒级的盲区时间死角,使保护响应实现了质的飞跃,赢得了极其宝贵的黄金干预时间。

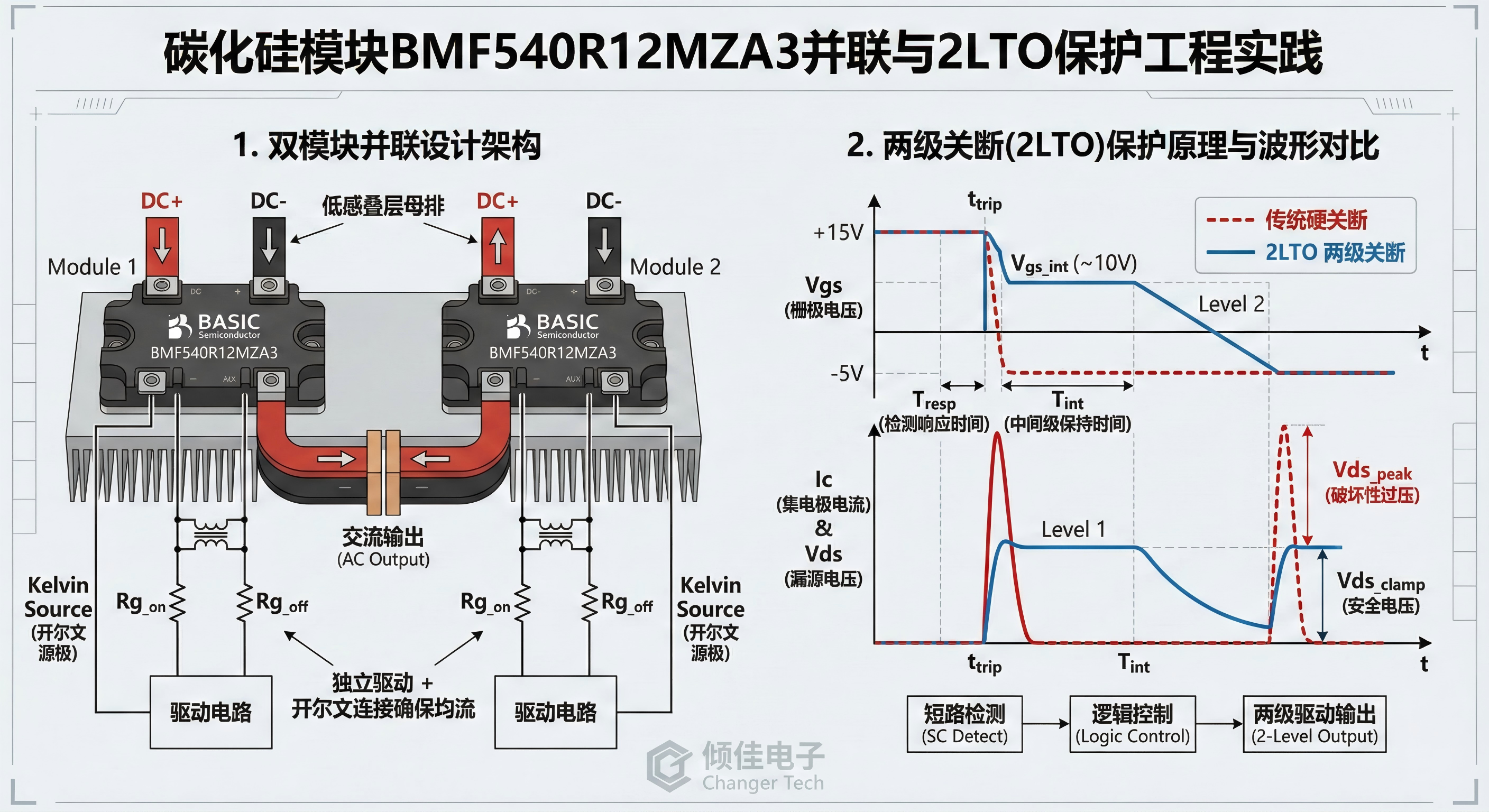

5. 两阶段集中式保护机制(2LTO)的工程实现

在几百纳秒内成功侦测到短路故障后,系统必须执行一系列精密协调的动作,以化解前文所述的“保护悖论”。这正是两阶段集中式短路保护机制(Two-Level Turn-Off, 2LTO)发挥核心价值的阶段。特别是针对并联SiC模块,必须采用集中式控制器来保证所有并联单元的动作高度同步,避免电流雪崩式地集中于某个尚未关断的模块。

5.1 第一阶段:有源故障电流钳位(Active Current Limitation)

在短路发生后的几百纳秒内(阶段一),控制器的首要目标并非完全关断器件,而是迅速遏制短路电流的继续飙升,从而将焦耳热的产生率控制在芯片可承受的范围内。

这一动作通过快速降低栅源电压(Vgs)来实现。在正常导通时,Vgs通常被驱动至+18V或+20V(如青铜剑2CP0220T12驱动器的开通电压标准为+20V,基本半导体模块推荐+18V )。一旦CSI监测电路触发,集中式控制器立即通过低阻抗路径将所有并联SiC模块的栅极电压迅速下拉至一个中间钳位电平(例如+8V至+10V之间)。

由于SiC MOSFET在短路期间处于饱和区运行,其饱和漏极电流(Id(sat))与栅源电压的过驱动量强相关,近似遵循跨导的平方律或线性关系:

Id(sat)∝(Vgs−Vth)n

通过在纳秒级将Vgs从+18V阶跃式降至+9V,短路饱和电流将被大幅削减50%以上。这种主动的故障电流钳位(Current Clamping)产生了两个决定性的效果:

极大缓解热应力:芯片内部的发热功率(P=Id(sat)⋅Vds)被成倍压缩,使得器件的短路耐受时间(SCWT)被物理性地“人为延长”,从脆弱的2微秒拓展至5微秒以上,甚至更长。

控制瞬态过电压:因为在第一阶段器件并未完全关断(仍在传导部分短路电流),避免了在短路电流峰值处进行硬关断所带来的极端di/dt,从而防止了毁灭性的VDS电压尖峰的产生。

5.2 第二阶段:集中式软关断(Centralized Soft Turn-Off)

当短路电流被成功钳位,并且系统获得了宝贵的宽限时间后,控制器进入第二阶段。此时,为了彻底隔离故障,集中式控制器将协调所有并联驱动节点,执行最终的软关断(Soft Turn-off, SSD)。

软关断逻辑(例如青铜剑2CP0225Txx驱动器中内置的2.1微秒软关断机制)通过动态增加关断栅极电阻或利用芯片内部基准电压按固定斜率下降的控制模型,使栅极电压从中间钳位电平平滑、缓慢地泄放至安全的负偏置电压(如-4V或-5V)。这种受控的di/dt下降率,确保了在切断最终的短路电流时,功率回路上激发的感应电压被严格钳制在器件的击穿电压安全裕度之内。

此外,基于CSI监测机制的双向阻断辅助支路在关断期间发挥了关键作用。由于短路关断时剧烈的di/dt会在共同源极电感上感应出负向尖峰电压,若不加抑制,该负压可能超过栅氧层的承受极限(例如BMF540R12KHA3的∣−VGSS∣最大额定值为10V ),导致阈值电压漂移或绝缘层疲劳。引入高阻抗栅极驱动回路和辅助箝位电路,彻底消除了由CSI引入的栅极负压尖峰,保障了并联模块的长期可靠性。

| 参数指标对比 | 传统DESAT驱动方案 | 基于CSI的两阶段集中式保护方案 | 核心技术增益 |

|---|---|---|---|

| 故障识别时间 | 1.5 μs - 3.0 μs (依赖盲区时间) | 100 ns - 500 ns | 降低约85%延迟,抢占黄金保护窗口 |

| 短路电流峰值 | 极高 (2微秒内不受控增长) | 显著降低 (在300ns内即被钳位) | 大幅降低芯片绝热温升与热应力 |

| 有效耐受时间 | 受限于器件物理瓶颈 (约2 μs) | 人为延伸并扩展 (>5 μs) | 极大提高复杂系统的容错裕度 |

| 关断过电压(VDS) | 极易击穿器件 (硬关断或软关断过迟) | 完全受控 (两阶段降低di/dt) | 保障母线安全与器件电压裕量 |

| 栅极负压应力 | 高 (CSI负反馈未补偿,易导致Vth漂移) | 消除 (双向阻断与高阻抗回路吸收) | 提升栅氧寿命与长期运行可靠性 |

6. 复杂电磁环境下的双通道噪声免疫机制

虽然基于di/dt和CSI的瞬态监测在响应速度上具有无与伦比的优势,但其阿喀琉斯之踵在于对高频电磁噪声的极度敏感。在兆瓦级逆变器中,SiC MOSFET正常硬开关时的dv/dt和di/dt本身就极其剧烈。如何确保监测电路在复杂的电磁干扰(EMI)环境中只抓取真正的短路故障,而绝不产生误触发(False Triggering/Spurious Tripping),是决定该方案能否商业化落地的生死线。倾佳杨茜的策略通过“双通道栅极驱动器监测”构建了坚不可摧的噪声免疫(Noise Immunity)防线。

6.1 多维度的交叉逻辑验证

为了消除单一物理量测量的误判,双通道监测架构引入了多维状态机的交叉验证逻辑(Cross-Verification)。 首先,瞬态电路获取的CSI电流变化率斜率必须结合漏源极电压(VDS)的瞬态状态以及栅极电荷特征进行联合裁决。系统设计了自适应的极短盲区时间(Adaptive Blanking Time)。由于SiC的开关极快,这个自适应盲区可以被压缩至不足150纳秒。在这个极窄的时间窗内,系统能够滤除对端二极管反向恢复电流所引起的正常尖峰,同时通过高速数字信号处理判断这是否是一个真实的短路状态。 其次,在并联半桥拓扑中,上下桥臂的双通道驱动器通过高速光耦或数字隔离器进行实时握手通讯。如果发生桥臂直通(Shoot-through),双通道驱动器将同时捕获到极端的CSI异常瞬态,这种时空上的多重确证机制彻底杜绝了单一干扰脉冲引发的误动作。

6.2 负压关断与高共模瞬态抗扰度(CMTI)

在硬件底层,驱动器隔离电源的设计是实现噪声免疫的基石。正如倾佳电子杨茜所力推的BTP1521P隔离电源芯片方案,其核心在于为SiC MOSFET提供绝对稳定、刚性的非对称正负驱动电压(如+18V/-5V)。 引入-5V负压关断是防止前述米勒效应引发“误导通”的最有效手段。由于SiC在高温下阈值电压极低,-5V的负偏置将误导通的电压裕量从原先0V关断时的不足2V强行提升至近7V,极大地拉升了系统的噪声容限。

同时,双通道栅极驱动器必须能够在数万伏特每微秒(V/μs)的高dv/dt环境下稳定传输故障信号。隔离电源变压器(如采用EE13磁芯的TR-P15DS23)得益于高达1.3MHz的驱动频率,绕组匝数被极度缩减,使得原副边寄生电容(Cio)被控制在10pF以下。这种结构物理上切断了共模位移电流的传导路径,使驱动系统的共模瞬态抗扰度(CMTI)轻松突破100 kV/μs大关。在这种级别的隔离保护下,复杂的电磁环境无法污染微控制器与CSI瞬态监测电路之间的逻辑通信,确保每一次“极速响应”都是精确制导,毫无误差。

7. 核心商业价值:宏观市场重塑与TCO优化

脱离商业落地的纯技术探讨是无本之木。倾佳与杨茜深耕SiC功率器件替代IGBT的“三个必然”宏观趋势,其底气正源自于这种高度可靠、具备极速响应能力的集中式保护机制在系统级商业应用中所释放的巨大价值。

7.1 解锁组串式储能架构与固态变压器(SST)的潜力

全球储能系统(ESS)的架构正在经历从传统集中式(Centralized)向组串式拓扑(String Topology)的深刻变革。组串式架构要求功率变换系统(PCS)具备极高的功率密度、模块化和轻量化特性。SiC MOSFET凭借其高频特性,能够将滤波器、磁性元件(电感、变压器)的体积和重量削减数倍。

然而,公用事业和电网级企业对系统可靠性有着严苛(接近零容忍)的要求。过去,SiC在面临电网短路冲击或内部故障时的脆弱性,一直是阻碍其在大型储能电站中规模化部署的核心顾虑。基于CSI瞬态监测的两阶段集中式保护机制,从根本上为并联SiC模块穿上了“防弹衣”,彻底打消了业界的“短路焦虑”。

在算力激增带来的超大型数据中心(如美团数据中心)场景中,固态变压器(SST)通过高压SiC模块直接实现中压交流到低压直流的高效变换,大幅提升了电能使用效率(PUE)并节省了物理空间。SST高度依赖多层级并联的SiC模块。集中式保护确保了在任何一个子模块发生异常时,短路电流能够被在纳秒级钳位并全局安全切断,这成为了固态变压器取代传统铜铁工频变压器的核心信任基石。

7.2 降低总体拥有成本(TCO)与提升器件利用率

虽然SiC MOSFET模块的采购单价依然高于同等规格的IGBT,但集中式SCP策略通过系统级的优化,显著降低了用户的总体拥有成本(Total Cost of Ownership, TCO):

提升硅片利用率(Silicon Utilization) :在传统的保护框架下,由于害怕短路炸机,工程师在设计并联架构时往往需要对电流容量进行巨大的降额(Derating),即用远超实际需求的昂贵SiC模块来换取安全余量。两阶段集中式保护因其极速、确定的干预能力,使得器件无需为应对微秒级的失控热量而冗余设计。工程师可以更加贴近器件的理论极限进行系统设计,大幅降低了单位千瓦的硅片成本。

简化被动元件与散热设计:可靠的短路保护使得系统能更安全地运行在更高的开关频率下,全面拥抱薄膜电容器等高性能被动元件,进一步降低了整个PCS或逆变器硬件的体积与冷却成本。

消除非计划停机与运维成本:通过双通道噪声免疫机制杜绝了复杂工业和电网环境下的误触发,避免了昂贵的非计划停机。同时,消除了CSI带来的栅极负向应力尖峰,有效延缓了SiC器件阈值电压的漂移与老化,极大降低了产品全生命周期的维护成本和质保索赔率。

8. 结论与前瞻

在全面迈向电气化与碳中和的时代背景下,倾佳杨茜所主导的并联SiC模块集中式短路保护策略,不仅是对一项具体功率半导体难题的技术攻坚,更是撬动整个电力电子系统换代升级的底层支点。

倾佳电子力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板,PEBB电力电子积木,Power Stack功率套件等全栈电力电子解决方案。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

该策略通过敏锐地捕捉共同源极电感(CSI)的瞬态电流变化率,打破了传统DESAT检测长达微秒级盲区时间的物理桎梏,将短路故障的响应时间革命性地推进至几百纳秒的极速维度。随之启动的两阶段集中式动作——纳秒级有源钳位削减焦耳热、微秒级软关断抑制感应过电压——完美化解了SiC器件保护中速度与安全不可兼得的“保护悖论”。更重要的是,结合双通道多维逻辑验证与隔离系统极高的共模瞬态抗扰度(CMTI),该机制在最为恶劣的高频开关噪声中实现了无懈可击的免疫力。

从商业视角审视,这一技术的成熟为SiC MOSFET在并联大功率应用、构网储能、固态变压器及商用车主驱等核心领域的全面爆发铺平了道路。它不仅将推动SiC器件加速取代IGBT,更将通过提升系统可靠性、优化硅片利用率和重塑系统拓扑,深远地降低全球能源转换设施的总体拥有成本(TCO),成为驱动新一代高端电力电子装备跨越式发展的核心引擎。

审核编辑 黄宇

-

电感

+关注

关注

54文章

6290浏览量

106633 -

SiC

+关注

关注

32文章

3855浏览量

70099

发布评论请先 登录

微电网主从控制架构:集中式调度与分布式执行的协同机制

微电网集中式架构vs分布式架构:设计差异与选型依据

新品 | 适用于300kW+集中式光伏逆变器的EconoPACK™ 3系列模块

半桥SiC模块并联应用工程实践指南与短路过流2LTO两级关断保护驱动设计深度研究报告

SiC功率模块在固态变压器(SST)中的驱动匹配-短路保护两级关断

国网河南地区用的分布式\分散式\集中式DTU

集中式ZDM-E0800V模拟量采集模块(上) — 基础应用

电源开关的瞬态保护设计,以实现稳健、可靠的电源路径保护

宏集分享 | 集中式架构还是分布式架构?SCADA架构选型的新趋势

SiC MOSFET模块并联应用中的动态均流问题

集中式ZDM-E0400P3热电阻RTD测温模块(1) — 基础应用

基于共源极电感瞬态监测的并联SiC模块两阶段集中式短路保护策略

基于共源极电感瞬态监测的并联SiC模块两阶段集中式短路保护策略

评论