本章以太网通信实验是基于ZYNQ-MZ702P开发板进行实现,在配置方面,需要读者自主修改不同的地方。文章末尾有本项目原工程压缩包,提供参考。

下面直接进行操作。

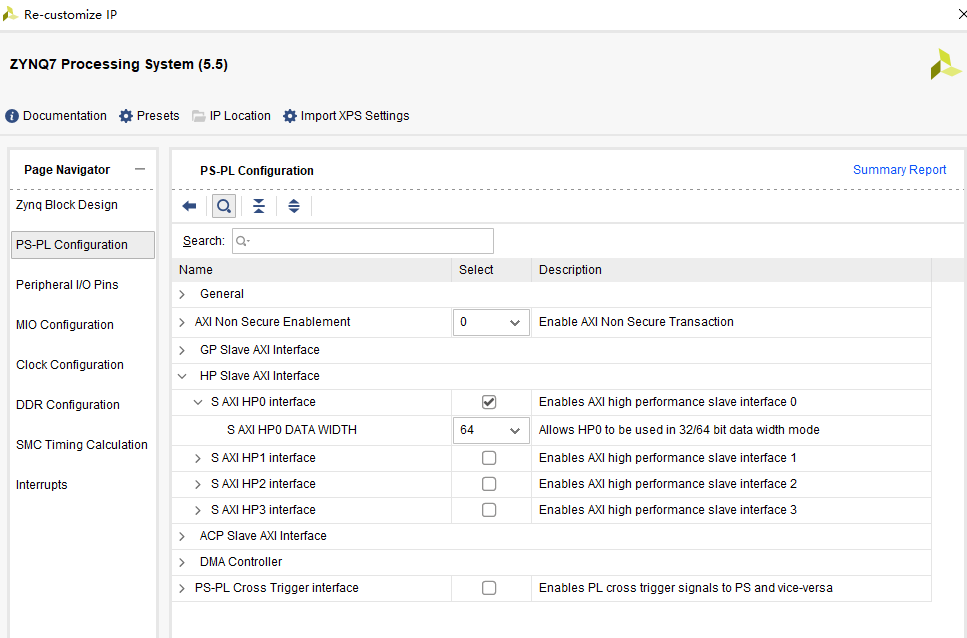

1.打开vivado,选择好开发板芯片后,新建完成工程,点击open block design,再点击右边Diagram框图中的加号添加zynq再进行相关配置。

配置输出时钟。

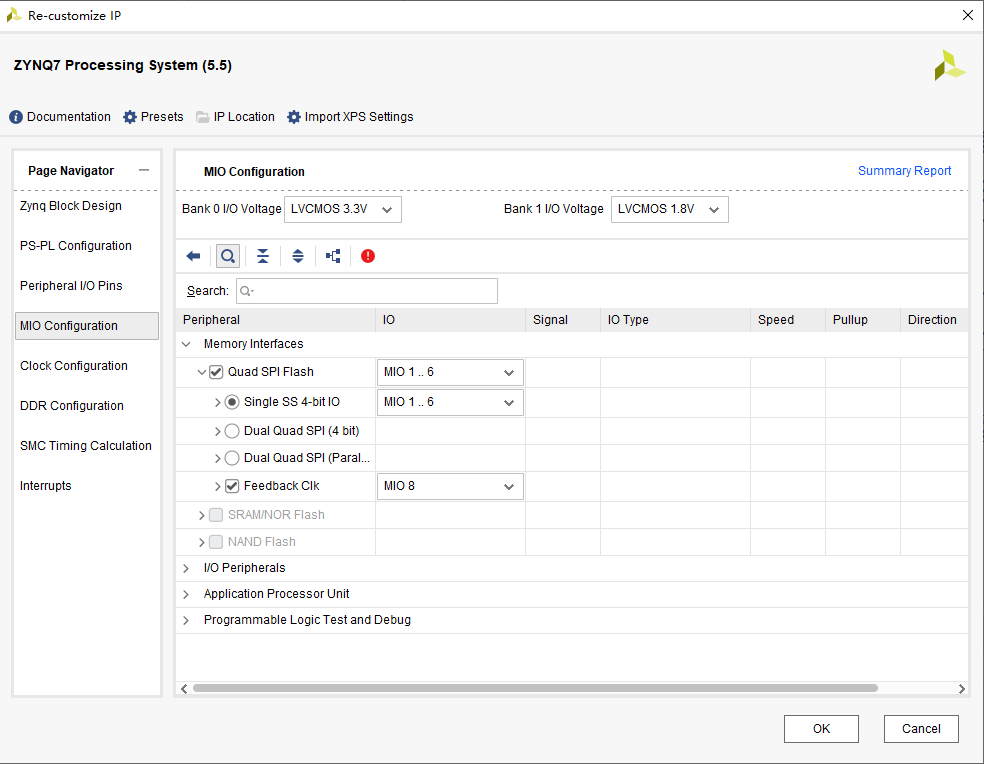

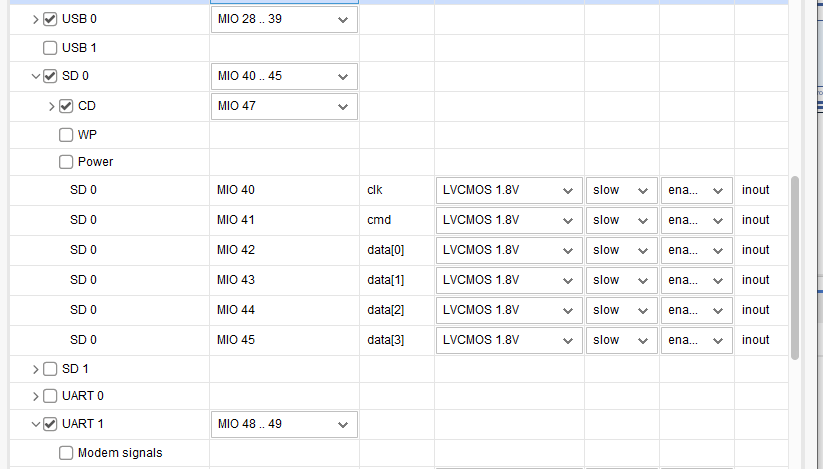

下面根据个人使用的开发板进行配置。

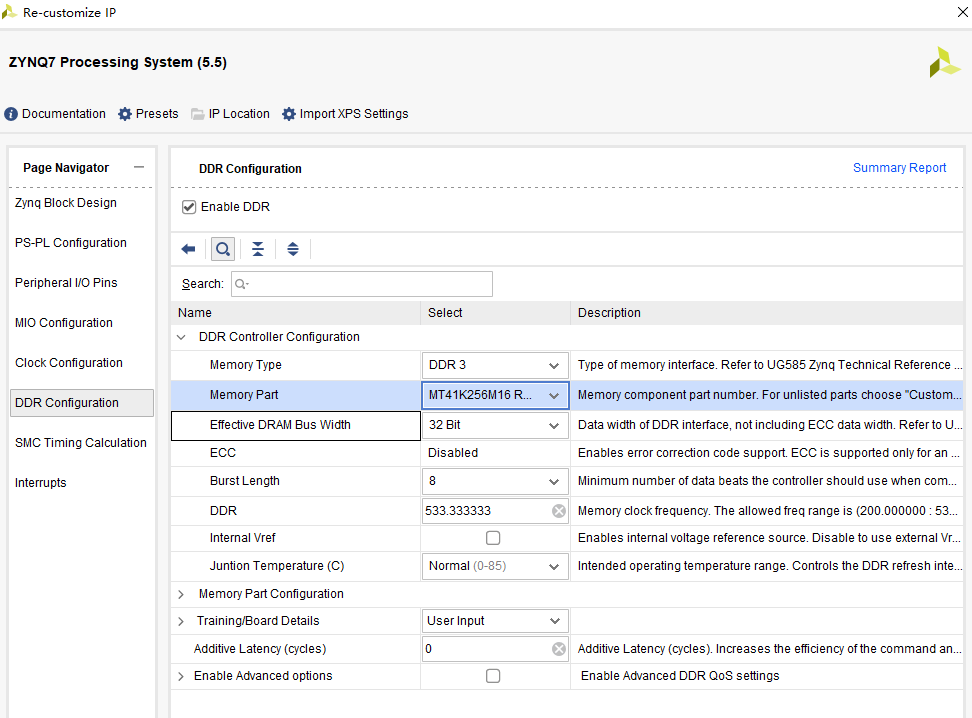

选择DDR型号。

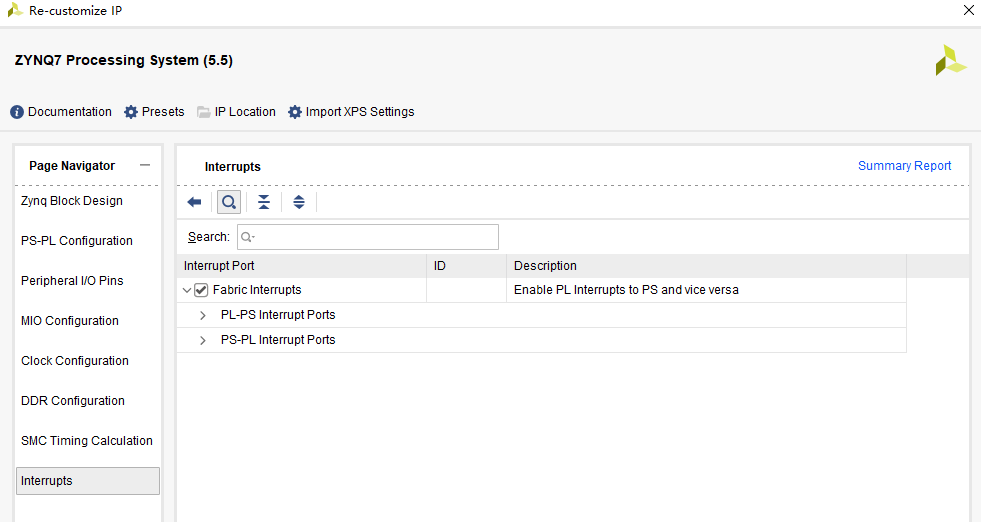

开启中断。

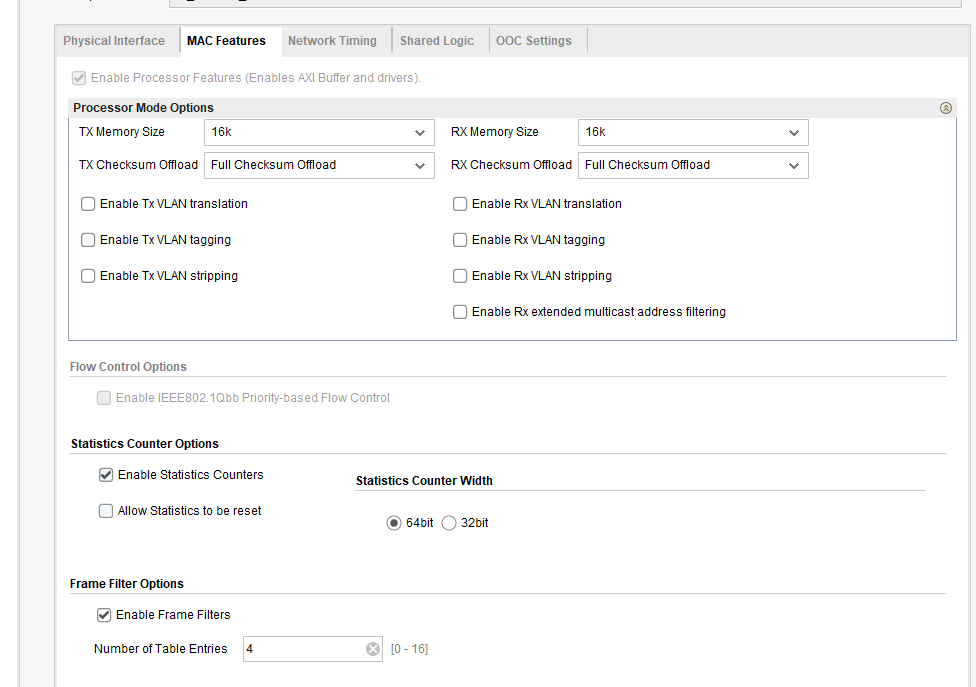

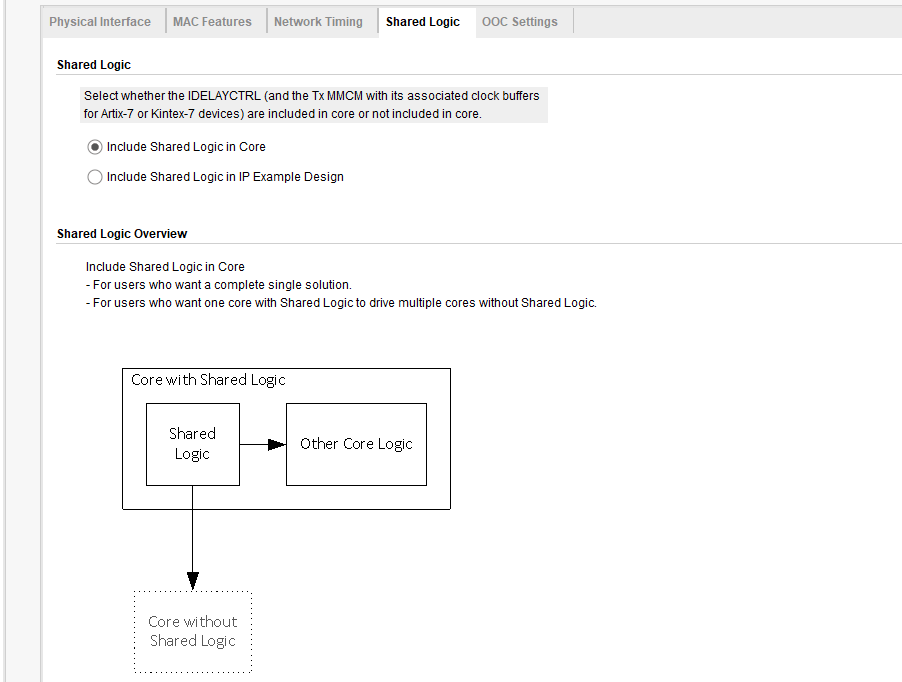

2.添加AXI 1G/2.5G Ethernet Subsystem模块并进行配置。

其他保持默认即可,点击OK。

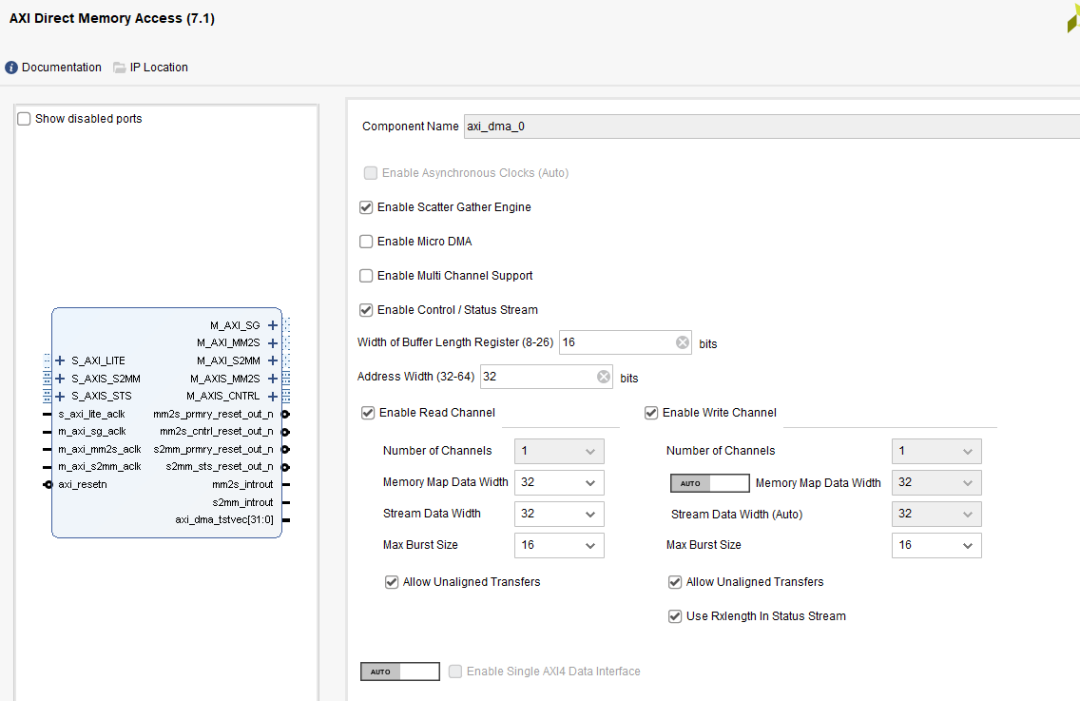

3.添加AXI Direct Memory Access模块。

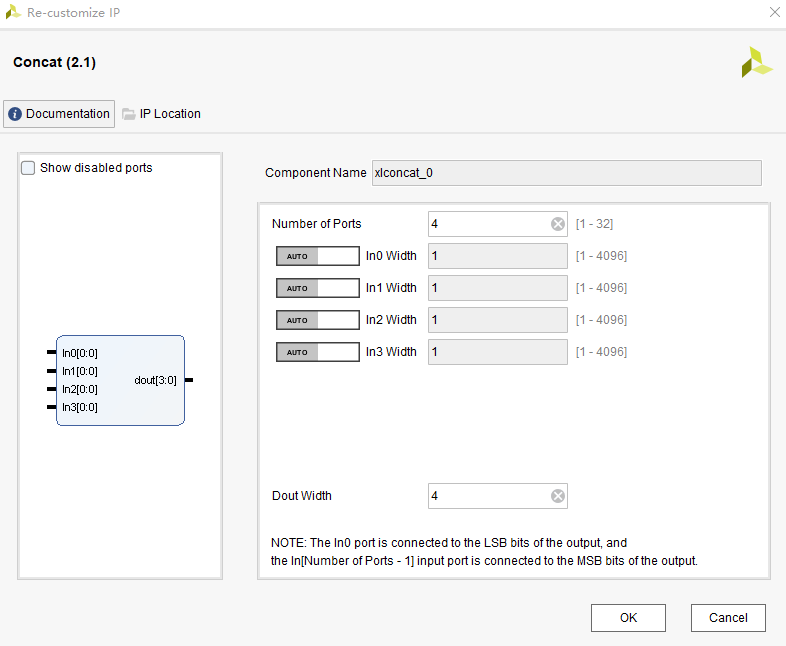

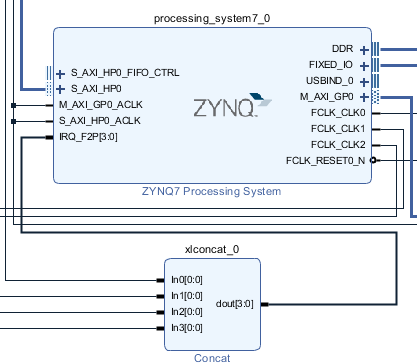

4.添加concat模块,并修改为4个端口。连接PL至PS的中断。

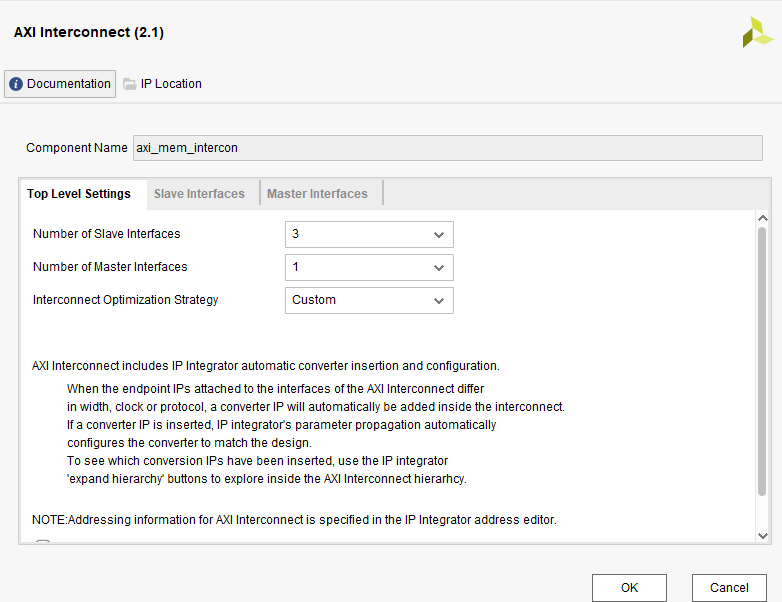

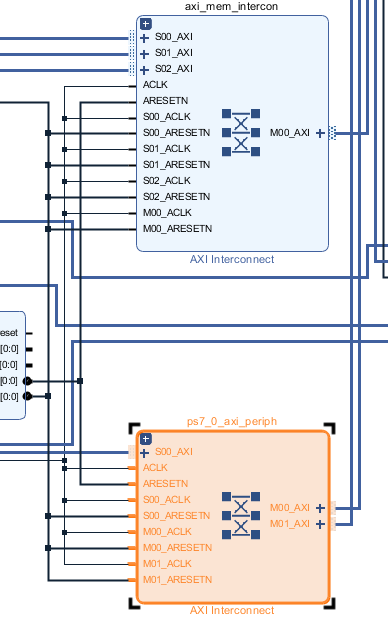

5.添加两个AXI Interconnect模块,其中一个默认,另一个进行修改。

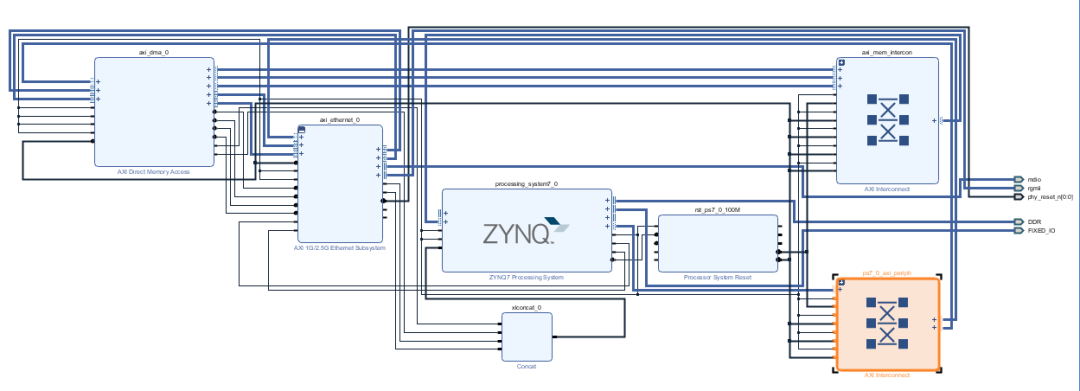

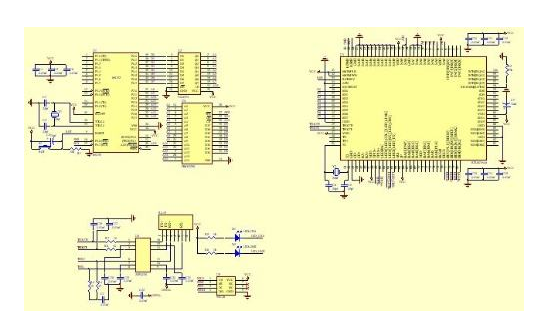

6.进行连线,先进行自动连线,不对的地方需要自己手动修改,最终连线效果如下图。

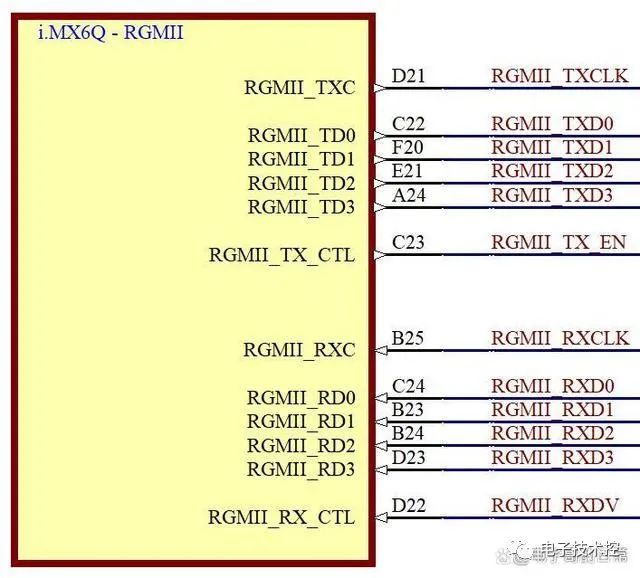

7.对引脚进行改名。

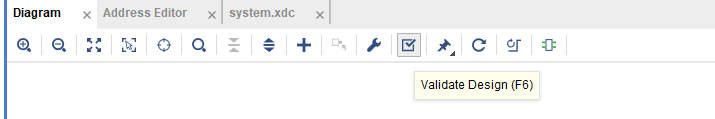

8.点击Validate Design验证block是否存在问题。

9.添加约束文件。

### -----------------RX------------------### set_property PACKAGE_PIN B19[get_ports rgmii_rxc]set_property PACKAGE_PIN A21[get_ports rgmii_rx_ctl]set_property PACKAGE_PIN B20[get_ports {rgmii_rd[0]}]set_property PACKAGE_PIN C18[get_ports {rgmii_rd[1]}]set_property PACKAGE_PIN A19[get_ports {rgmii_rd[2]}]set_property PACKAGE_PIN A18[get_ports {rgmii_rd[3]}]### -----------------TX------------------### set_property PACKAGE_PIN B15[get_ports rgmii_txc]set_property PACKAGE_PIN C15[get_ports rgmii_tx_ctl]set_property PACKAGE_PIN A17[get_ports {rgmii_td[0]}]set_property PACKAGE_PIN A16[get_ports {rgmii_td[1]}]set_property PACKAGE_PIN B17[get_ports {rgmii_td[2]}]set_property PACKAGE_PIN B16[get_ports {rgmii_td[3]}]set_property IOSTANDARD LVCMOS18[get_ports rgmii_rxc]set_property IOSTANDARD LVCMOS18[get_ports rgmii_rx_ctl]set_property IOSTANDARD LVCMOS18[get_ports {rgmii_rd[*]}]set_property IOSTANDARD LVCMOS18[get_ports rgmii_txc]set_property IOSTANDARD LVCMOS18[get_ports rgmii_tx_ctl]set_property IOSTANDARD LVCMOS18[get_ports {rgmii_td[*]}]set_property PACKAGE_PIN R18[get_ports mdio_mdc]set_property PACKAGE_PIN T17[get_ports mdio_mdio_io]set_property IOSTANDARD LVCMOS18[get_ports mdio_mdc]set_property IOSTANDARD LVCMOS18[get_ports mdio_mdio_io]set_property IOSTANDARD LVCMOS18[get_ports phy_reset_n_0[0]]set_property PACKAGE_PIN T19[get_ports phy_reset_n_0[0]]

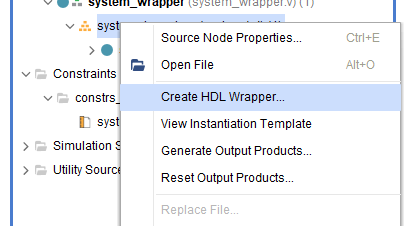

10.先生成顶层文件,再点击下方的Generate Output...。

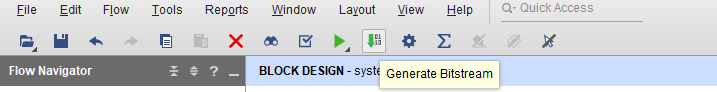

11.生成bit流文件。

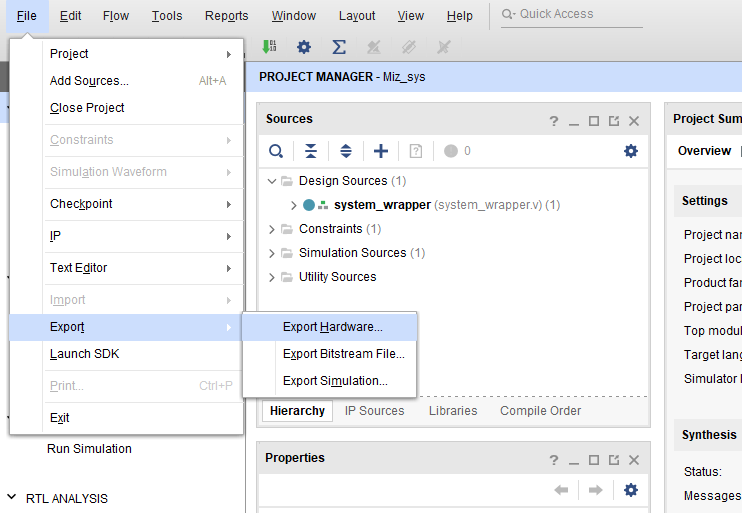

12.若生成比特流成功,则导出比特流,打开vitis软件进行工程创建。若显示失败,参考本人另一帖子。https://blog.csdn.net/c_lllll_ll/article/details/154642857?spm=1001.2014.3001.5501

13.导出bit流文件。

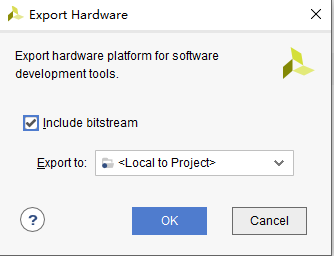

14.打开SDK。若读者使用vitis,则需要自主创建工程。

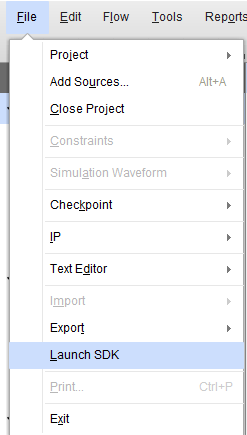

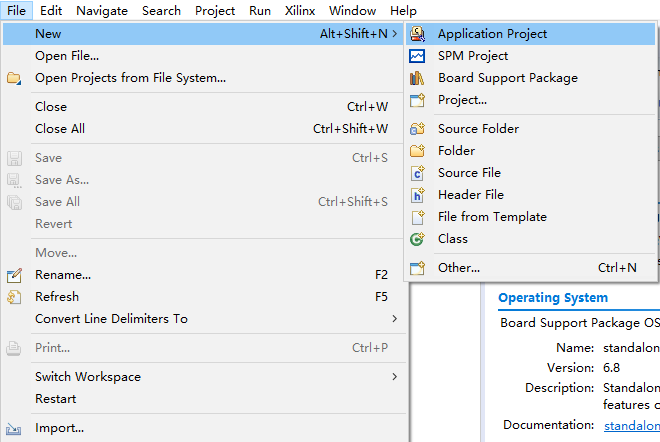

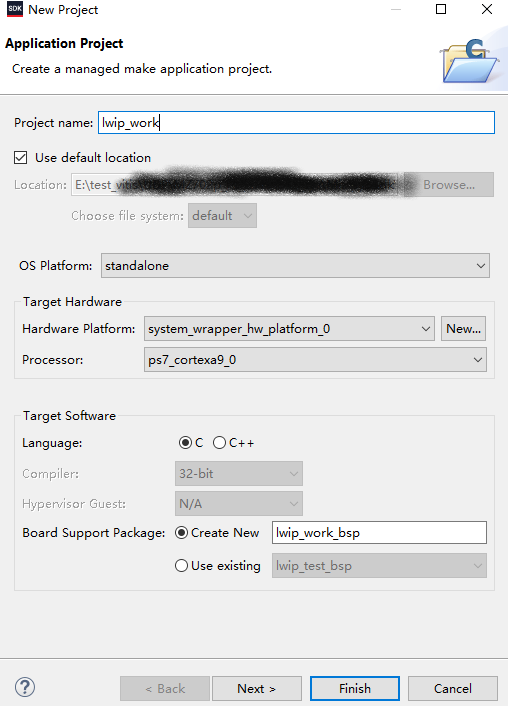

15.新建工程。

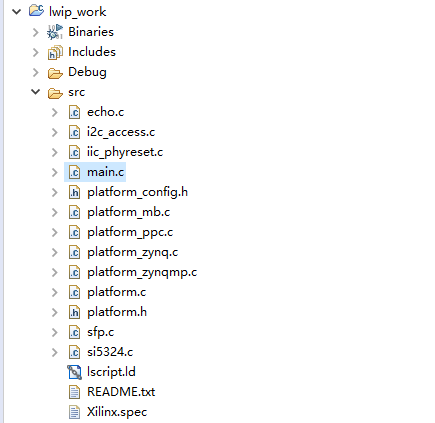

16.选择lwIP Echo Server,点击finish

17.此时需要打开bsp setting查看配置。

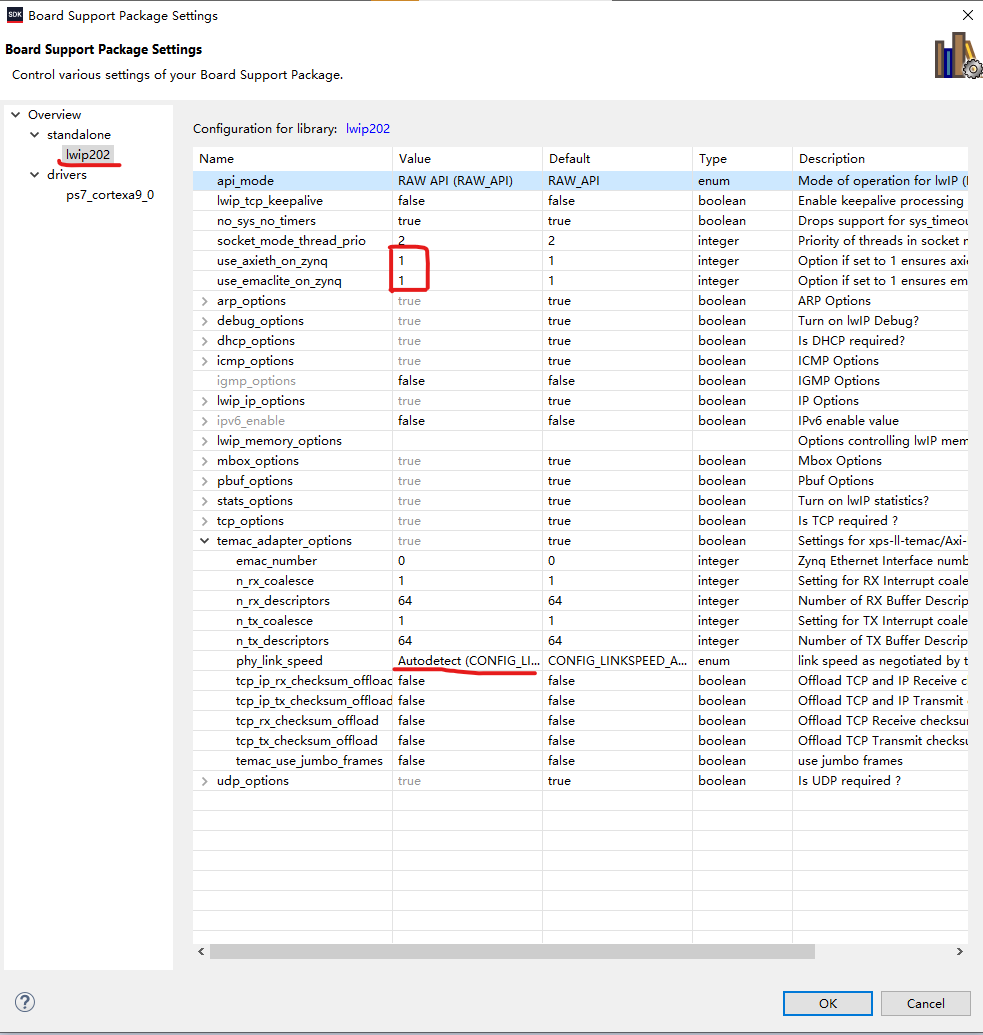

18.上面两个value需要配置为1,因为是进行pl端扩展的以太网通信实验。ps端以太网测试则修改为0即可,下方的phy_link_speed需要设置为自动检测。

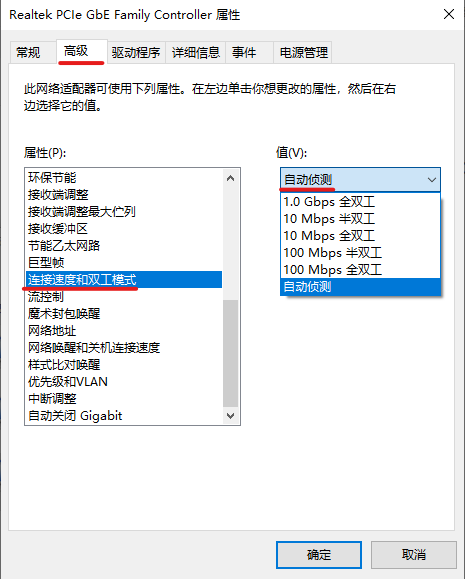

19.phy_link_speed的设置需要与电脑网口配置相同,由于电脑网口配置一般都为自动检测,读者也可以自行检查。

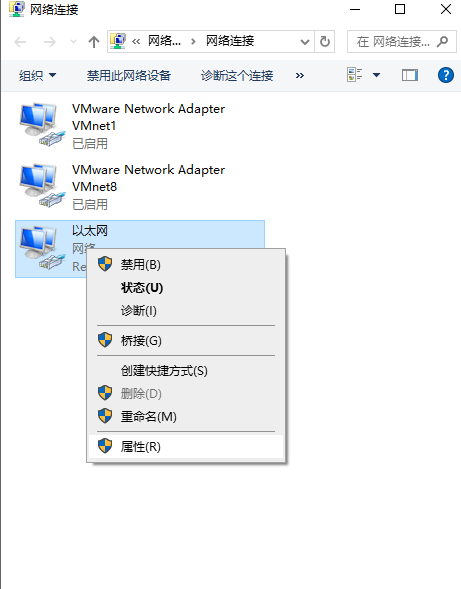

(1)终端搜索 查看网络连接

(2)点击属性

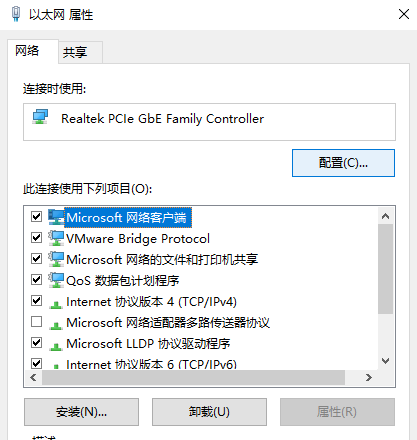

(3)点击上方的 配置。

(4)点击 高级,在下面的属性中找到 连接速度和双工模式,右边查看电脑网口配置。

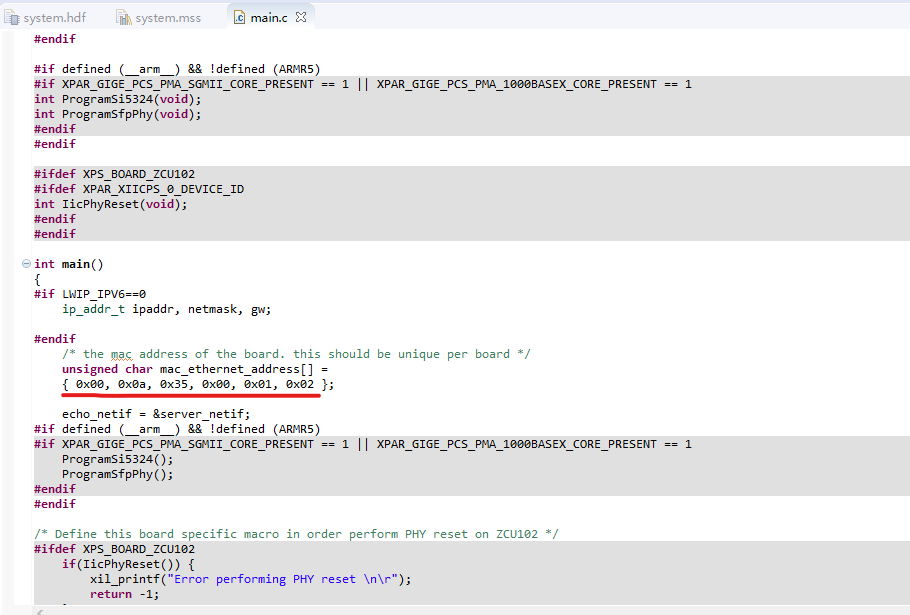

20.在左侧文件栏中打开main.c函数,

21.查看sdk自动生成的测试代码中的mac地址

21.打开cmd,输入ipconfig,查看局域网内是否有相同的mac地址的设备,若有则需要修改代码,修改为不同的即可。

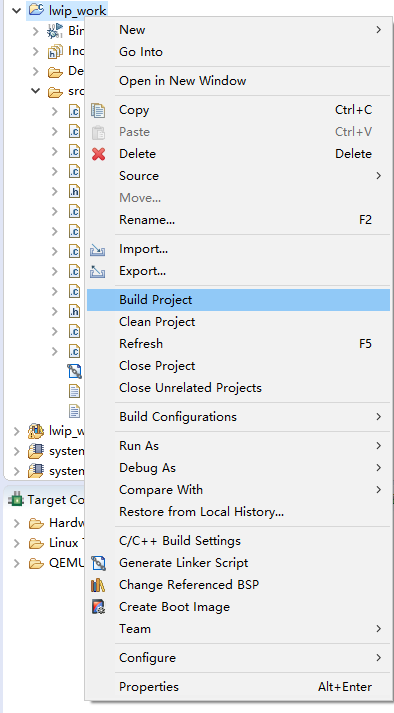

22.进行编译。

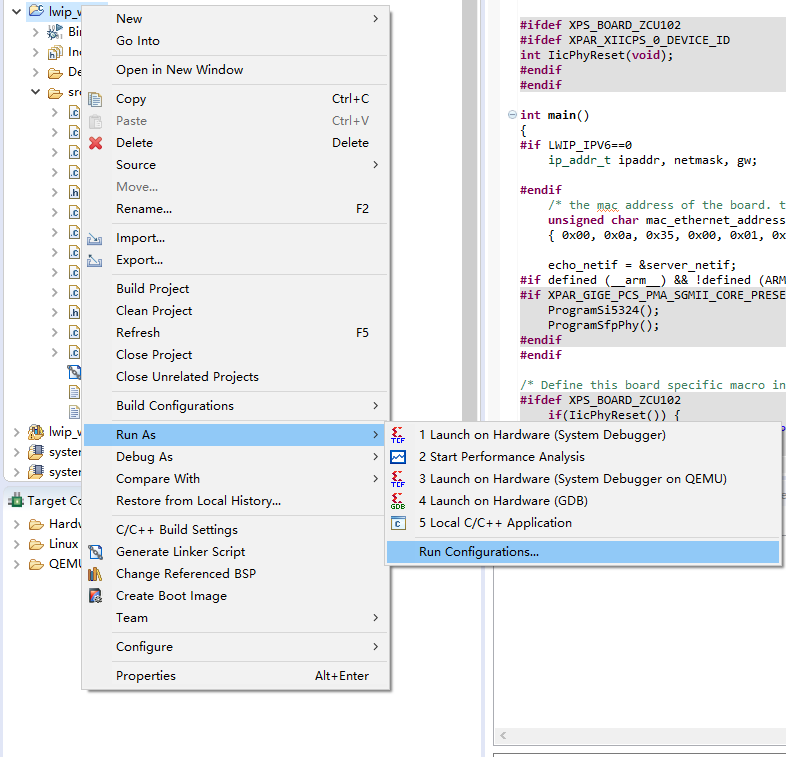

23.sdk需要点击run configuration进行配置。

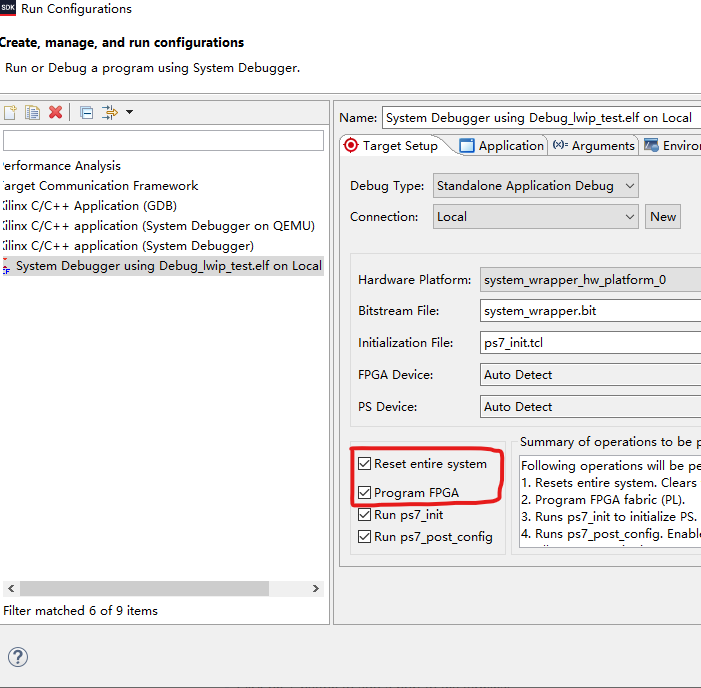

24.进行勾选,勾选后,连接好开发板的电源线,串口线,下载线,以太网的网线。

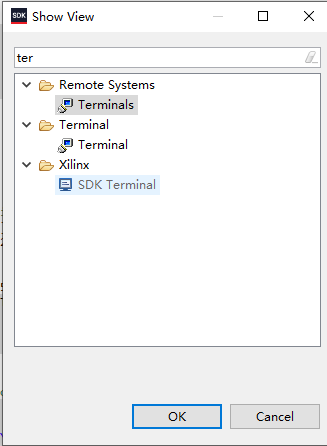

25.打开串口。

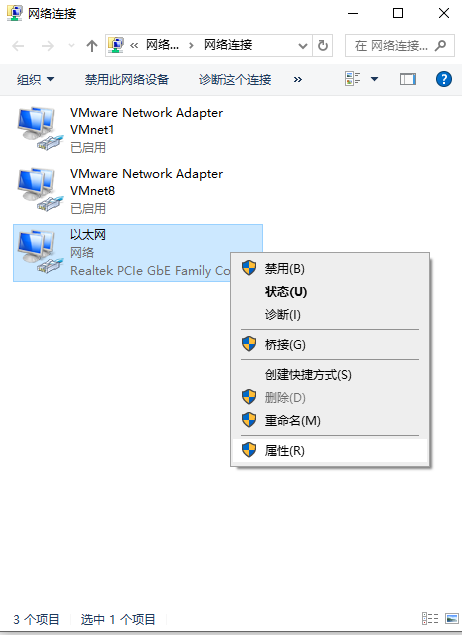

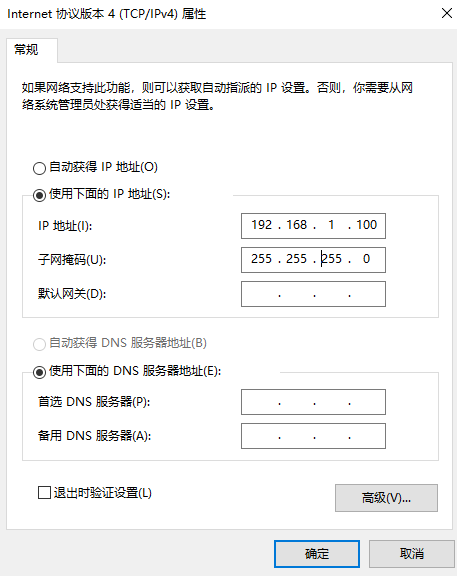

26.配置电脑网址。

点击属性。

点击协议版本4。

需要配置网址,与开发板网址处于同一ip。

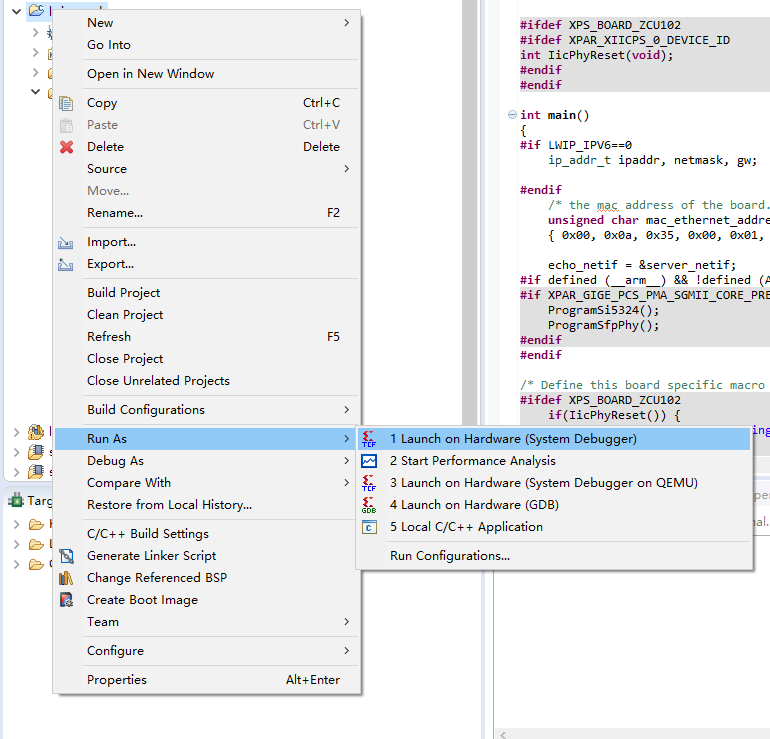

27.烧录程序。

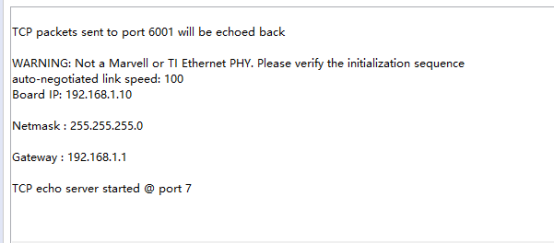

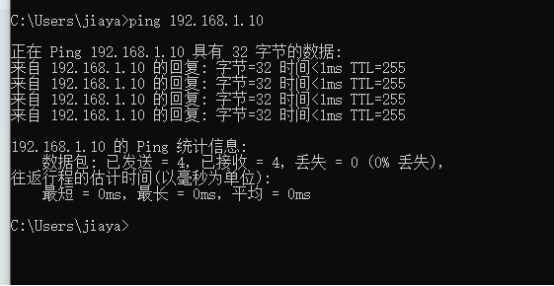

27.此时可以看到串口正常打印出开发板的ip地址,子网掩码,端口号。然后在终端进行ping连接。

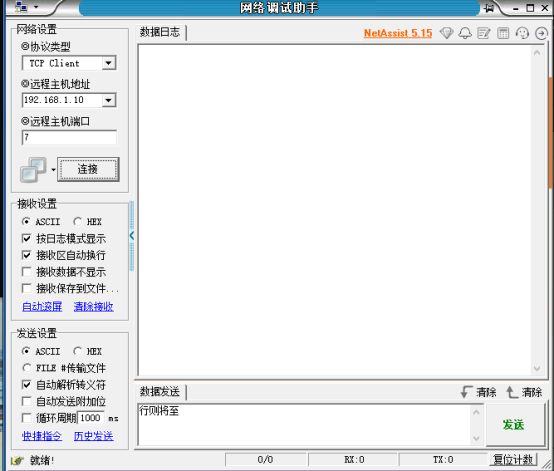

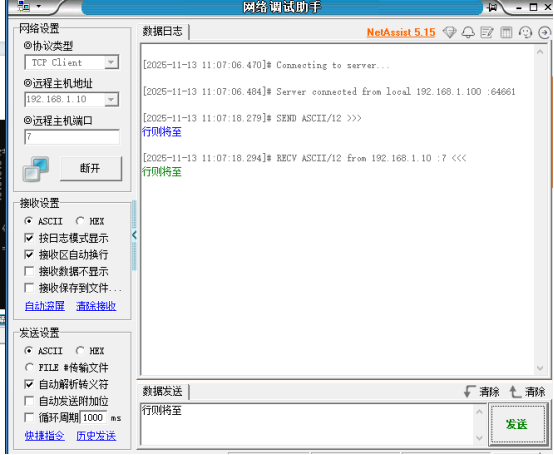

28.打开网络调试助手,选择TCP Client,点击连接。

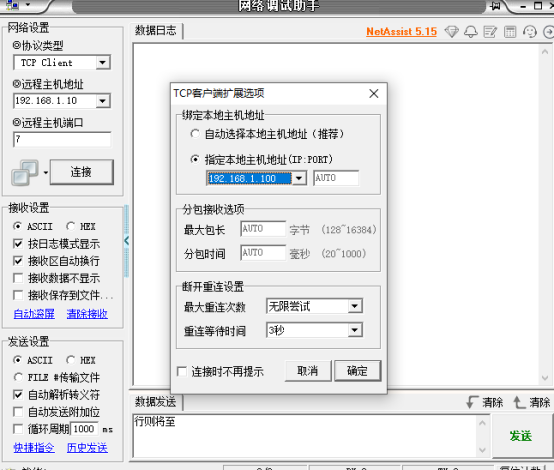

选择指定本地主机地址,并选择配置的ip地址,点击确定。

29.连接成功后,输入数据,回传成功,实验结束。

-

以太网

+关注

关注

41文章

6184浏览量

181549 -

通信

+关注

关注

18文章

6450浏览量

140258 -

开发板

+关注

关注

26文章

6419浏览量

120806 -

Zynq

+关注

关注

10文章

633浏览量

49570

原文标题:基于ZYNQ开发板实现以太网通信

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

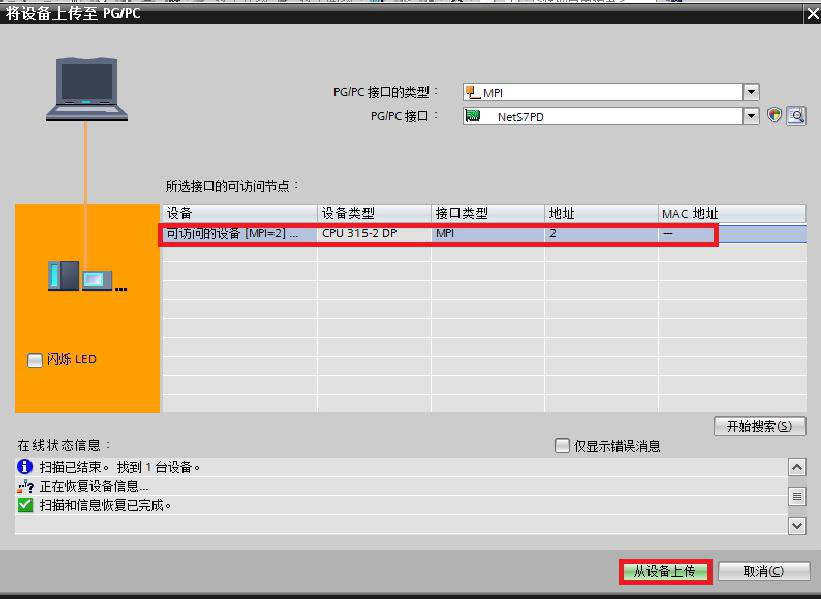

西门子200ppi转以太网通过CHNet-S7200PD实现以太网通信及ModbusTCP配置方法

西门子300mpi/dp转以太网通过CHNet-S7300MD实现以太网通信及ModbusTCP配置方法

实现以太网通信硬件电路方法

DE2-115开发板以太网通信问题

请问UDP SOCKET要用操作系统才可以实现以太网通信吗?

用51单片机控制RTL8029实现以太网通信

单片机实现以太网通讯硬件设计

W5100在单片机实现以太网通信中的应用

S7-200SMART开放以太网通信

如何使用51单片机控制RTL8019AS实现以太网通讯

基于ZYNQ-MZ702P开发板实现以太网通信

基于ZYNQ-MZ702P开发板实现以太网通信

评论