CDCP1803:高性能1:3 LVPECL时钟缓冲器的设计指南

在电子设计领域,时钟信号的精确分配至关重要,它直接影响着整个系统的性能和稳定性。TI公司的CDCP1803时钟驱动器,作为一款专为时钟分配优化的器件,以其出色的特性和灵活的配置,成为众多工程师的首选。本文将深入剖析CDCP1803的技术细节、应用要点以及设计注意事项,帮助工程师们更好地利用这款器件。

文件下载:cdcp1803.pdf

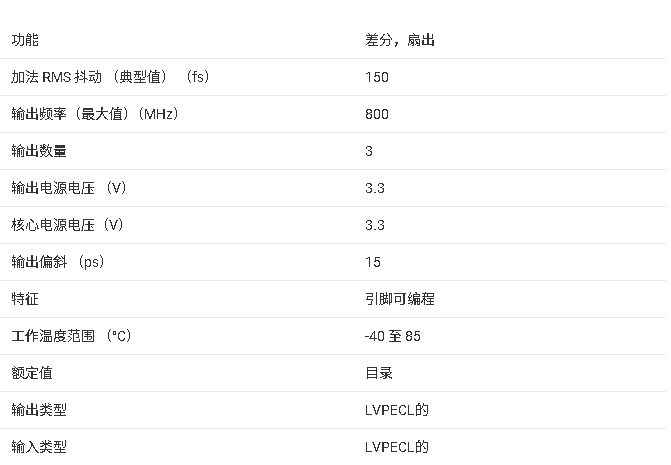

一、关键特性速览

1. 信号分配与输出

CDCP1803能够将一路差分时钟输入信号分配到三路LVPECL差分时钟输出,并且为其中两路LVPECL输出提供可编程的分频功能。这一特性使得它在不同时钟频率需求的系统中具有很强的适应性。

2. 低输出偏斜

其典型输出偏斜仅为15ps,确保了时钟信号在分配过程中的同步性,减少了因信号延迟差异而导致的系统误差。

3. 宽工作电压范围

工作电压范围为3V - 3.6V,能够适应多种电源环境,增加了器件的通用性。

4. 高速信号处理

支持高达800MHz的LVPECL信号速率,满足高速系统的时钟需求。

5. 广泛的信号兼容性

差分输入级具有较宽的共模范围,能够接受LVDS、HSTL、CML、VML、SSTL - 2等多种差分信号,以及LVTTL/LVCMOS单端信号,方便与不同类型的信号源连接。

6. 偏置电压输出

提供VBB偏置电压输出,可作为单端输入信号的共模电压参考,简化了单端驱动应用的设计。

二、引脚功能详解

1. 使能引脚(EN)

用于同时启用或禁用所有输出。当EN = 1时,输出根据S[2:0]的设置开启;当EN = 0时,输出Y[2:0]处于高阻抗状态。

2. 差分输入引脚(IN, IN)

差分输入时钟,输入级灵敏度高且共模范围宽。建议在输入前对PCB传输线进行端接,如使用100Ω跨接输入。也可以使用单端信号驱动,此时互补输入应连接到VBB。

3. 模式选择引脚(S[2:0])

用于选择不同的工作模式,定义了Y[2:0]的输出配置。

4. 偏置电压输出引脚(VBB)

输出电压为VDD – 1.3V,可用于为单端输入信号的未使用互补输入IN提供偏置。驱动负载时,输出电流限制在约1.5mA。

5. 电源引脚

VDDPECL为PECL输入和内部逻辑提供电源,VDD[2:0]为输出Y[2:0]提供PECL输出电源电压。每个输出可以通过将相应的VDDx拉至GND来禁用。

三、工作模式配置

CDCP1803通过三个控制端子(S0, S1, S2)和一个使能端子(EN)来选择不同的输出模式。具体的模式配置可以参考文档中的表1,工程师们可以根据实际需求灵活设置这些引脚,以实现不同的输出分频和开关控制。

四、电气特性分析

1. 输入特性

输入频率范围为0 - 800MHz,输入电压摆幅在500 - 1300mV之间,输入阻抗为300kΩ,输入电容为1pF。这些特性确保了器件能够准确地接收各种类型的时钟信号。

2. 输出特性

输出频率最高可达800MHz,输出电压摆幅在500mV以上,输出偏斜典型值为15ps,上升和下降时间在200 - 350ps之间。这些参数保证了输出时钟信号的质量和稳定性。

3. 抖动特性

在不同的频率范围和分频模式下,器件的附加相位抖动较小,例如在12kHz - 20MHz、fout = 250MHz - 800MHz、1分频模式下,抖动典型值为0.15ps rms。

五、热设计要点

CDCP1803采用24引脚QFN封装,为了确保良好的散热性能,PCB设计时需要特别注意。建议使用四层JEDEC测试板,并在PCB中设置四个直径为22mil的热过孔,将封装的散热焊盘与PCB有效连接,以保证良好的散热效果。通过合理的热设计,可以降低器件的结温,提高其可靠性和稳定性。

六、应用设计建议

1. 输入终端匹配

对于LVPECL输入,推荐使用100Ω电阻跨接输入端子进行端接,或者使用2 × 50Ω电阻,中心抽头连接电容以抑制奇模噪声和补偿传输线失配。VBB输出也可以连接到中心抽头,为输入信号提供偏置。

2. 单端信号驱动

当使用单端信号驱动时,输入信号连接到一个输入,互补输入应正确偏置到输入信号的中心电压。对于LVCMOS信号,可以使用简单的电压分压器实现。更好的方法是对输入信号进行交流耦合,然后使用VBB参考输出重新偏置信号。

3. 复位和控制端子切换

在设备使能(EN = 0 → 1)时,输出驱动会经历一个短暂的高信号状态,然后进入低状态。在启用单个输出级时,输出状态会在第一个正时钟过渡后变得有效。

七、总结

CDCP1803是一款功能强大、性能出色的时钟缓冲器,具有广泛的信号兼容性、低输出偏斜和高速信号处理能力。通过合理的引脚配置、电气特性分析和热设计,工程师们可以充分发挥其优势,满足各种复杂系统的时钟分配需求。在实际应用中,还需要根据具体的设计要求和系统环境,灵活调整设计方案,确保系统的稳定性和可靠性。你在使用CDCP1803的过程中遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

设计指南

+关注

关注

0文章

277浏览量

8969

发布评论请先 登录

DAC3482用CDCE62005做时钟发生器,产生的FIFO-OSTR又经过了时钟缓冲器CDCP1803,CDCP1803的作用是什么?

DAC3482从时钟发生器出来的FIFO_OSTR信号连入时钟缓冲器CDCP1803后才输出到DA中,时钟缓冲器起什么作用?

CDCLVP2108 16路LVPECL输出高性能时钟缓冲器数据表

CDCLVP2102四路LVPECL输出高性能时钟缓冲器数据表

16路LVPECL输出、高性能时钟缓冲器CDCLVP1216数据表

CDCLVP2106 12路LVPECL输出高性能时钟缓冲器数据表

CDCLVP1204四路LVPECL输出高性能时钟缓冲器数据表

CDCLVP1102双路LVPECL输出高性能时钟缓冲器数据表

CDCP1803:高性能1:3 LVPECL时钟缓冲器的设计指南

CDCP1803:高性能1:3 LVPECL时钟缓冲器的设计指南

评论