探索CDCVF855:高性能时钟驱动器的技术解析

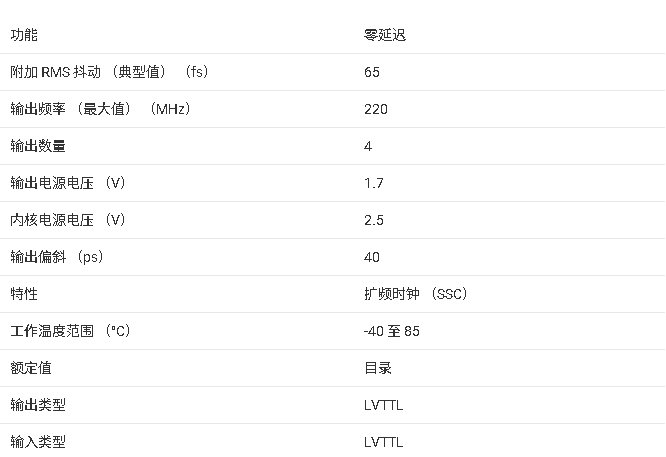

在电子设计领域,时钟驱动器的性能对于系统的稳定性和数据传输的准确性至关重要。今天,我们将深入探讨德州仪器(Texas Instruments)的CDCVF855——一款2.5 - V锁相环(PLL)时钟驱动器,看看它如何在众多应用中发挥关键作用。

文件下载:cdcvf855.pdf

一、CDCVF855的关键特性

1. 频率与兼容性

CDCVF855的工作频率范围为60 MHz至220 MHz,能够满足多种不同应用场景的需求。它还与扩频时钟兼容,有助于降低电磁干扰(EMI),这在对EMI要求严格的环境中尤为重要。

2. 低抖动与低相位偏移

低抖动是衡量时钟驱动器性能的重要指标之一。CDCVF855在周期抖动(Period Jitter)和周期到周期抖动(Cycle - Cycle Jitter)方面表现出色,例如在200 MHz时,周期抖动可达±30 ps,周期到周期抖动可达±40 ps。同时,它的静态相位偏移仅为±50 ps,确保了时钟信号的准确性和稳定性。

3. 时钟分配与输出

该驱动器实现了1对4的差分时钟分配(SSTL2),可以将一个差分时钟输入对(CLK, CLK)分配到4个差分时钟输出对(Y[0:3], Y[0:3])和一个差分反馈时钟输出对(FBOUT, FBOUT),为系统提供了灵活的时钟分配方案。

4. 电源与功耗

CDCVF855可由2.6 - V或2.5 - V双电源供电,并且静态电流消耗小于100 µA,在低功耗设计方面表现优秀。当没有CLK输入信号或PWRDWN为低电平时,它会进入低功耗模式,进一步降低功耗。

二、应用场景

1. DDR内存模块

在DDR400/333/266/200等内存模块中,CDCVF855能够为内存提供稳定的时钟信号,确保数据的准确读写。其低抖动和低相位偏移特性有助于提高内存的性能和可靠性。

2. 零延迟扇出缓冲器

作为零延迟缓冲器,CDCVF855可以将输入时钟信号无延迟地分配到多个输出端,满足系统中不同模块对时钟信号的需求。

三、工作原理与控制

CDCVF855基于PLL电路,需要一定的稳定时间来实现PLL的锁相。在电源上电后,需要等待稳定时间过去,才能保证时钟输出的稳定性。

时钟输出由时钟输入(CLK, CLK)、反馈时钟(FBIN, FBIN)和模拟电源输入(AVDD)控制。当PWRDWN为高电平时,输出与CLK同相且同频;当PWRDWN为低电平时,所有输出被禁用,进入高阻态,PLL关闭,进入低功耗模式。此外,当输入频率低于建议的检测频率(典型值为10 MHz)时,设备也会进入低功耗模式,当输入频率恢复到大于20 MHz时,PLL重新开启,输出恢复正常。

四、电气特性与参数

1. 绝对最大额定值

在使用CDCVF855时,需要注意其绝对最大额定值,如电源电压范围为0.5 V至3.6 V,输入和输出电压范围为 - 0.5 V至VDDQ + 0.5 V等。超出这些额定值可能会对设备造成永久性损坏。

2. 推荐工作条件

推荐的工作条件包括电源电压、输入电压、输出电流等参数。例如,VDDQ的范围为2.3 V至2.7 V,AVDD为VDDQ - 0.12至2.7 V等。在设计电路时,应确保这些参数在推荐范围内,以保证设备的正常工作。

3. 电气特性参数

CDCVF855的电气特性参数包括输入电压、输出电压、输出电压摆幅、输入电流等。例如,在VDDQ = 2.3 V,IOH = - 12 mA时,高电平输出电压为1.7 V;在VDDQ = 2.3 V,IOL = 12 mA时,低电平输出电压为0.6 V。这些参数对于电路设计和性能评估非常重要。

五、封装与引脚功能

CDCVF855采用28引脚的TSSOP封装,不同引脚具有不同的功能。例如,AGND为2.5 - V模拟电源地,AVDD为2.5 - V模拟电源,CLK和CLK为差分时钟输入等。了解引脚功能对于正确连接和使用该设备至关重要。

六、思考与总结

CDCVF855作为一款高性能的时钟驱动器,在低抖动、低相位偏移、时钟分配和低功耗等方面表现出色,适用于多种应用场景。在实际设计中,电子工程师需要根据具体的应用需求,合理选择工作参数,确保设备在推荐的工作条件下运行。同时,要注意绝对最大额定值,避免因参数超出范围而损坏设备。大家在使用CDCVF855的过程中,有没有遇到过一些特殊的问题或者有什么独特的应用经验呢?欢迎在评论区分享。

-

低功耗

+关注

关注

12文章

3981浏览量

106848 -

时钟驱动器

+关注

关注

0文章

124浏览量

14407

发布评论请先 登录

CDCVF111 1:9差分LVPECL时钟驱动器数据表

探索CDCVF855:高性能时钟驱动器的技术解析

探索CDCVF855:高性能时钟驱动器的技术解析

评论