高速双时钟缓冲器LMH2180:特性、应用与设计要点

在电子设计领域,时钟缓冲器是确保系统时钟信号稳定和准确的关键组件。今天,我们要深入探讨的是德州仪器(TI)的LMH2180,一款专为便携式通信和多时钟系统设计的高速双时钟缓冲器。

文件下载:lmh2180.pdf

一、LMH2180的特性亮点

1. 出色的电气性能

- 带宽与增益:小信号带宽(SSBW)典型值可达78MHz,大信号带宽(LSBW)在(V{IN}=1.0V{PP})时典型值为60MHz(2.7V供电),5V供电时SSBW可达87MHz,LSBW为68MHz。增益平坦度(GFN)在(f>100kHz)时,2.7V供电下小于0.1dB的带宽典型值为4.9MHz,5V供电时为25MHz。

- 低噪声与低失真:相位噪声在(V{IN}=1V{PP}),(f{C}=38.4MHz),(Delta f = 1kHz)时典型值为(-123dBc/Hz);输入参考电压噪声在(f = 1MHz),(R{SOURCE}=50Omega)时,2.7V供电典型值为13nV/√Hz,5V供电为12nV/√Hz。输出与输入隔离度(ISOLATION)在(f = 1MHz),(R{SOURCE}=50Omega)时典型值为84dB,串扰抑制(CT)在(f = 38.4MHz),(V{IN}=1V_{PP})时,2.7V供电典型值为41dB,5V供电为59dB。

- 快速的时域响应:上升时间((t{r}))典型值为6ns,下降时间((t{f}))典型值为5ns(2.7V供电),5V供电时上升和下降时间典型值均为6ns。建立时间((t{s}))到0.1%在(1V{PP})阶跃时,2.7V供电典型值为120ns,5V供电为70ns。过冲(OS)在0.1(V{PP})阶跃时,2.7V供电典型值为37%,5V供电为13%。压摆率(SR)在(V{IN}=2V_{PP})时,2.7V供电典型值为106V/µs,5V供电为124V/µs。

- 低功耗设计:总电源电流在2.7V供电且两个缓冲器均使能无负载时典型值为2.3mA,5V供电时为4.0mA。关断电流在2.7V供电时为30µA,5V供电为49µA。

2. 灵活的设计特性

- 宽电源电压范围:电源电压范围为2.4V至5V,能适应不同的电源系统设计。

- 独立缓冲器使能引脚:每个缓冲器都有独立的使能引脚,可根据实际需求灵活开启或关闭缓冲器,优化电流消耗。

- 快速导通技术:具备快速(T_{on})技术,能快速响应时钟信号。

- 串扰抑制电路:有效消除多个时钟信号之间的串扰,确保系统在基带和振荡器信号路径之间的出色运行。

- 丰富的封装选项:提供8引脚WSON(焊球且无回拉)和8凸点DSBGA封装,满足不同的应用场景和PCB布局需求。

- 宽温度范围:工作温度范围为(-40^{circ}C)至(85^{circ}C),适用于多种环境条件。

二、应用领域广泛

1. 3G移动应用

在3G移动设备中,LMH2180可用于WLAN - WiMAX模块、TD - SCDMA多模式MP3和相机、GSM模块等,为这些设备提供稳定准确的时钟信号,确保通信的可靠性和稳定性。

2. 振荡器模块

在各种振荡器模块中,LMH2180能有效减少基芯片对振荡器的杂散信号影响,同时降低负载电阻和电容对振荡器的影响,提高振荡器的驱动能力。

三、设计要点与注意事项

1. 输入配置

LMH2180的输入内部偏置为1V,这使得输入信号可以进行交流耦合,无需外部偏置电阻。这种设计避免了振荡器输出端的大直流负载,防止负载阻抗影响振荡频率。但要注意,交流信号的最大幅度为(2V{PP})。耦合电容(C{1})应足够大,以让交流信号顺利通过。

2. 驱动容性负载

每个缓冲器都能驱动容性负载,但直接连接到输出的电容会成为缓冲器环路的一部分。电容会降低增益/相位裕度,影响稳定性,可能导致频率响应出现峰值,极端情况下会产生振荡。因此,在驱动大容性负载时,建议在缓冲器和负载电容之间串联一个电阻,具体阻值可通过实验确定。

3. 相位噪声

时钟缓冲器会给时钟信号增加噪声,导致时钟信号相位的不确定性,即抖动(时域)或相位噪声(频域)。在无线局域网等通信系统中,需要低抖动/相位噪声的时钟信号以降低误码率。在测量LMH2180的相位噪声时,使用了高精度的测量设置,确保准确评估其性能。

4. 布局设计

在电路设计和PCB布局时,要确保所有去耦和其他接地连接使用相同的接地平面,以减少干扰。去耦电容应靠近LMH2180放置在(V{DD})和(V{SS})之间,以保证干净的电源电压。此外,要合理选择组件值,电阻值既要足够低以避免显著的噪声贡献,又要足够大以避免在加载输入或输出时过度增加功耗。

四、总结

LMH2180作为一款高性能的高速双时钟缓冲器,凭借其出色的电气性能、灵活的设计特性和广泛的应用领域,成为电子工程师在便携式通信和多时钟系统设计中的理想选择。在实际设计过程中,充分了解其特性和设计要点,合理布局和使用,能够发挥其最大优势,为系统的稳定运行提供有力保障。你在使用时钟缓冲器时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

电子设计

+关注

关注

42文章

2870浏览量

49916

发布评论请先 登录

LMH2180,pdf datasheet (75 MHz

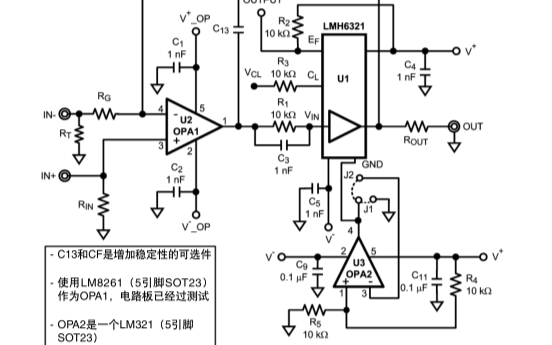

LMH6321(PSOP和TO-263)单路开环高速缓冲器评估板

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

高速双时钟缓冲器LMH2180:特性、应用与设计要点

高速双时钟缓冲器LMH2180:特性、应用与设计要点

评论