Texas Instruments ADC32RF54/55:高性能RF采样数据转换器的技术解析

在当今的电子设计领域,对于高性能、高速度的模拟到数字转换器(ADC)的需求日益增长。Texas Instruments(TI)推出的ADC32RF54和ADC32RF55这两款产品,以其卓越的性能和丰富的功能,在雷达、频谱分析、软件定义无线电等众多应用中展现出了巨大的潜力。本文将深入探讨这两款ADC的关键特性、工作原理以及设计应用中的注意事项。

文件下载:adc32rf55.pdf

关键特性剖析

高性能指标

ADC32RF54和ADC32RF55是14位、2.6 GSPS到3 GSPS的双通道ADC,具备出色的噪声性能。其噪声谱密度(NSD)表现优异,在不同的平均模式下,NSD可低至 -160.4 dBFS / Hz(4x AVG)。这种低噪声特性对于需要高精度信号处理的应用至关重要,例如雷达系统中的微弱信号检测。

在频谱性能方面,当输入频率 (f{IN}=1 GHz) ,-4 dBFS时,2x内部平均的SNR可达62.3 dBFS,SFDR HD2,3为63 dBc,SFDR最坏杂散为85 dBFS。而在 (f{IN}=1.8 GHz) ,-4 dBFS的条件下,2x内部平均的SNR为63 dBFS,SFDR HD2,3为68 dBc,SFDR最坏杂散为86 dBFS。这些性能指标使得该ADC能够在宽频范围内保持良好的信号质量。

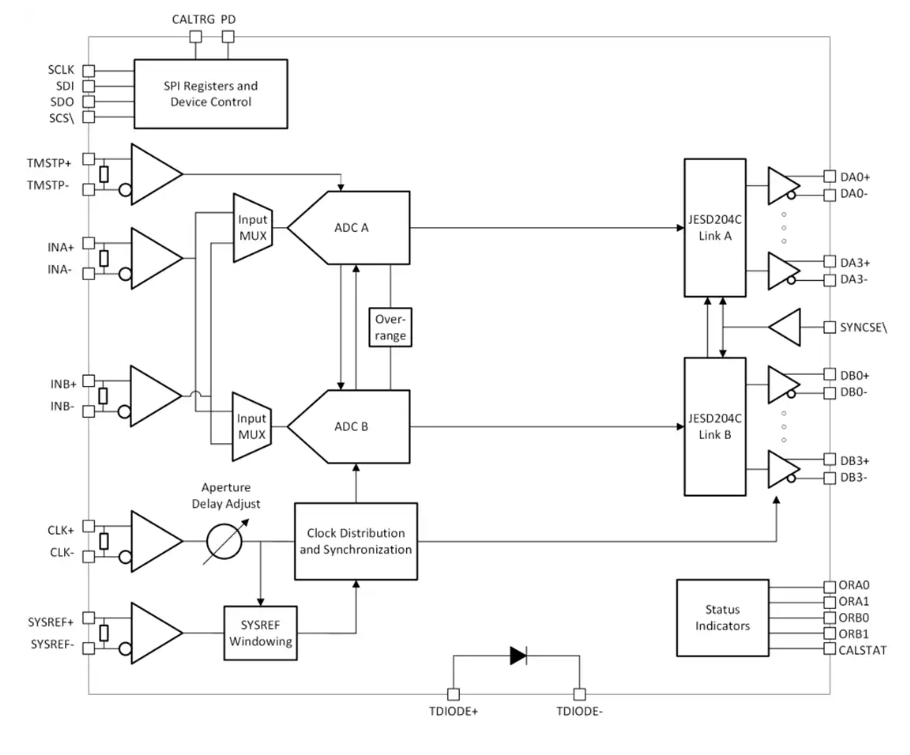

独特架构与低抖动

采用单核心(非交错)ADC架构,具有50 fs的孔径抖动和低近场残余相位噪声(在10 kHz偏移处为 -127 dBc/Hz)。低孔径抖动有助于减少信号采样时的误差,提高采样精度;而低残余相位噪声则能够降低信号的相位误差,保证信号的相位稳定性,对于需要高精度相位信息的应用,如相控阵雷达,具有重要意义。

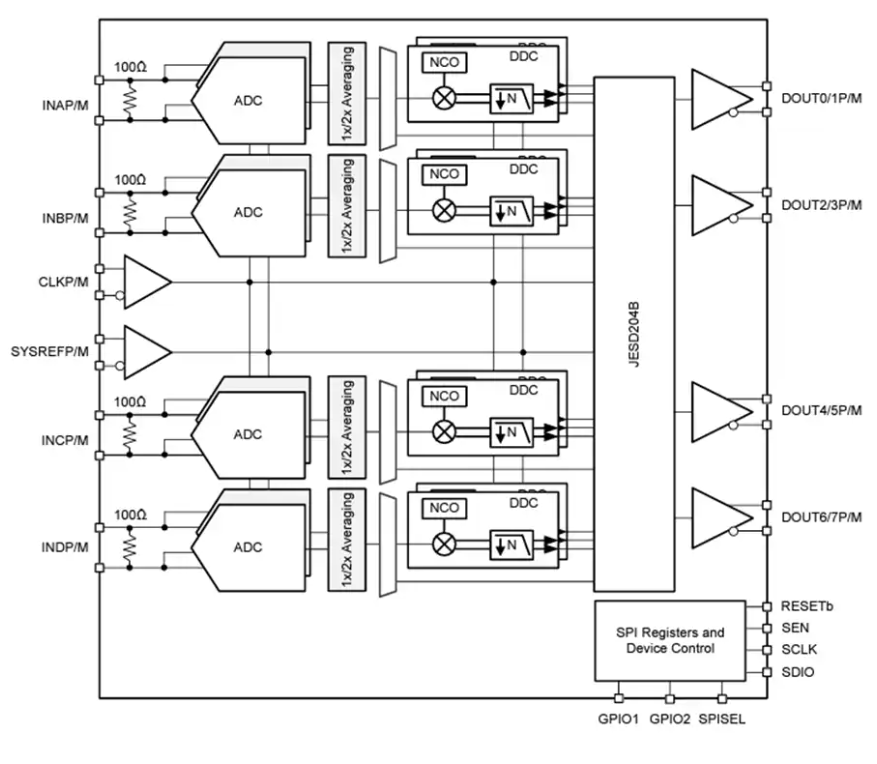

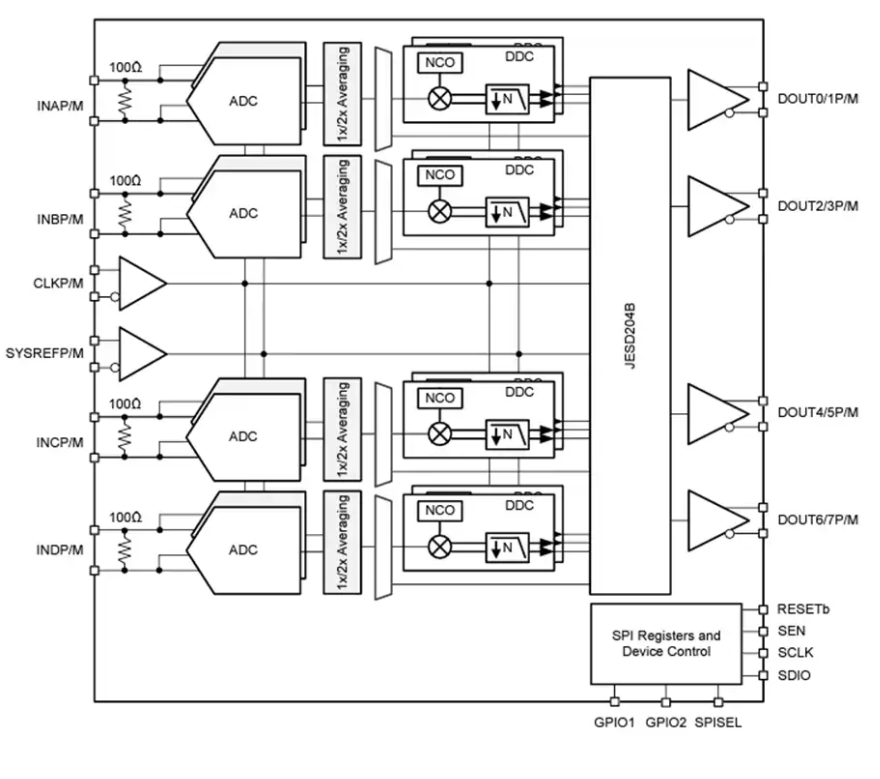

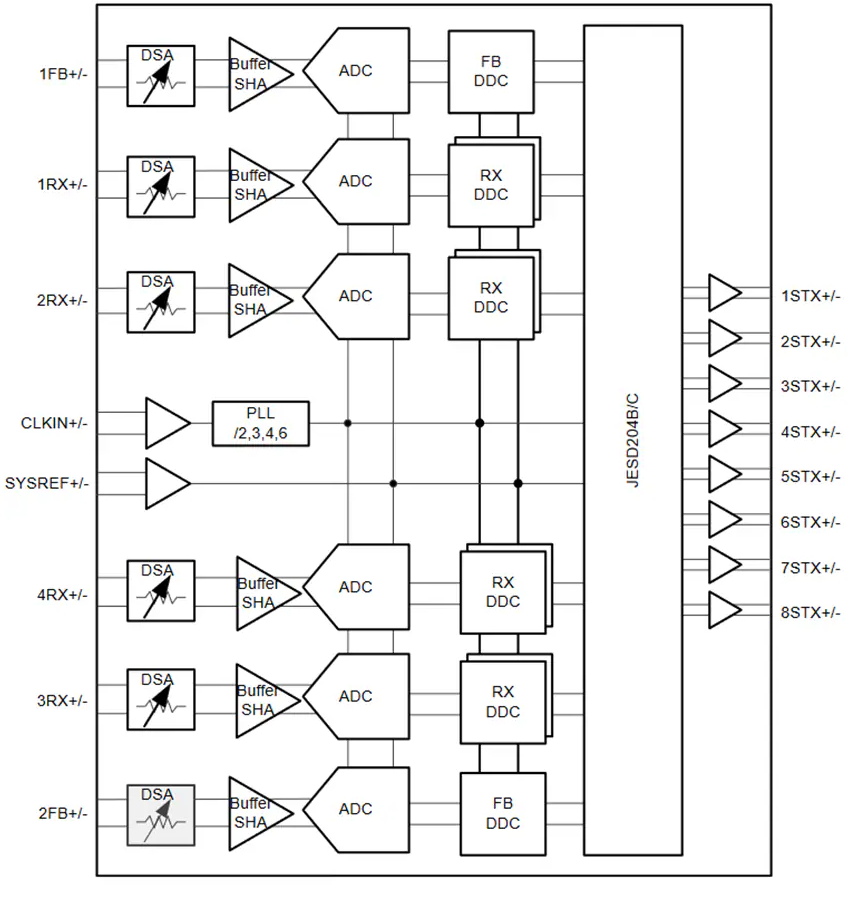

数字下变频器(DDC)功能

每个ADC通道可连接到一个四频段数字下变频器(DDC),支持高达128x的复数抽取和48位NCO相位相干跳频,跳频速度小于1 µs。这一功能使得ADC能够灵活地处理不同频段的信号,实现信号的下变频和滤波,满足多种应用场景的需求。例如,在软件定义无线电中,可以根据不同的通信协议和频段要求,快速调整NCO频率,实现信号的高效处理。

JESD204B接口

支持JESD204B串行数据接口,最大通道速率可达13 Gbps,支持子类1确定性延迟。这种高速接口能够满足高速数据传输的需求,确保ADC采集到的数据能够快速、准确地传输到后续的处理单元。

应用领域广泛

ADC32RF54和ADC32RF55适用于多种应用场景,包括相控阵雷达、频谱分析仪、软件定义无线电(SDR)、电子战、高速数字化仪、电缆基础设施和通信基础设施等。在相控阵雷达中,其高采样率和低噪声性能能够提高雷达的探测精度和分辨率;在频谱分析仪中,能够准确地分析信号的频谱特性;在软件定义无线电中,可实现灵活的信号处理和通信协议切换。

详细设计与性能分析

模拟输入特性

输入带宽与满量程

输入带宽和满量程取决于输入终端和平均模式的选择。在默认模式下,输入带宽为2.75 GHz(-3 dB),输入满量程为1.1至1.35 Vpp(2至3.5 dBm)。当启用4x平均时,-3 dB带宽会降低至约2.1 GHz,但输入满量程会增加至 + 6.6 dBm。这种灵活的配置方式使得设计师能够根据具体应用需求,平衡带宽和满量程之间的关系。

输入不平衡影响

AC性能对模拟输入的幅度和相位不平衡较为敏感。在不同的采样率和输入频率条件下,幅度和相位不平衡会对SNR、HD2、HD3和Non HD23等性能指标产生影响。因此,在设计输入电路时,需要严格控制输入信号的幅度和相位平衡,例如选择具有良好平衡性能的巴伦变压器。

过范围指示

ADC提供了两种过范围指示选项:快速过范围指示(通过GPIO1/2引脚)和嵌入JESD流的过范围指示。快速过范围指示在约6个时钟周期后可用,并且过范围指示标志会保持高电平,直到通过SPI寄存器清除。而嵌入JESD流的过范围指示则会在每个时钟周期更新,替代相应通道输出数据的LSB。这种灵活的过范围指示方式能够满足不同应用场景下对过范围检测的需求。

采样时钟输入

采样时钟输入对ADC的性能影响显著。内部采样时钟路径设计旨在降低残余相位噪声,因此需要一个非常干净的电源供应。时钟幅度应大于1 VPP,以获得最佳性能。此外,时钟输入和ADC采样电路还存在幅度噪声,该噪声与输入频率无关,仅受采样复位开关的影响。在设计时钟电路时,需要选择低抖动的时钟源,并对时钟信号进行适当的滤波和处理,以减少幅度噪声对信号质量的影响。

SYSREF输入

SYSREF输入信号用于复位内部数字块,并使其与内部多帧时钟对齐,以实现子类1确定性延迟。该输入信号可以是AC或DC耦合,通过SPI寄存器选项进行选择。在使用周期性SYSREF信号时,其频率必须是内部本地多帧时钟(LMFC)的子谐波。此外,ADC还具有内部SYSREF监测电路,用于检测可能的亚稳态和时钟周期滑移,确保SYSREF信号与采样时钟的同步。

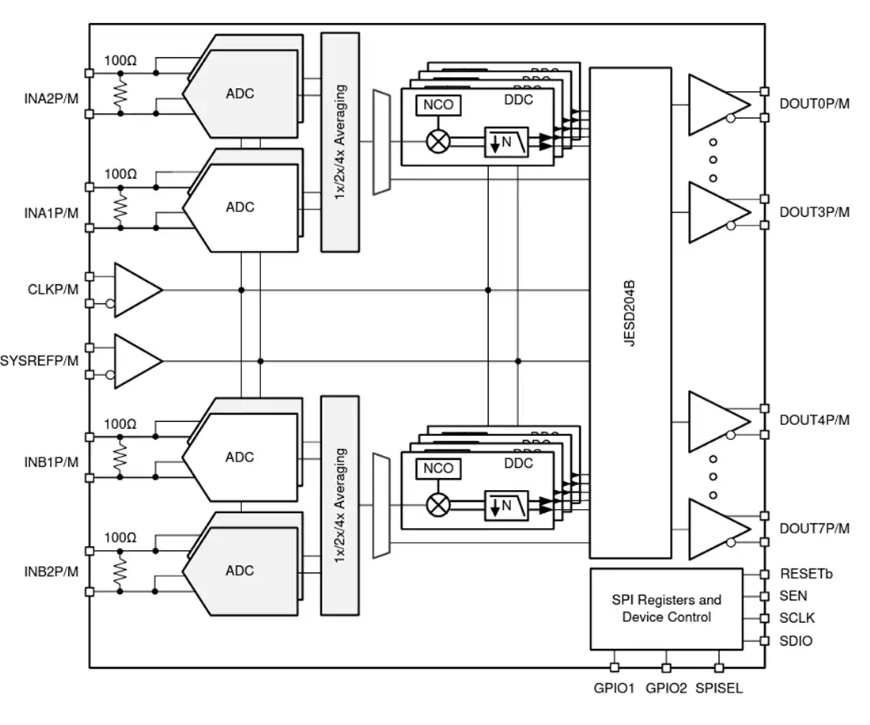

数字平均模式

提供数字平均模式(2x/4x AVG),可通过牺牲一定的功耗来进一步改善噪声密度。在2x平均模式下,一个外部输入连接到INx1输入,两个ADC核心内部对输入信号进行平均;在4x平均模式下,信号需要外部分割并连接到INx1和INx2输入,四个ADC核心内部对信号进行平均。平均模式下,输出分辨率会增加到16位,以避免量化噪声限制。

编程与配置

GPIO引脚控制

可通过GPIO引脚执行多种命令,如JESD同步、NCO控制、快速过范围指示和校准冻结等。这种引脚控制方式使得设计师能够在不依赖SPI接口的情况下,实现对ADC的基本控制,提高了系统的灵活性和实时性。

SPI接口配置

主要通过SPI接口对设备进行配置和控制。SPI接口由SEN、SCLK和SDIO引脚组成,当SEN为低电平时,可实现数据的串行输入。通过SPI接口,可以对ADC的各种功能进行详细配置,如数字平均模式、DDC参数、JESD接口参数等。

寄存器映射

设备具有一系列内部寄存器,可通过SPI接口进行访问。这些寄存器涵盖了各种功能配置,如数字操作模式、JESD接口配置、SYSREF输入、校准设置等。通过合理配置这些寄存器,可以实现对ADC的精确控制,满足不同应用场景的需求。

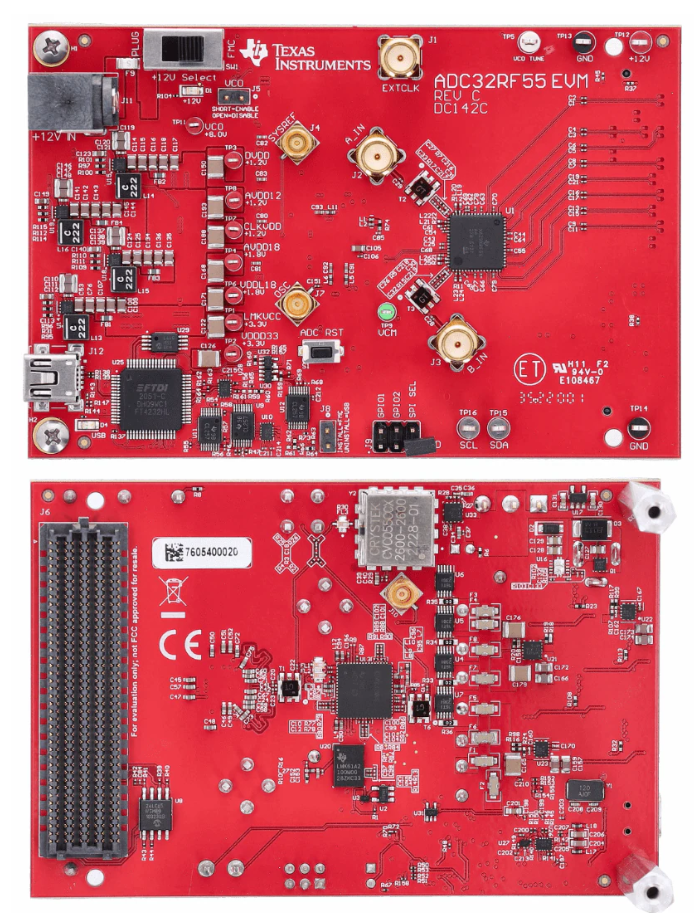

应用设计注意事项

输入信号路径

在设计输入信号路径时,应使用适当的带限滤波器来抑制接收信号路径中的不需要频率。需要使用1:2(对于100欧姆有效终端阻抗)或1:1(对于50欧姆有效终端阻抗)的巴伦变压器将单端RF输入转换为差分输入。巴伦输出应通过100 pF电容器进行AC耦合,并具有良好的幅度(<0.5 dB)和相位平衡(小于2度)。

时钟设计

设备时钟输入必须进行AC耦合,以提供额定性能。时钟源应具有低抖动(集成相位噪声),以确保ADC达到规定的SNR性能。在使用平均和/或抽取时,应首先估计单个ADC核心的SNR性能,然后再考虑内部平均和/或抽取带来的SNR改善。

电源供应

ADC需要四个不同的电源供应(AVDD18、AVDD12、CLKVDD和DVDD),电源排序至关重要。为了实现低噪声设计,建议使用高效降压开关稳压器,然后为每个电源轨使用低噪声LDO进行二次调节,以提供额外的开关噪声降低和提高电压精度。

布局设计

在电路板设计中,模拟输入和时钟信号的走线应尽可能短,避免使用过孔,以减少阻抗不连续性。数字JESD204B输出接口的走线应使用紧密耦合的100-Ω差分走线。电源和接地连接应提供低电阻路径,使用电源和接地平面代替走线,避免窄而孤立的路径增加连接电阻。

总结

ADC32RF54和ADC32RF55以其卓越的性能、丰富的功能和灵活的配置选项,为电子工程师提供了一个强大的信号处理解决方案。在实际应用中,工程师需要根据具体的应用需求,合理选择和配置ADC的各种参数,并注意输入信号路径、时钟设计、电源供应和布局设计等方面的问题,以充分发挥该ADC的性能优势。你在使用这款ADC的过程中,遇到过哪些挑战?又是如何解决的呢?欢迎在评论区分享你的经验。

发布评论请先 登录

RF采样:全新的采样速率数据转换器

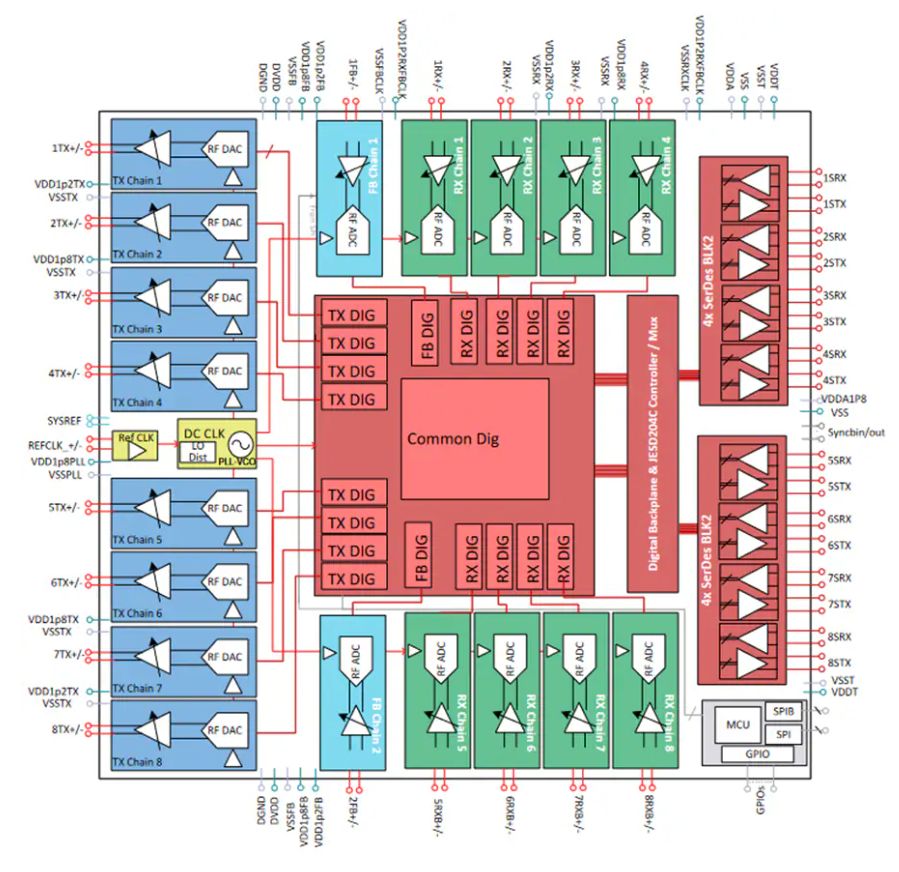

ADC34RF55四通道14位3GSPS射频采样数据转换器数据表

ADC08DJ5200RF射频采样千兆采样模数转换器(ADC)数据表

ADC32RF54双通道 14 位高速 RF 采样 ADC 技术总结

Texas Instruments ADC32RF54/55:高性能RF采样数据转换器的技术解析

Texas Instruments ADC32RF54/55:高性能RF采样数据转换器的技术解析

评论