7-Bit 0.25dB Digital Step Attenuator F1958:设计与应用全解析

在电子设计领域,对于基站(BTS)无线电卡等应用而言,数字步进衰减器(DSA)起着至关重要的作用。今天我们要深入探讨的是Renesas的F1958,一款7位0.25dB数字步进衰减器,它在1MHz至6GHz的频率范围内展现出卓越的性能。

文件下载:F1958NBGK8.pdf

一、产品概述

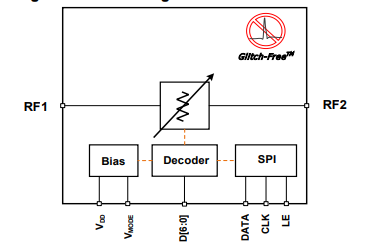

F1958属于Renesas Glitch - Free™系列DSA,专为满足基站无线电卡等严苛应用需求而优化。它采用紧凑的4 x 4 mm 24引脚封装,输入和输出阻抗均为50Ω,便于集成到无线电或射频系统中。

(一)高可靠性设计

该器件由QFN封装中的单片硅芯片构建而成,具有极高的可靠性。插入损耗极低,失真极小,并且能够实现极其精确的衰减水平。这些精确的衰减水平有助于提高系统的信噪比(SNR)和/或邻道泄漏比(ACLR),确保系统增益尽可能接近目标水平。

(二)快速切换特性

在并行模式下,F1958具有极快的建立时间,非常适合快速切换系统。此外,它采用了Renesas的Glitch - Free™技术,与其他竞争产品相比,能够在衰减状态转换期间保护功率放大器或ADC。

二、竞争优势

(一)低插入损耗

F1958拥有最低的插入损耗,能够为系统提供最佳的SNR,这对于对信号质量要求极高的应用来说至关重要。

(二)Glitch - Free™技术

该技术可有效保护功率放大器或ADC在衰减状态转换时不受损害,提高了系统的稳定性和可靠性。

(三)精确的衰减水平

极其精确的衰减水平能够确保系统增益的准确性,从而提高系统的整体性能。

(四)超低失真

超低的失真特性使得信号在传输过程中能够保持较高的质量,减少了信号的畸变。

(五)高ESD防护

具有MSL1和2000V HBM ESD防护能力,增强了器件在复杂环境下的抗干扰能力。

三、典型应用

F1958的应用场景十分广泛,包括但不限于以下几个方面:

(一)基站系统

在3G/4G/4G +基站系统中,F1958能够精确控制信号的衰减,确保信号的稳定传输。

(二)分布式天线系统(DAS)

在DAS中,它可以根据实际需求调整信号强度,优化信号覆盖范围。

(三)远程无线电头端

为远程无线电头端提供精确的信号衰减控制,提高通信质量。

(四)有源天线系统(AAS)和宽带卫星设备

在这些对信号精度要求极高的系统中,F1958能够发挥重要作用。

(五)NFC基础设施和军事通信设备

在NFC基础设施和军事通信设备中,其高可靠性和精确的衰减控制能力能够满足特殊环境下的通信需求。

四、产品特性

(一)接口灵活

支持串行和7位并行接口,用户可以根据实际需求选择合适的接口方式。

(二)宽衰减范围

具有31.75dB的衰减范围,且以0.25dB为步进,能够满足不同的衰减需求。

(三)快速建立时间

对于0.25dB步进,建立时间仅为500ns,能够实现快速的信号调整。

(四)低插入损耗

在4GHz时,插入损耗小于1.7dB,有效减少了信号的损失。

(五)高精度衰减

在4GHz时,衰减误差小于±0.2dB,确保了衰减的精确性。

(六)双向RF使用

支持双向RF使用,增加了器件的使用灵活性。

(七)宽电源范围

可使用3.3V或5V电源,适应不同的电源环境。

(八)宽工作温度范围

工作温度范围为 - 40°C至 + 105°C,能够在恶劣的环境条件下正常工作。

(九)紧凑封装

采用4 x 4 mm薄型24 - QFN封装,节省了电路板空间。

五、引脚分配与描述

(一)引脚分配

F1958的引脚分配清晰明确,不同的引脚承担着不同的功能。例如,D0 - D6为并行控制引脚,用于控制不同的衰减量;RF1和RF2为RF端口,可作为输入或输出端口;VDD为电源输入引脚等。

(二)引脚描述

每个引脚都有详细的描述,如D0引脚为0.25dB的并行控制引脚,拉高该引脚可实现相应的衰减。同时,对于一些关键引脚,如VDD引脚,需要使用电容器尽可能靠近引脚接地,以减少电源噪声。

六、电气特性

(一)绝对最大额定值

明确了器件在不同参数下的绝对最大额定值,如电源电压、控制引脚电压、RF端口电压、最大RF输入功率、结温等。超过这些额定值可能会导致器件永久性损坏,因此在设计过程中必须严格遵守。

(二)推荐工作条件

给出了器件的推荐工作条件,包括电源电压、工作温度范围、RF频率范围、最大输入功率等。在这些条件下使用器件,能够确保其性能的稳定性和可靠性。

(三)电气特性详细参数

涵盖了逻辑输入高电平、逻辑输入低电平、逻辑电流、插入损耗、相对相位、步进误差、绝对衰减误差、端口回波损耗、输入IP3、输入0.1dB压缩点等多个方面的详细参数。这些参数是评估器件性能的重要依据,工程师在设计时需要根据实际需求进行综合考虑。

七、编程模式

(一)串行模式

通过将VMODE引脚拉高至逻辑高电平来选择串行模式。串行接口使用8位字,但仅使用其中的7位,数据以LSB(D0)先移入的方式进行传输。在串行编程时,所有并行控制输入引脚必须接地。

(二)并行控制模式

用户可以选择直接并行模式或锁存并行模式。

- 直接并行模式:当VMODE引脚浮空或为逻辑低电平,且LE引脚为逻辑高电平时,选择直接并行模式。在该模式下,器件会立即对并行控制引脚的电压变化做出反应,适用于需要快速建立时间的应用。

- 锁存并行模式:当VMODE引脚浮空或为逻辑低电平,且LE引脚从逻辑低电平切换到逻辑高电平时,选择锁存并行模式。在该模式下,需要先设置好并行控制引脚的电压,然后将LE引脚拉高,器件才会转换到相应的衰减设置。

八、评估套件

(一)套件组成

评估套件包含了评估F1958所需的各种组件,如开关、连接器、电容器、电阻器等。通过评估套件,用户可以方便地对器件进行测试和验证。

(二)操作步骤

评估套件的操作步骤包括电源供应设置、并行逻辑控制设置、串行逻辑控制设置、上电和下电程序等。在操作过程中,需要严格按照步骤进行,以确保测试结果的准确性。

九、应用信息

(一)数字引脚电压和电阻值

明确了各个控制引脚的开路直流电压和内部连接情况,为工程师在设计电路时提供了重要的参考。

(二)电源供应

建议使用公共电源为所有需要直流电源的引脚供电,并使用外部电容器对电源引脚进行旁路,以减少噪声和快速瞬变。同时,对电源电压的变化率和控制引脚的电压范围也有相应的要求。

(三)控制引脚接口

当控制信号的完整性成为问题时,推荐在每个控制引脚的输入处使用特定的电路,以确保信号的稳定性。

十、订购信息

提供了不同型号的订购信息,包括封装形式、MSL评级、运输包装和温度范围等。工程师可以根据实际需求选择合适的型号。

F1958数字步进衰减器凭借其卓越的性能、灵活的接口和广泛的应用场景,为电子工程师在设计射频系统时提供了一个优秀的选择。在实际应用中,工程师需要根据具体的需求和设计要求,充分发挥其优势,确保系统的性能和可靠性。你在使用数字步进衰减器时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

产品特性

+关注

关注

0文章

87浏览量

941

发布评论请先 登录

基于RFSA2644下的SERIAL CONTROLLED DIGITAL STEP ATTENUATOR 50MHz TO 4000MHz 6-BIT 0.5dB LSB

基于RFSA3715下的5MHz to 4000MHz Digital Step Attenuator

基于RFSA3714下的50MHz to 6000MHz Digital Step Attenuator

基于RFSA3713下的5MHz to 6000MHz Digital Step Attenuator

基于RFSA3613下的5MHz to 6000MHz Digital Step Attenuator

基于RFSA2724下的Serial Controlled Digital Step Attenuator 50MHz to 4000MHz

基于RFSA3523下的5MHz to 6000MHz Digital Step Attenuator

基于RFSA2534下的50 MHz to 4000 MHz Digital Step Attenuator

基于QPC6713下的50MHz to 6000MHz Digital Step Attenuator

基于RFSA3623下的5MHz to 6000MHz Digital Step Attenuator

基于RFSA2524下的SERIAL CONTROLLED DIGITAL STEP ATTENUATOR 50MHz TO 4000MHz 5-BIT 1dB LSB

7位0.25dB数字步进衰减器F1958:特性与应用解析

7-Bit 0.25dB Digital Step Attenuator F1958:设计与应用全解析

7-Bit 0.25dB Digital Step Attenuator F1958:设计与应用全解析

评论