深入剖析SN74AC138-Q1:3 - 8解码器的设计与应用指南

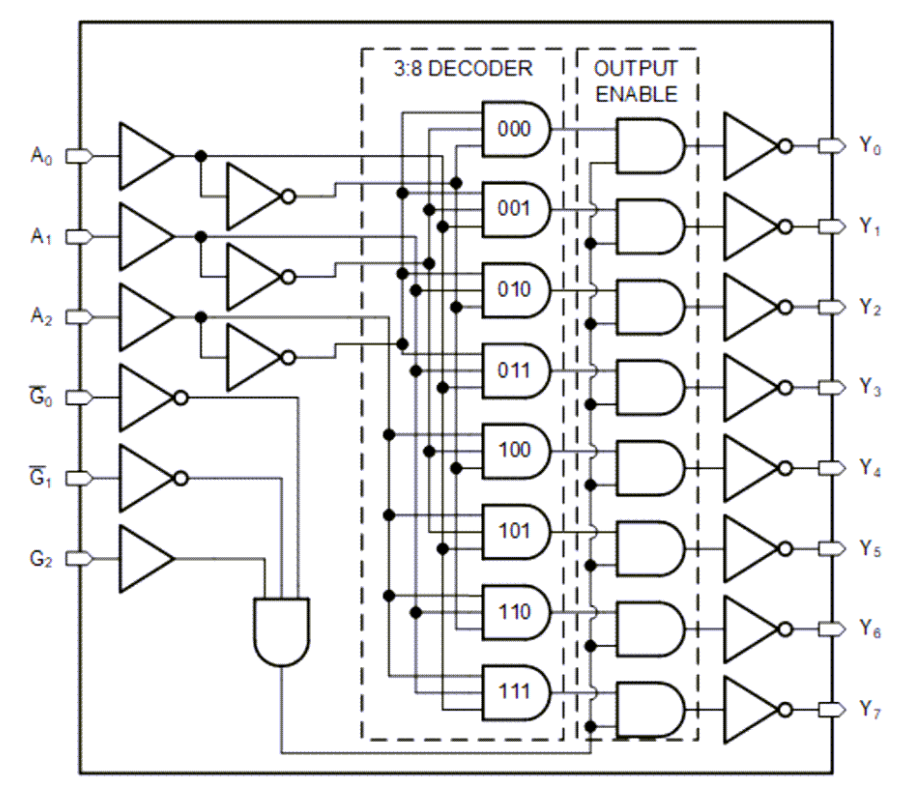

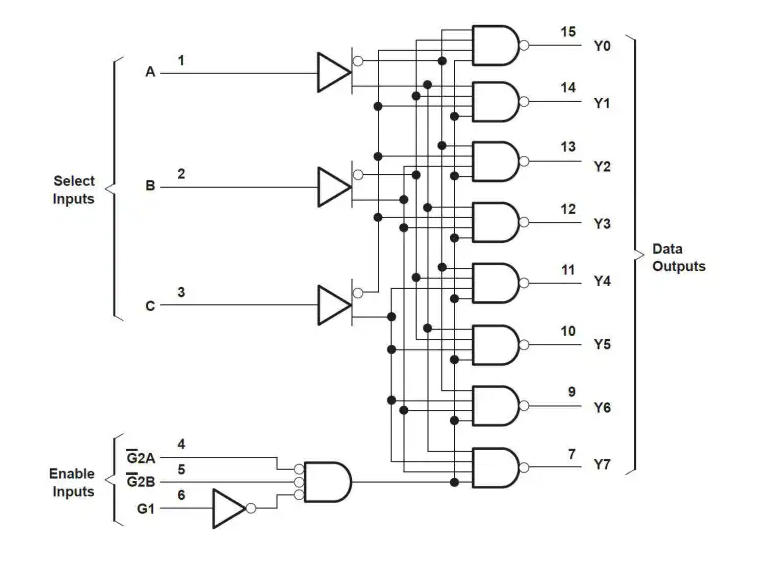

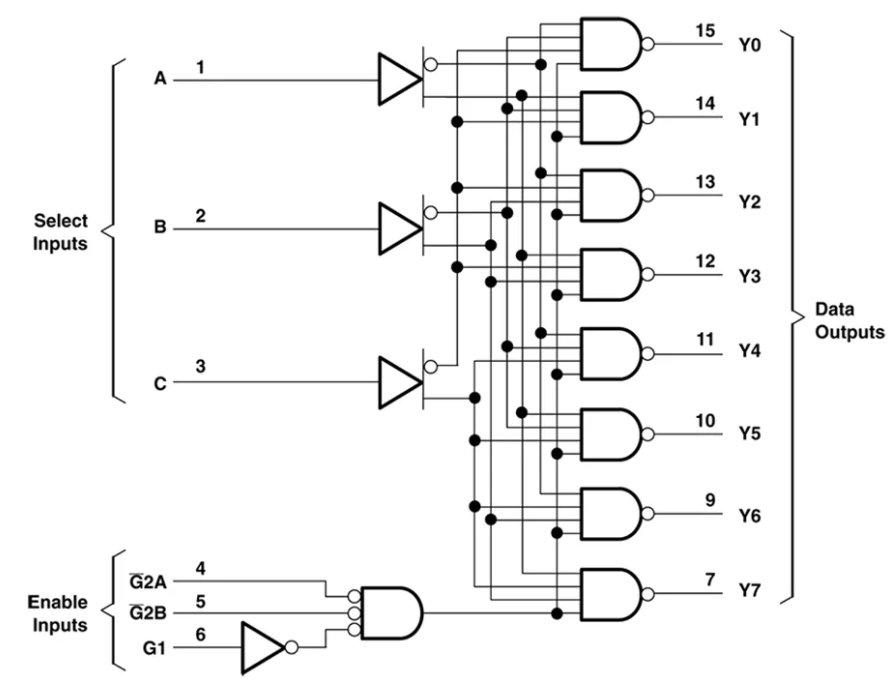

在电子设计领域,解码器是一种常见且重要的逻辑器件,它能够将输入的二进制代码转换为特定的输出信号。今天我们要深入探讨的是德州仪器(TI)的SN74AC138 - Q1,一款3 - 8解码器/解复用器,它在众多电子系统中发挥着关键作用。

文件下载:sn74ac138-q1.pdf

一、规格参数

1. 绝对最大额定值

绝对最大额定值规定了器件在不被永久损坏的前提下能够承受的最大应力。例如,电源电压范围(VCC)为 - 0.5V至7V,输入和输出电压范围(VI和VO)为 - 0.5V至VCC + 0.5V。需要特别注意的是,超出这些额定值可能会导致器件永久性损坏,即使短暂超出推荐工作条件,也可能影响器件的可靠性、功能性和寿命。

| 参数 | 描述 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| VCC | 电源电压范围 | -0.5 | 7 | V |

| VI | 输入电压范围 | -0.5 | VCC + 0.5V | V |

| VO | 输出电压范围 | -0.5 | VCC + 0.5V | V |

| ...... | ...... | ...... | ...... | ...... |

2. ESD额定值

静电放电(ESD)是电子器件的一大潜在威胁,SN74AC138 - Q1在这方面有明确的额定值。人体模型(HBM)下为±2000V(AEC Q100 - 002标准,HBM ESD分类等级2),带电设备模型(CDM)下为±1000V(AEC Q100 - 011标准,CDM ESD分类等级C4B)。在实际操作中,必须采取适当的静电防护措施,以避免ESD对器件造成损害。

3. 推荐工作条件

推荐工作条件是确保器件正常、稳定工作的参数范围。电源电压(VCC)推荐范围为1.5V至6V,不同的VCC对应着不同的高、低电平输入电压要求。例如,当VCC = 1.5V时,高电平输入电压(VIH)最小值为1.2V,低电平输入电压(VIL)最大值为0.3V。在设计电路时,务必使器件工作在这些推荐条件下。

二、器件特性

1. 平衡CMOS推挽输出

SN74AC138 - Q1采用平衡CMOS推挽输出结构,意味着器件能够吸收和提供相似的电流。这种输出结构在驱动轻负载时能够产生快速的边沿,但同时也可能会引发振铃现象。因此,在设计电路板时,需要充分考虑布线和负载条件,避免出现振铃问题。此外,要严格控制输出功率,防止因过流而损坏器件,必须始终遵循绝对最大额定值中定义的电气和热限制。

2. 标准CMOS输入

标准CMOS输入具有高阻抗的特点,通常可以用一个电阻与输入电容并联的模型来表示。在计算最坏情况下的电阻时,可以使用绝对最大额定值中的最大输入电压和电气特性中的最大输入泄漏电流,通过欧姆定律(R = V ÷ I)来计算。需要注意的是,输入信号必须快速在有效逻辑状态之间转换,否则会导致功耗过大甚至引发振荡。在实际应用中,绝对不要让标准CMOS输入处于浮空状态,未使用的输入必须连接到VCC或GND。

3. 可焊侧翼

部分封装的SN74AC138 - Q1具备可焊侧翼,这种设计有助于提高焊接后的侧面润湿性,使得QFN封装在自动光学检测(AOI)中更易于检查。可焊侧翼可以是凹陷或阶梯状的,为焊料提供了额外的附着面积,从而可靠地形成侧面焊脚。

4. 钳位二极管结构

器件的输入和输出都配备了正负极钳位二极管。然而,需要特别注意的是,电压超过绝对最大额定值表中规定的值可能会损坏器件。在满足输入和输出钳位电流额定值的前提下,输入和输出电压额定值可以适当超出。

三、功能模式

| SN74AC138 - Q1的功能模式由三个使能输入和三个二进制选择输入共同决定。通过这些输入的不同组合,可以选择八个输出线中的一个,被选中的输出线为低电平,其余输出线为高电平。具体的功能表如下: | 输入(G2、G1、G0、A2、A1、A0) | 输出(Y0 - Y7) |

|---|---|---|

| X X H X X X | H H H H H H H H | |

| L X X X X X | H H H H H H H H | |

| X H X X X X | H H H H H H H H | |

| H L L L L L | L H H H H H H H | |

| ...... | ...... |

四、应用与实现

1. 典型应用示例

在一个使用5位输入选择32个输出中的1个的应用中,可以使用四个SN74AC138 - Q1 3 - 8解码器。此时,需要一个外部反相器来完成整个电路。被选中的输出为低电平,其余输出为高电平。

2. 设计要求

- 电源考虑:确保所需的电源电压在推荐工作条件规定的范围内,电源电压决定了器件的电气特性。正电压电源必须能够提供足够的电流,包括所有输出所需的总电流、最大静态电源电流(ICC)以及开关所需的瞬态电流。同时,要注意器件的功耗和热增加,可以参考相关的应用报告进行计算。

- 输入考虑:输入信号必须超过VIL(max)才能被视为逻辑低电平,超过VIH(min)才能被视为逻辑高电平,且不能超过绝对最大额定值中的最大输入电压范围。未使用的输入必须连接到VCC或地,推挽输出不能直接连接在一起,以免产生过大电流损坏器件。

3. 详细设计步骤

- 添加去耦电容:从VCC到GND添加一个去耦电容,电容应尽可能靠近器件,并且在电气上靠近VCC和GND引脚。

- 控制输出电容负载:确保输出的电容负载 ≤ 50pF,可通过提供短而合适尺寸的走线来实现。

- 控制输出电阻负载:确保输出的电阻负载大于(VCC / IO(max))Ω,以防止违反绝对最大额定值中的最大输出电流。

- 考虑热问题:虽然逻辑门的热问题通常不是主要关注点,但可以使用相关应用报告中的步骤来计算功耗和热增加。

4. 电源供应建议

电源电压可以在推荐工作条件规定的最小和最大电源电压额定值之间选择。在启动时,电源应在规定的上电斜坡速率范围内上升。每个VCC端子都应配备一个良好的旁路电容,对于SN74AC138Q1,建议使用0.1μF的旁路电容,为了抑制不同频率的噪声,可以并联多个旁路电容。

5. 布局指南

- 旁路电容放置:旁路电容应靠近器件的正电源端子,提供电气上短的接地返回路径,使用宽走线以最小化阻抗,并尽量将器件、电容和走线放置在电路板的同一侧。

- 信号走线几何形状:信号走线宽度为8mil至12mil,长度小于12cm以最小化传输线效应,避免信号走线出现90°角,在信号走线下方使用完整的接地平面,并对信号走线周围的区域进行填充。对于长度超过12cm的走线,使用阻抗控制走线,在输出附近使用串联阻尼电阻进行源端匹配,避免分支走线,如果必须分支,应单独缓冲信号。

总结

SN74AC138 - Q1作为一款功能强大的3 - 8解码器/解复用器,在电子设计中具有广泛的应用前景。通过深入了解其规格参数、器件特性、功能模式以及应用实现方法,电子工程师可以更好地利用这款器件,设计出更加稳定、可靠的电子系统。在实际设计过程中,务必严格遵循器件的各项参数和设计指南,以确保系统的性能和可靠性。你在使用类似解码器的过程中遇到过哪些问题呢?欢迎在评论区分享你的经验。

-

电子设计

+关注

关注

42文章

2935浏览量

49917

发布评论请先 登录

Texas Instruments SN74AC138-Q1 3线至8线反相解码器/解复用器数据手册

Texas Instruments SN74AHCT138/SN74AHCT138Q-Q1解复用器/解码器数据手册

Texas Instruments SN74AHC138/SN74AHC138-Q1 3线至8线解码器/解复用器数据手册

深入剖析SN74AC138 - Q1:3 - 8解码器的设计与应用指南

深入剖析SN74AC138 - Q1:3 - 8解码器的设计与应用指南

评论