传统的数据采集系统一般采用单片机,系统大多通过PCI总线完成数据的传输。其缺点是数学运算能力差;受限于计算机插槽数量和中断资源;不便于连接与安装;易受机箱内电磁环境的影响。这些问题遏制了基于PCI总线的数据采集系统的进一步开发和应用。因此,需要一种更为简便通用的方式完成采集系统和计算机数据的交互。

数据采集系统性能的好坏,主要取决于它的精度和速度。在保证精度的条件下应尽可能地提高采样速度,以满足实时采集、实时处理和实时控制的要求。实践表明,采用ARM 32位嵌入式微处理器作为控制器,用USB(通用串行总线)和上位机连接构成的数据采集系统能大大提高系统数据处理的能力,降低对PC机和接口速度的依赖。

1 系统硬件设计

实现系统功能的基本思路是:以CPLD/FPGA实现仪器的数字平台,和ARM嵌入式处理器及单片机一起实现对整机的智能控制和高速的数据处理。

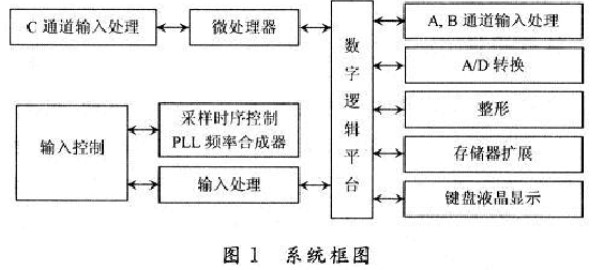

1.1 系统框图

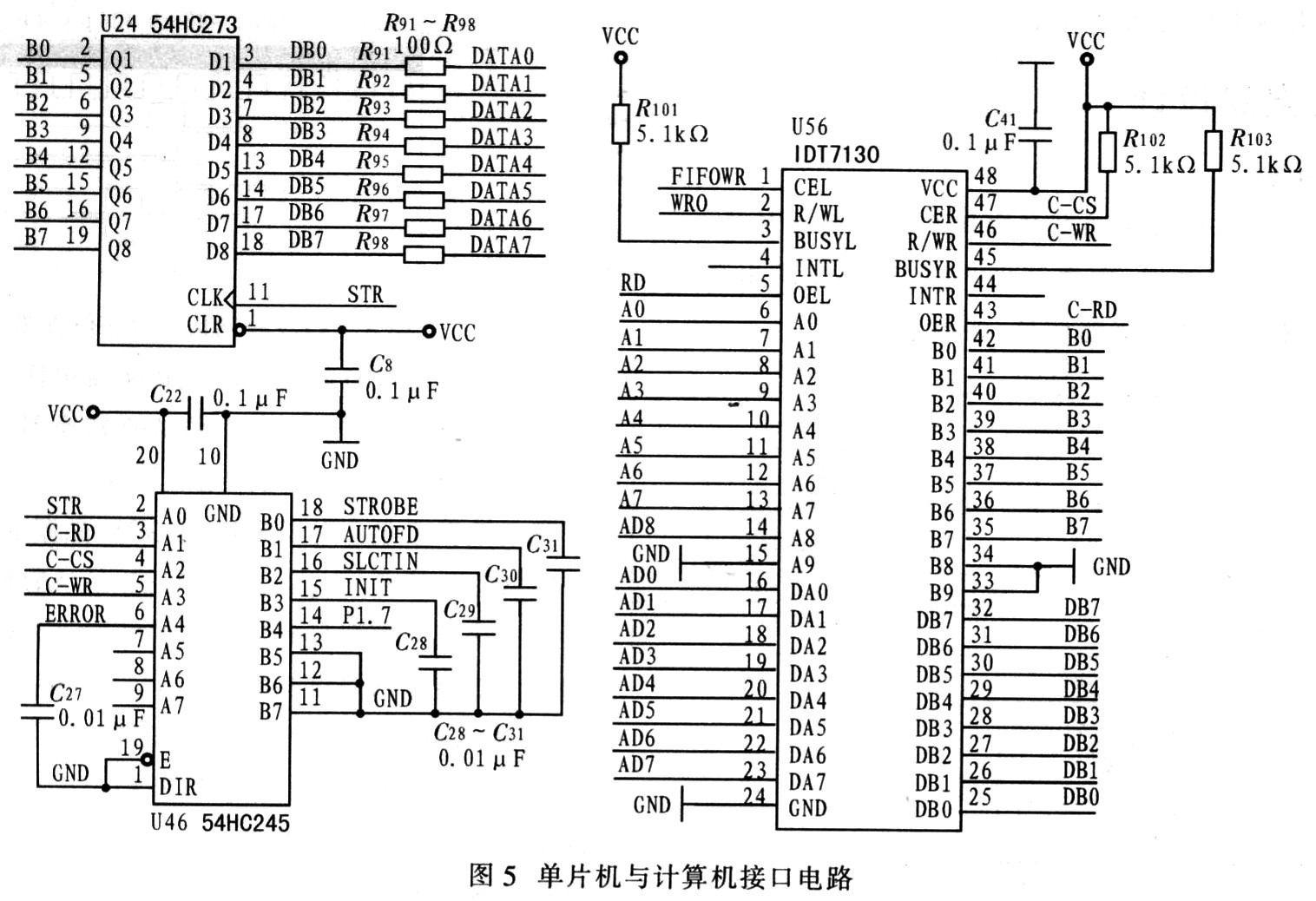

系统原理方框图如图1所示,该系统主要由微处理器、数字逻辑平台、输入控制、A,B通道输入处理、C通道输入处理、整形、A/D转换、采样时序控制、键盘液晶显示、存储器扩展等模块构成。

1.2 系统结构图

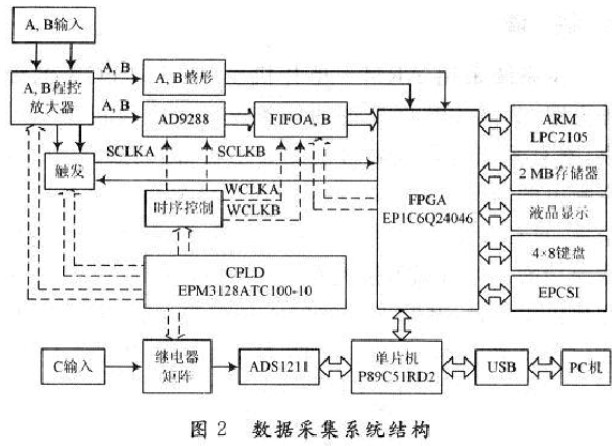

系统硬件如图2所示,利用一片规模较小的CPLD和一片规模较大的FPGA组合构成系统的数字逻辑平台。CPLD主要用作输入控制,FPGA则连接了系统的其他各个部分。CPLD/FPGA可实现现场编程,使用CPLD/FPGA可使设计方便,利用它灵活、校验快以及设计可随意改变的特点,可大大缩短研制时间。

1.3 主要部分功能

1.3.1 微处理器

系统采用由Philips公司生产的ARM 32位微处理器LPC2105作为主CPU,进行高速的数据处理,用8位单片机P89C51RD2作为辅CPU,进行速度较慢的数据处理,控制其他外围芯片和模块实现A,B通道模拟带宽100 MHz、峰值电压±100 V和C通道二极管通断、电压、电流、电阻值的数据采集功能。

1.3.2 A,B通道部分

通过自动增益电路(AGC)即程序控制放大器,将被测模拟信号调理到适合ADC芯片(AD9288)采样的范围。根据频率的大小和触发方式,运用实时采样或等效采样对调理后的模拟信号进行采样(A/D转换)。利用高速FIFO存贮器(IDT72V261LAl0A)存储采样后得到的数据。

结合键盘操作和系统设置,对采样后的数据进行数学运算,将还原后的波形数据和参数送液晶显示器显示或存入闪存里面或通过USB接口传送给PC机,从而实现了A,B通道高速数据采集的功能。

1.3.3 C通道部分

C输入通道为多功能输入通道,系统通过控制继电器矩阵来选择不同的模块测量电压、电流或二极管的通断和电阻。被测元件参数或电压、电流经过多功能转换电路处理后,其信号送24 b的A/D转换器ADS1211采样后送单片机P89C51RD2,分析被测元件或电压、电流的参数值,从而实现了C通道高精度数据采集的功能。

1.3.4 键盘、液晶显示接口电路

本系统采用4×8的键盘和320×240不带驱动器的液晶显示模块,驱动器和显存设计在FPGA内。以上系统通过USB接口与PC机通信,在上位机的控制下,实现可视化人机交互界面。同时系统也保留了传统的RS 232接口,但只是用于ARM和单片机的编程下载。

2 软件设计流程

LPC2105芯片作为系统主控制中心及数据处理中心,整个系统的运转受到它的控制,例如响应用户的按键操作,发出通道控制,A/D采样时钟控制,FIFO写时钟的选择,菜单及系统状态显示,FIFO数据的处理,信号或参数的自动测试等。

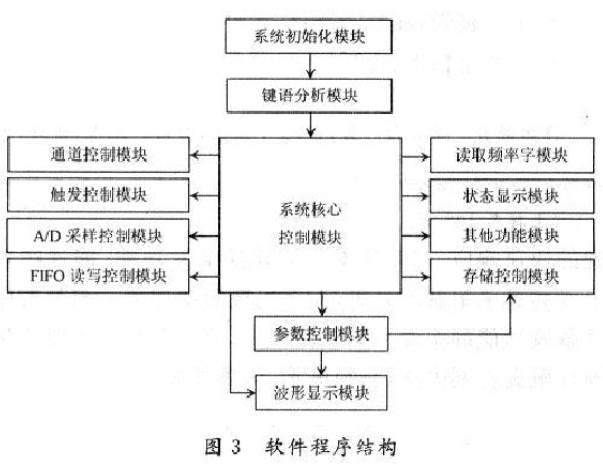

数据采集卡的软件程序结构如图3所示,可分为系统初始化模块、键语分析模块、系统核心控制模块、通道控制模块、触发控制模块、A/D采样控制模块、FIFO读写控制模块、读取频率字模块、参数测试模块、状态显示模块、波形显示模块、存储控制模块、其他功能模块。

系统的初始化模块包括开机自检、硬件参数初始化、系统状态初始化(如通道的波形显示状态初始化)等。键语分析模块对面板上的用户输入进行分析处理,通过核心控制模块调用相应的功能处理模块,通过对通道控制模块、触发控制模块、A/D采样控制模块、FIFO读写控制模块、读取频率字模块、参数测试模块、状态显示模块、波形显示模块、存储控制模块、其他功能模块的函数调用来实现对来自键语分析的处理功能。状态显示模块显示程序运行时的各种状态,如当前数据采集的扫描速率、通道的垂直灵敏度等。波形显示模块显示采集的波形。

整个系统的程序又可分成底层驱动和上层软件。底层驱动指对本系统其他外设或器件直接控制或访问的程序部分,包括LPC2105和单片机的初始化(即对片内各核心寄存器的操作赋值、对片上外设的初始化赋值、对片内各外设中断及外部中断的控制操作)。上层软件主要指:菜单的设计及显示、数据的处理、波形的恢复及平滑等。

3 系统性能指标

3.1 A,B通道的性能指标

(1)模拟信号带宽:100 MHz(40 dB);

(2)最高实时采样率:100.MS/s;

(3)最高等效采样率:5 GS/s;

(4)垂直分辨率:8 b;

(5)垂直灵敏度:5 mV/div~25 V/diV;

(6)水平扫描:5 ns/div~10 s/diV;

(8)输入RC:1 MΩ±1.5%/20 pF±3 pF;

(9)耦合方式:直流、交流、接地;

(10)触发模式:交流、直流、高频抑制、低频抑制;

(11)触发源:A,B;

(12)存储深度:16K/通道;

(13)显示模式:A,-A,B,-B,A-B,A+B;

(14)测量信号参数:周期、频率、平均值、有效值、峰值、均方根值、最小值、最大值、上升时间、下降时、正频宽、负频宽、占空比;

(15)测量精度:±5%;

(16)校准信号:1 kHz/3.3 V。

2 C通道性能指标

(1)测量电阻:100 Ω,1 kΩ,10 kΩ,100 kΩ,1 MΩ;

(2)测量电压:10 mV,30 mV,1 V,3 V,lO V,V:

(3)测量电流:200 mA,1 A;

(4)二极管:通断测量;

(5)测量精度:±3%。

4 结 谙

本系统采用ARM+单片机+CPLD/FPGA的设计方案,其高速数据处理的任务可以由下位机独立完成,并且系统带有大屏幕液晶显示器,因而脱离PC机在断电的情况下也可以正常使用。该采集卡具备实时采集、自动存储、即时显示、即时反馈、自动处理、自动传输等功能。为现场数据的真实性、有效性、即时性、可用性提供了保证,并能方便地输入计算机,可以应用于智能仪器仪表、工业、农业、商业、交通、物流、仓储等行业。

-

FPGA

+关注

关注

1664文章

22502浏览量

639148 -

单片机

+关注

关注

6078文章

45579浏览量

673561 -

cpld

+关注

关注

32文章

1259浏览量

174162

发布评论请先 登录

基于单片机的数据采集系统设计

基于ARM+μC/OS-II的嵌入式数据采集系统设计

基于VB与单片机串行通信的数据采集系统设计

单片机系统中高速数据采集的实现

基于CPLD的高速数据采集系统的实现

使用单片机进行多路数据采集系统设计的详细资料说明

基于CPLD器件和ARM+单片机实现数据采集系统的设计

基于CPLD器件和ARM+单片机实现数据采集系统的设计

评论