工程师辛辛苦苦画完板,打样回来却发现焊接不上、虚焊、或者板子直接“变板砖”。

一个好的硬件产品,不仅需要优秀的电路设计,更需要完美的物理实现(SMT/PCBA)。

第一部分:PCB设计阶段的“隐形杀手”

QFN封装的“虚焊”迷局

背景:

一款物联网通讯模块,核心芯片采用了一个48引脚的QFN封装芯片。客户反馈首批试产100片中,有近20片无法正常启动,表现为电源电流异常,时好时坏。

问题现象:

外观目检和X-Ray检测均未发现明显短路或缺件。但在功能测试架上,表现为通讯不稳定或无法上电。

排查过程:

1. 功能复测: 将不良品在显微镜下观察,发现QFN芯片底部的接地(GND)散热焊盘位置,有部分引脚呈现灰暗色,疑似未完全熔融。

2. 剖片分析(切片): 对不良品进行切片分析,证实了GND焊盘下的多个引脚存在虚焊(冷焊)。

3. 根本原因(PCB与钢网设计双重失误):

PCB设计: 客户在设计时,为了“散热更好”,将QFN芯片底部的中心散热焊盘设计得比芯片本体还要大,导致该大焊盘与周围信号引脚的间距过近。

钢网设计(Stencil): 钢网开孔时,没有对中心散热焊盘进行适当的“内缩”或“网格化”处理,导致印刷时锡膏量过多。

综合后果: 过多的锡膏在回流焊熔融时,由于表面张力和重力作用,将周围的信号引脚“拉”向中心,导致部分引脚与焊盘错位,或者锡膏溢出造成隐性短路/虚焊。

解决:

1. 修改PCB: 调整中心散热焊盘尺寸,确保与周围引脚有足够的安全间距。

2. 优化钢网: 对中心焊盘进行“棋盘格”开孔,减少锡膏印刷量。

3. 调整炉温: 适当延长回流焊的预热区时间,使助焊剂充分挥发。

干货

一、IC引脚间距与PCB布线的配合

1. 焊盘尺寸设计原则

遵循IPC标准:推荐依据 IPC-7351《表面贴装焊盘图形标准》进行焊盘设计。

引脚间距(Pitch)决定焊盘宽度和长度:

对于 QFP、SOIC、TSSOP 等封装,引脚间距常见有 1.27mm、0.8mm、0.65mm、0.5mm、0.4mm 等。

焊盘宽度通常略小于引脚宽度(约小0.05~0.1mm),以防止桥接。

焊盘长度需保证足够的焊接面积,一般为引脚长度 +(0.2~0.5mm)。

细间距器件(Fine Pitch < 0.5mm):

建议采用 NSMD(Non-Solder Mask Defined)焊盘,即阻焊开窗大于铜焊盘,便于控制焊锡量。

需使用高精度制程(如激光钻孔、精细线路),最小线宽/线距建议 ≥ 3mil(0.076mm)。

2. 布线配合要求

引出走线方向:从焊盘内侧引出,避免从外侧“拉线”,防止焊接时锡膏被拉偏。

走线宽度:在密集引脚区域,若无法满足标准线宽,可局部缩窄(但需满足电流承载要求)。

泪滴(Teardrop)处理:在焊盘与走线连接处添加泪滴,增强机械强度并改善信号完整性。

阻抗控制:高速信号线需考虑参考平面、线宽、介质厚度等,确保阻抗匹配。

3. 阻焊层(Solder Mask)设计

阻焊开窗应比焊盘大 0.05~0.1mm(单边),避免覆盖焊盘导致虚焊。

相邻焊盘间必须有阻焊桥(Solder Mask Dam),尤其在细间距器件中,防止锡桥。

最小阻焊桥建议 ≥ 0.1mm(4mil),部分高端工艺可达 0.075mm。

二、Mark点(Fiducial Mark)的设置对SMT贴片精度的重要性

1. Mark点的作用

为SMT贴片机提供视觉定位基准,用于校正PCB的放置偏差(X/Y偏移、旋转、缩放)。

提高贴片精度,尤其对 高密度、细间距、BGA/QFN 等元件至关重要。

2. Mark点设计规范

形状与尺寸:

推荐圆形或方形实心铜箔,直径/边长通常为 1.0mm 或 1.5mm。

表面需裸露(无阻焊、无丝印),并做表面处理(如OSP、ENIG)以增强反光一致性。

周围空白区(Clearance):

Mark点周围至少 ≥ 直径大小的空白区域(如1.5mm Mark点,周围留空 ≥ 1.5mm),无铜箔、走线、过孔、丝印等干扰。

数量与位置:

全局Mark点(Global Fiducial):每块PCB至少设 2~3个,呈非对称分布(如L形),位于板边或拼板边缘。

局部Mark点(Local Fiducial):对 BGA、QFP、CSP 等高精度元件,建议在其附近(≤ 5mm)设置1~2个局部Mark点。

拼板(Panel)设计:

每个子板(Individual PCB)应有自己的Mark点;

整个拼板也需设置全局Mark点,便于整板定位。

3. 注意事项

避免将Mark点放在V-Cut槽、邮票孔附近,以免加工变形影响识别。

不同供应商设备对Mark点识别能力略有差异,建议提前与SMT厂商确认其设备要求。

总结

焊盘设计需兼顾电气性能、可焊性与防缺陷(如桥接、虚焊);

Mark点是SMT自动贴装精度的“眼睛”,合理布局可显著提升良率;

始终结合 具体封装数据手册 + PCB制造商/SMT厂工艺能力 进行设计验证。

设计阶段就考虑生产工艺,能省下大笔改板和维修的成本。

好了下期继续

审核编辑 黄宇

-

pcb

+关注

关注

4415文章

23955浏览量

426009 -

smt

+关注

关注

45文章

3210浏览量

77015

发布评论请先 登录

电感选型避坑指南:从共模到功率,硬件工程师必须掌握的核心参数

《PCB打样/SMT贴片避坑指南!工程师必看,少走弯路》

PCB设计避坑指南——孔/槽篇

如何选择靠谱的PCB/SMT/PCBA厂家?2025年全流程避坑指南与优质厂商推荐

分享一个驱动开发工程师学习路线图

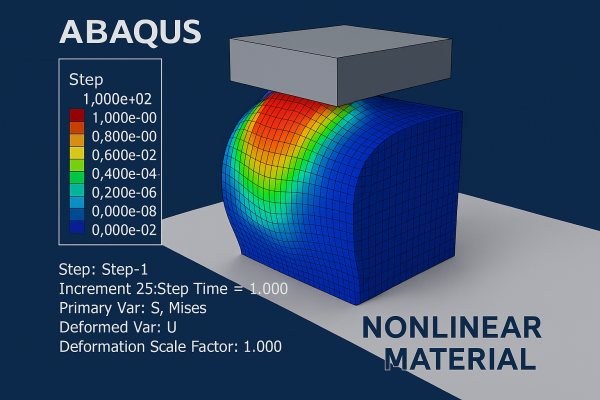

从线性到非线性:工程师必须掌握的Abaqus三大非线性来源

从“烧板”到一次成功:硬件工程师必须掌握的PCB设计与SMT工艺避坑指南

从“烧板”到一次成功:硬件工程师必须掌握的PCB设计与SMT工艺避坑指南

评论