Synopsys ARC-V 处理器中的高级指令融合引入了一种新型机制,用于融合常见的 RISC-V 指令对,旨在提高处理器流水线效率,特别是针对资源受限的嵌入式处理器。通过融合来自不同功能单元的指令, 它将单发射、顺序执行的处理器扩展为双指令发射。

重要的是,该机制并未引入新的指令,完全兼容 RISC-V 架构,并且对软件透明,确保与现有软件和硬件环境的无缝集成。通过减少流水线开销并简化指令处理,高级指令融合显著提升嵌入式处理的效率。

该方法还具备可适应的设计原则,可以从双指令融合扩展到多指令融合,从而惠及整个生态系统中的 RISC-V 处理器实现。

嵌入式 RISC-V 设计面临的挑战

随着嵌入式系统不断演进,设计人员面临在严格的功耗和成本限制下实现更高性能和日益异构的处理架构的挑战。这一转变部分源于边缘人工智能(Edge AI)的快速扩展,越来越多的工作负载被推向数据源附近,这要求更智能、更强大的嵌入式解决方案。

与此同时,开放标准的 RISC-V 架构正在获得广泛推动,尤其在微控制器单元(MCU)领域,其采用率和出货量处于领先地位。这些处理器必须在满足极端功耗、安全性和可靠性标准的同时,支持边缘复杂的工作负载。

RISC-V 指令集架构(ISA)设计为简洁且模块化,使用大量简单指令可以降低 CPU 功耗和面积。然而,这种指令冗余可能带来性能限制,因为复杂操作需要更多周期来完成。

虽然双发射、多发射以及乱序执行等技术可以提升每周期指令数(IPC)和性能,但它们通常会增加面积需求,这对资源受限的嵌入式处理器来说是一个挑战。

指令融合是一项众所周知的技术,它利用可用的硬件资源来增加指令级并行性(ILP)。指令融合以最小的面积开销提升 ILP 和 CPU 性能,特别适用于在小型、顺序执行的处理器中提高性能密度。

本文描述了一种新颖的高级指令融合技术,用于在微架构层面融合成对的 RISC-V 指令。该技术在避免引入单独的流水线的前提下,实现了双发射处理器的主要效率优势,同时保持 RISC-V 兼容性。

什么是高级指令融合?

架构级融合 vs 微架构级融合

某些指令集在架构级别融合指令,另一些指令集则在微架构/实现层面进行指令融合。典型示例包括加载/存储对以及带自动增量的加载/存储。在某些指令集(例如:ARM 和 ARC)中,这些在架构级别融合,即:这些操作由单条指令完成。其他指令集(例如:RISC-V)则采取不同的方法,保持架构指令简洁,将融合操作交由微架构实现。

微架构级融合相比架构级融合的主要优势包括:

微架构级融合能够实现更激进的优化,例如即使内存地址不连续也可以融合加载指令对

不同 ISA 之间的二进制兼容性更易维护,因为简单或小型处理器无需实现指令融合

在微架构级别实现融合要求处理器具有足够的指令获取带宽。简单的 RISC ISA(例如:RISC-V)比较冗长,因此比在架构级别执行指令融合的 ISA 消耗更多指令获取带宽。

简单的顺序单发射处理器每周期的指令获取带宽通常不超过 4 字节。这对微架构融合构成了严重限制。大多数融合对需要 16 位压缩指令。因此,在资源受限的嵌入式处理器中利用微架构融合的第一步是增加其指令获取带宽。

实现细节

资源受限的 RISC-V 设计中的高级指令融合

传统的融合指令对不需要额外的寄存器文件读写带宽。与其他 RISC-V 指令一样,一个融合指令对最多从寄存器文件读取两个源操作数,并产生一个结果。

然而,某些融合指令对候选会打破这一规则:

加载双指令(Load-double):融合两个加载指令时,需要两个寄存器写端口

存储双指令(Store-double):融合两个存储指令时,需要三个寄存器读端口(存储指令有一个公共基地址,但每个存储指令需要独立的存储数据操作数)

乘加指令(MAC):融合乘法和加法时,需要三个寄存器文件读端口

要利用这些高级融合指令对(双加载、双存储和 MAC),需要额外的硬件资源。更具体地说:寄存器文件应能够提供三个源操作数,并增加第二个寄存器写端口。

高级指令融合技术增加了额外的硬件资源,并提高了其利用率。它通过利用微架构融合框架,在顺序执行处理器上实现了有限的双发射能力。采用这种方法,任何映射到不同的功能单元、最多需要三个源操作数、并且最多产生两个目标寄存器的两个独立的指令,都可以被视为高级融合(双发射)候选对。

这些指令在前端通过预解码的操作码和寄存器操作数标识符进行融合。预解码的寄存器操作数标识符用于检测高级融合指令对之间是否存在数据依赖关系。解码器被增强以接收融合指令的附加信息,但不会被复制。融合指令对中的每条指令被分发至对应的功能单元。处理器的后端指令融合基本无感,除了增加架构 PC 和处理由融合指令触发的异常之外,不需要引入单独的流水线。

图 1 展示了带有高级指令融合的 RISC-V 处理器前端的典型实现。一些示例包括以下指令对:LOAD+ALU、LOAD+BR、LOAD+MPY、ST+BR、ST+ALU。

性能结果

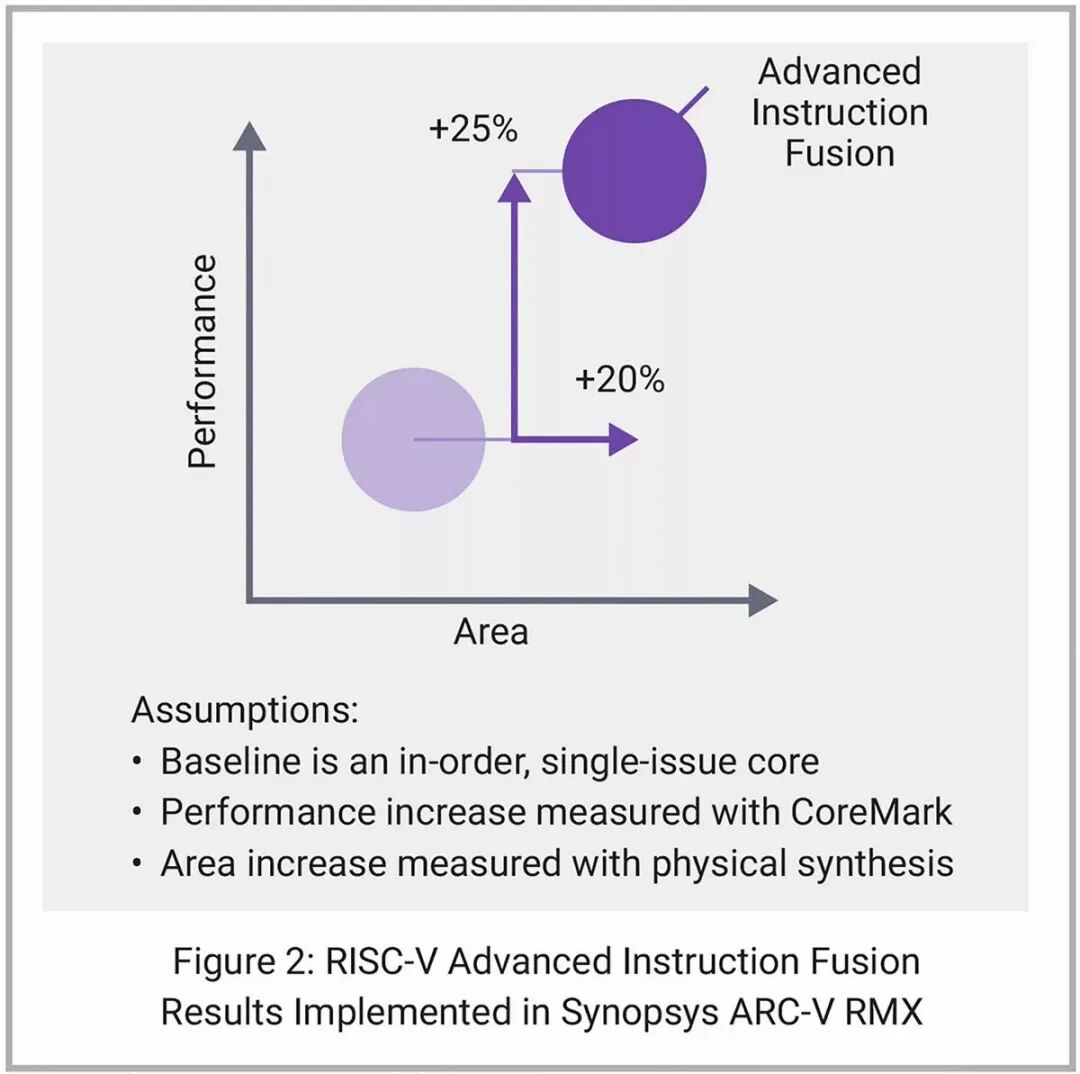

Pollack 定律指出,微架构增强带来的性能提升通常随复杂度增加的平方根增长。图 2 显示,对于 Synopsys ARC-V RMX(一款带有高级指令融合的 RISC-V 嵌入式处理器),测得的 CoreMark/MHz 表明其性能提升与硅面积呈线性关系,带来了更大的性能优势。此外,由于高级指令融合仅产生固定的面积开销,性能密度的提升也更加显著。

结论

高级指令融合为在资源受限的嵌入式系统中提供了一种有效提升处理器流水线效率的方法,其核心是融合常见的 RISC-V 指令对。该技术在不引入新指令或需要软件修改的前提下,通过在单发射、顺序执行处理器上实现来自不同功能单元的指令融合,完成双指令发射,实现了显著的性能提升,并完全兼容 RISC-V 架构。流水线开销降低和简化指令处理带来了显著的效率提升,同时这种可扩展的设计支持未来扩展到多指令融合。总体而言,高级指令融合为整个 RISC-V 生态系统中高效提升处理器性能提供了一种实用且可扩展的解决方案。

关键要点

理想的嵌入式系统设计:该技术专为面积和功耗受限的小型、顺序执行处理器设计,适用于无法采用传统多发射或乱序架构的场景。

无需更改 ISA 即可提升性能:高级指令融合在不引入新指令或破坏 RISC-V 兼容性的情况下,提高 IPC 和流水线效率。

微架构级融合优势:相比架构级融合,在微架构级别进行融合支持更灵活、更激进的优化策略。

硬件高效双发射:通过融合来自不同功能单元的指令,实现双指令发射,仅需适度增加硬件资源,如增加寄存器端口。

可扩展设计:融合框架具有适应性,可扩展支持多指令融合,推动在整个 RISC-V 生态系统中更广泛采用。

-

处理器

+关注

关注

68文章

20329浏览量

254858 -

嵌入式

+关注

关注

5209文章

20645浏览量

336923 -

指令

+关注

关注

1文章

624浏览量

37664 -

RISC-V

+关注

关注

49文章

2946浏览量

53535

原文标题:突破能效瓶颈:RISC-V 高级指令融合如何实现性能密度跃升

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集

rIsc-v的缺的是什么?

RISC-V指令集的特点总结

关于RISC-V芯片的应用学习总结

RISC-V B扩展介绍及实现

一文看懂RISC-V代码密度

优化的关键,RISC-V中的性能监控

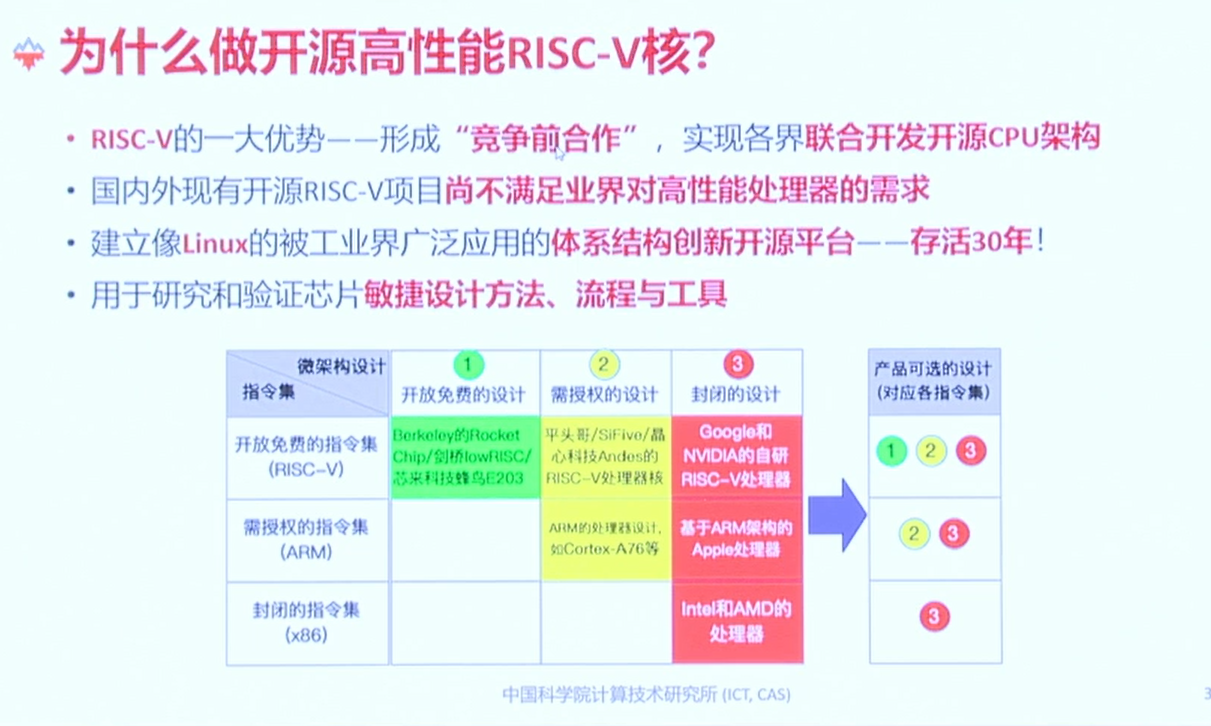

为什么做开源高性能RISC-v核,香山开源高性能RISC-V处理器开发流程

risc-v中国峰会直播:如何优化RISC-V指令集架构的代码密度?

第一届RISC-V中国峰会看点 risc-v开发要怎么优化risc-v指令集架构代码密度

RISC-V高级指令融合如何实现性能密度跃升

RISC-V高级指令融合如何实现性能密度跃升

评论