高性能 ISO/IEC 14443 A/B 前端 MFRC631 详细解析

引言

在当今的电子设备领域,近场通信(NFC)技术的应用愈发广泛,从移动支付到门禁系统,NFC 为我们的生活带来了极大的便利。NXP 推出的 MFRC631 作为一款高性能的 ISO/IEC 14443 A/B 前端芯片,在 NFC 应用中发挥着重要作用。本文将对 MFRC631 进行全面解析,涵盖其基本特性、功能模块、寄存器配置以及应用设计等方面,希望能为电子工程师们在实际设计中提供有价值的参考。

文件下载:MFRC63102HN,151.pdf

一、MFRC631 概述

MFRC631 是一款经济高效的 NFC 前端芯片,专为支付应用设计。它支持多种操作模式,包括 ISO/IEC 14443 类型 A 和 MIFARE Classic 通信模式的读写操作,以及 ISO/IEC 14443B 模式的读写操作。其内部发射器能够驱动与 ISO/IEC 14443A 和 MIFARE Classic IC 卡及应答器通信的读写器天线,无需额外的有源电路。数字模块则管理完整的 ISO/IEC 14443A 帧和错误检测功能(奇偶校验和 CRC)。

MFRC631 支持多种 MIFARE 产品,如 MIFARE Classic(1 kB 和 4 kB 内存)、MIFARE Ultralight、MIFARE Ultralight C、MIFARE Plus 和 MIFARE DESFire 等,并且支持 MIFARE 产品系列高达 848 kbit/s 的双向传输速度。此外,它还支持 ISO/IEC 14443B 读写器通信方案的第 2 层和第 3 层(除防冲突功能外),防冲突功能需在主机控制器的固件以及上层实现。

二、特性与优势

2.1 高性能多协议支持

MFRC631 集成了 NXP ISO/IEC14443 - A 和 Innovatron ISO/IEC14443 - B 知识产权许可,支持高达 848 kbit/s 的传输速度,能满足多种应用场景的需求。它不仅支持 ISO/IEC 14443 类型 A、MIFARE Classic 和 ISO/IEC 14443 B 模式,还能通过硬件实现 MIFARE Classic 产品的加密读写操作,增强了数据传输的安全性。

2.2 低功耗设计

具备低功耗卡检测功能,可有效降低设备的功耗。同时,它还支持多种灵活高效的节能模式,包括硬关机、待机和低功耗卡检测模式,有助于延长设备的电池续航时间。

2.3 丰富的接口支持

支持多种主机接口,如 SPI(最高 10 Mbit/s)、I2C - bus 接口(快速模式最高 400 kBd,快速模式 + 最高 1000 kBd)和 RS232 串行 UART(最高 1228.8 kBd,电压电平取决于引脚电源),方便与不同的主机设备进行连接。此外,还提供了单独的 I2C - bus 接口用于连接安全访问模块(SAM),增强了系统的安全性。

2.4 其他优势

- 集成 PLL 从 27.12 MHz RF 石英晶体派生系统时钟,节省了成本。

- 具有 512 字节的 FIFO 缓冲区,可实现最高的事务处理性能。

- 提供 3 V 至 5.5 V(MFRC63102)或 2.5 V 至 5.5 V(MFRC63103)的电源供应范围,适应不同的电源环境。

- 多达 8 个自由可编程输入/输出引脚,增加了设计的灵活性。

三、功能模块详解

3.1 中断控制器

中断控制器负责处理中断请求的启用和禁用,所有中断都可以通过固件进行配置。固件还可以触发中断或清除待处理的中断请求。芯片实现了两个 8 位中断寄存器 IRQ0 和 IRQ1,以及两个 8 位中断使能寄存器 IRQ0En 和 IRQ1En。通过设置中断控制器寄存器中的位 7,可以设置和清除位 0 至 6。

MFRC631 通过在寄存器 Status1Reg 中设置位 IRQ 来指示某些事件,并且如果激活,还会通过引脚 IRQ 发出信号。引脚 IRQ 上的信号可用于利用主机的中断处理功能来中断主机,从而实现高效的主机软件。

3.2 定时器模块

3.2.1 定时器概述

MFRC631 实现了五个定时器,其中四个定时器(Timer0 至 Timer3)的输入时钟可以通过寄存器 T(x)Control 配置为 13.56 MHz、212 kHz(从 27.12 MHz 石英派生)或第五个定时器(Timer4)的下溢事件。每个定时器都实现了一个 16 位宽的计数器寄存器,定时器的重载值在寄存器 T(x)ReloadHi 和 T(x)ReloadLo 中定义。第五个定时器 Timer4 连接到内部 LFO(低频振荡器)作为输入时钟源,可用于唤醒系统。

3.2.2 定时器模式

- 超时计数器和看门狗计数器:通过设置寄存器 T(x)ReloadValue 并启动定时器计数,当定时器下溢时,如果在配置的时间间隔内事件未发生,定时器单元将生成中断请求,通知主机事件未发生。

- 唤醒定时器:Timer4 可在预定义的时间后唤醒系统。在低功耗卡检测模式下,可设置 T4Control.T4AutoWakeUp 和 T4Control.T4AutoRestart 来激活 Timer4 并自动将系统置于待机状态。如果检测到卡,主机通信可以启动;如果未检测到卡且 T4Control.T4AutoWakeUp 未设置,MFRC631 将保持全功率运行。

- 秒表:可以测量配置的开始和停止事件之间的时间间隔。通过设置寄存器 T(x)ReloadValueHi 和 T(x)ReloadLo,定时器开始递减计数,当配置的停止事件发生时,定时器停止计数,主机可以根据定时器间隔计算经过的时间。

- 可编程单次定时器:主机配置中断和定时器,启动定时器并等待引脚 IRQ 上的中断事件。在配置的时间后,中断请求将被触发。

- 周期性触发器:如果设置了位 T(x)Control.T(x)AutoRestart 并激活中断,在每个定时器周期结束后,将周期性地发出中断请求。

3.3 非接触式接口单元

3.3.1 ISO/IEC14443 类型 A 和 MIFARE Classic 通信模式

在该模式下,读写器到卡的通信采用 100% ASK、Miller 编码,传输速度为 106 kbit/s 至 848 kbit/s;卡到读写器的通信采用子载波负载调制、Manchester 编码或 BPSK,传输速度同样为 106 kbit/s 至 848 kbit/s。内部 CRC 协处理器根据 ISO/IEC 14443 A 第 3 部分计算 CRC 值,并根据传输速度内部处理奇偶校验生成。

3.3.2 ISO/IEC14443B 功能

读写器到卡的通信采用 NRZ、Miller 编码,传输速度为 106 kbit/s 至 848 kbit/s;卡到读写器的通信采用子载波负载调制、BPSK 编码,传输速度为 106 kbit/s 至 848 kbit/s。MFRC631 连接到主机后,可管理完整的 ISO/IEC 14443 B 协议。

3.4 主机接口

3.4.1 主机接口配置

MFRC631 支持多种主机接口类型,包括 SPI、I2C、I2CL 和串行 UART。在上电或从掉电恢复后,它会自动重置接口并检查当前的主机接口类型。通过控制引脚的逻辑电平组合来识别主机接口。

3.4.2 SPI 接口

作为 SPI 通信的从设备,SPI 时钟 SCK 由主设备生成。数据从主设备到从设备通过 MOSI 线传输,从 MFRC631 到主设备通过 MISO 线传输。支持高达 10 Mbit/s 的数据速度,NSS 信号用于启用或禁用 SPI 接口。读写数据时,遵循特定的字节顺序和地址字节格式。

3.4.3 RS232 接口

内部 UART 接口与 RS232 串行接口兼容,电压电平在 VSS 和 PVDD 之间。可通过设置寄存器 SerialSpeedReg 中的 BR_T0 和 BR_T1 位来选择不同的传输速度,默认传输速度为 115.2 kbit/s。读写数据时,遵循特定的帧格式。

3.4.4 I2C - bus 接口

实现了与 NXP Semiconductors I2C 接口规范兼容的接口,支持标准模式、快速模式和快速模式 +。在数据传输过程中,遵循特定的数据有效性、起始和停止条件、字节格式和应答规则。支持 7 位寻址,设备地址的高 5 位由 NXP 保留,低 2 位可由用户自由配置。

3.4.5 SAM 接口

MFRC631 实现了专用的 I2C 或 SPI 接口,可方便地将 MIFARE SAM 集成到应用中。SAM 可作为加密协处理器,与微控制器和读写器 IC 进行通信,有效降低协议开销,提高交易时间性能。

3.4.6 边界扫描接口

提供符合 IEEE 1149.1 的边界扫描接口,可通过测试单元对引脚功能进行覆盖,实现无需物理测试探针的互连测试。支持多种边界扫描命令,方便对芯片进行测试和编程。

3.5 缓冲区

MFRC631 实现了一个 512 × 8 位的 FIFO 缓冲区,用于缓冲主机和内部状态机之间的输入和输出数据流。可通过寄存器配置 FIFO 的大小(255 字节或 512 字节),并通过相关寄存器获取 FIFO 的状态信息,如长度、几乎满或几乎空的警告等。还可以通过设置 FIFOFlush 位清除 FIFO 缓冲区。

3.6 模拟接口和非接触式 UART

3.6.1 概述

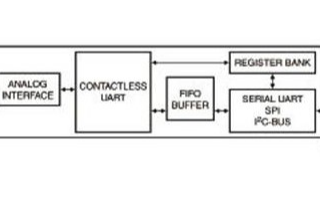

集成的非接触式 UART 支持外部主机在线处理协议要求的帧和错误检查,最高传输速度可达 848 kbit/s。外部电路可连接到通信接口引脚 SIGIN 和 SIGOUT 进行数据调制和解调。

3.6.2 TX 发射器

引脚 TX1 和 TX2 输出的信号是经包络信号调制的 13.56 MHz 载波,可直接驱动天线。可通过寄存器 DrvMode 配置信号,通过 TxAmp 设置调制指数。为避免过冲,提供了过冲保护功能,通过两个定时器 overshoot_t1 和 overshoot_t2 实现。还可通过位生成器对数据流进行编码。

3.6.3 接收器电路

采用多功能正交接收器架构,具有完全差分信号输入(RXP 和 RXN)。可配置为实现各种 13.56 MHz 协议的最佳接收性能,接收过程包括多个步骤,如正交解调等。支持单端和差分模式,单端模式下接收灵敏度会降低。

3.6.4 有源天线概念

通过配置相关寄存器,可将 MFRC631 的模拟部分和数字部分分离,实现有源天线概念。外部有源天线电路可连接到 MFRC631 的数字电路,提高系统的灵活性和性能。

3.6.5 符号生成器

用于创建各种协议符号,如 ISO14443 协议中的 SOF 或 EOF 符号。可通过符号定义寄存器和模式寄存器配置符号,每个符号由一组寄存器定义,包括位时钟和子载波频率、脉冲类型/长度和包络类型等。

3.7 内存

3.7.1 内存概述

MFRC631 实现了三种不同的内存:EEPROM、FIFO 和寄存器。上电时,通过自动将 EEPROM 区域的内容复制到寄存器来初始化寄存器。可通过执行 LoadProtocol 命令将 EEPROM 中的默认协议设置复制到寄存器,改变 MFRC631 的行为。读写 EEPROM 部分 2 可用于存储用户数据或预定义的寄存器设置。FIFO 用作输入/输出缓冲区,可提高系统性能。

3.7.2 EEPROM 内存组织

EEPROM 大小为 8 kB,按页组织,每页 64 字节。不同的内存区域有不同的用途,如产品信息和配置、寄存器重置、MIFARE Classic 密钥存储和寄存器设置协议区域等。

3.7.3 EEPROM 初始化内容 LoadProtocol

EEPROM 在生产时进行初始化,其内容可用于将 MFRC631 的某些寄存器重置为默认设置。通过执行 LoadProtocol 命令,可将 EEPROM 中的寄存器设置复制到相应的寄存器。

3.8 时钟生成

3.8.1 晶体振荡器

晶体振荡器为 MFRC631 提供时钟,作为载波生成、正交混频器 I 和 Q 时钟生成以及同步系统的编码器和解码器的时间基准。为获得最佳性能,建议使用内部振荡器缓冲器和推荐的电路,以确保时钟频率的稳定性和低抖动。

3.8.2 IntegerN PLL 时钟线

MFRC631 可通过 CLKOUT 引脚提供频率可配置的时钟(1 MHz 至 24 MHz),时钟源为 27.12 MHz 晶体振荡器。通过两个分频器确定输出频率,可根据需要配置不同的频率和分频比。

3.8.3 低频振荡器(LFO)

实现了低频振荡器(LFO),Timer4 可配置为使用 LFO 生成的时钟作为输入时钟,用于唤醒系统。LFO 在芯片生产时进行了校准,运行频率为 16 kHz。如果需要更高的精度,可通过数字状态机对 LFO 进行微调。

3.9 电源管理

3.9.1 供电概念

MFRC631 由 VDD(电源电压)、PVDD(焊盘电源)和 TVDD(发射器电源)供电,三者相互独立。建议使用阻塞电容对这些电源进行缓冲,以提高电源的稳定性。

3.9.2 功率降低模式

- 硬关机:通过将引脚 PDOWN 置为高电平,可实现硬关机,关闭内部 1.8 V 电压调节器和振荡器,将输出引脚切换到高阻抗状态。

- 待机模式:通过设置寄存器 Command 中的 PowerDown 位为 1 进入待机模式,此时内部电流源关闭,电压参考和电压调节器进入待机状态。退出待机模式时,需清除该位并遵循特定的操作步骤。

- 调制器关闭模式:通过设置寄存器 Control 中的 ModemOff 位为 1,可关闭天线发射器和接收器。

3.9.3 低功耗卡检测(LPCD)

LPCD 是一种节能模式,分为待机和检测两个阶段。通过唤醒计数器(WUC)控制待机时间,在检测阶段检测 I 和 Q 通道的值,并与寄存器中的阈值进行比较。如果超过阈值,将触发 LPCDIRQ 中断。

3.9.4 复位和启动时间

在 PDOWN 引脚施加 10 μs 的高电平可启动内部复位程序。复位完成且振荡器进入稳定工作状态后,芯片即可使用,典型的启动时间为 2.5 ms。

3.10 命令集

3.10.1 概述

MFRC631 的行为由状态机控制,通过向命令寄存器写入命令代码来执行命令。命令的参数和数据通过 FIFO 缓冲区进行交换。每个命令可通过向命令寄存器写入新的命令代码来停止。

3.10.2 命令集概述

提供了多种命令,如空闲命令、低功耗卡检测命令、加载密钥命令、MIFARE Classic 认证命令、接收命令、发送命令、收发命令、EEPROM 读写命令、加载寄存器命令、加载协议命令等。

3.10.3 命令功能

不同的命令具有不同的功能和执行条件,如空闲命令用于取消当前命令执行,LPCD 命令用于低功耗卡检测,MFAuthent 命令用于 MIFARE Classic 认证等。在执行命令时,需要根据命令的要求设置相应的参数和寄存器。

四、寄存器配置

4.1 寄存器位行为

根据寄存器的功能,其访问条件有所不同。主要分为读/写(r/w)、动态(dy)、只读(r)、只写(w)和保留(RFU)等类型。

4.2 MFRC631 寄存器概述

提供了多个可由主机修改的寄存器,涵盖了命令控制、主机控制、FIFO 控制、中断控制、非接触式接口配置、定时器配置、发射器配置、CRC 配置等多个方面。

4.3 命令配置

通过命令寄存器控制命令的执行,可设置命令的启动和停止,以及接收器和发射器电路的电源状态。

4.4 SAM 配置寄存器

HostCtrl 寄存器用于控制接口访问权限,可设置寄存器的可修改性、总线控制权和 SAM 接口的选择。

4.5 FIFO 配置寄存器

包括

-

MFRC631

+关注

关注

0文章

3浏览量

7108

发布评论请先 登录

MFRC52202HN1的特性和优势

CI523兼容FM17550/SKY1311 支持 ISO/IEC 14443 A/B/Mifare 更高速率 通信

ISO/IEC14443标准包括哪几个部分

如何使用安装CLRC663plus的CLEV6630B对MFRC630 plus进行评估?

ISO/IEC14443-4 标准协议

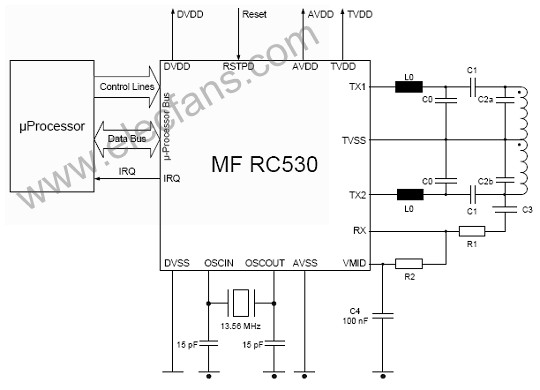

基于MFRC530设计的ISO14443A无接触读卡技术

基于ISO14443A协议的RFID模拟前端设计

ISO/IEC_FCD_14443-1

ISO/IEC_FCD_14443-2

ISO/IEC_CD_14443-4

MFRC523性能标准ISO/IEC 14443的A/B的前端产品数据表

高集成读写器MFRC523的主要特性及功能分析

高性能 ISO/IEC 14443 A/B 前端 MFRC631 详细解析

高性能 ISO/IEC 14443 A/B 前端 MFRC631 详细解析

评论