电子发烧友网报道(文/黄晶晶)由被誉为“硅仙人”的传奇CPU架构师Jim Keller创办的Tenstorrent公司,作为高性能RISC-V CPU与AI 计算领域的翘楚备受关注。近日,Tenstorrent 在上海举办TT Blueprint China技术峰会,官宣TT-Ascalon高性能RISC-V CPUIP正式上市,并介绍全系列IP产品。Tenstorrent十分重视中国市场的开拓,与Corelab、希姆计算公司等建立合作伙伴关系,共同推动RISC-V 在汽车、机器人以及服务器等高性能 AI 计算领域的广泛落地。

Jim Keller创办Tenstorrent公司的初衷正是希望提供基于开源架构的RISC-V IP、拓展性优秀的AI硬件和完全开源的AI软件栈,以帮助芯片设计降低成本、提高开发成功率。

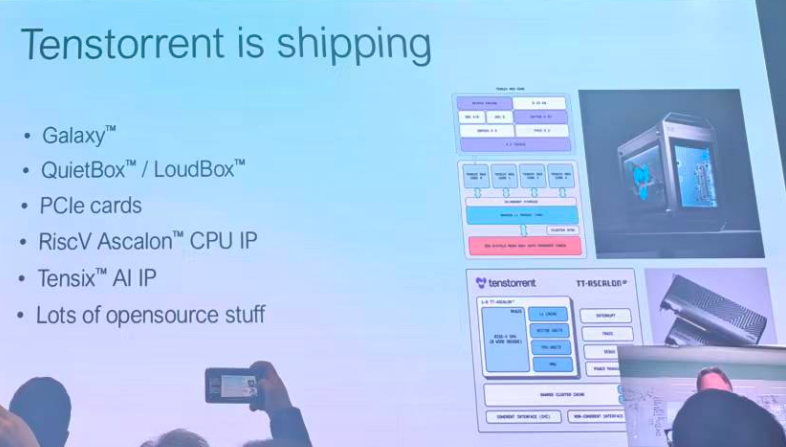

Tenstorrent正在出货的产品包括应用于高端服务器的Galaxy AIIP、小型服务器的QuietBox(采用水冷方案,适用于办公环境),以及LoudBox(采用风冷方案,适用于大型机架),此外还有PCIe卡、RISC-V Ascalon CPU IP、以及TensixAI处理器等等,并且明年Tenstorrent将进行IP产品线的重大升级。

同时,Tenstorrent还提供开源软件栈,开源AI编译器、AI模型、算子库和底层编程。在下一代AI方案中,Tenstorrent将发布芯粒OCA,芯粒将单芯片分割成更小的部分,开发者能够复用多个芯粒,而专注于AI、CPU处理器核心部分的开发,从而提高人工智能解决方案的易构建性,并降低成本。

值得一提的是,针对中国市场Tenstorrent的IP完全满足出口合规性要求,Tenstorrent还积极参与RISC-V的大学合作计划。

Ascalon高性能RISC-V IP

RISC-V是一种开源指令集架构(ISA)规范,正在全球范围内被广泛采用,此前在IoT领域已有不少RISC-V芯片出货,但鲜有产品在高性能计算领域取得突破。Tenstorrent工程副总裁Divyang Agrawal先生表示,Tenstorrent高性能RISC-V CPUTT-Ascalon具备真正的高性能计算能力,性能超越市场上任何现有RISC-V CPU,Ascalon在众多采用不同专有指令集架构的高端处理器中稳居领先行列。

Ascalon通过业界标准SPEC CPU基准测试验证,单核性能达到22 SPECint® 2006/GHz、>2.3 SPECint® 2017/GHz和>3.6 SPECfp® 2017/GHz,并可在Samsung SF4X工艺节点下实现>2.5 GHz主频,充分展现了其强大的设计和在先进工艺节点上的可扩展性。

Ascalon具有高度扩展,产品系列覆盖从AscalonX到S,其中S针对中端核心,对标Cortex A78,A710级别的性能。高端产品方面,Ascalon X拥有极致性能,对标Neoverse V3。

Ascalon完全兼容RVA23规范,并集成高性能RVV1.0矢量引擎,支持硬件虚拟化、先进内存管理和高级中断架构。此外,Ascalon还具备安全性和RAS(可靠性、可用性和可维护性)特性,包括侧信道攻击防护。Tenstorrent同步宣布,Ascalon已全面支持GCC、LLVM和Qemu,并已完成上游合入,开发者和客户可立即部署使用。

现场demo演试,基于单核心AscalonCPU运行90年代《毁灭战士》游戏十分顺畅,其加速器的功能直接由Ascalon的矢量单元运行,无需GPU。

Ascalon为服务器、AI基础设施、汽车高性能计算(HPC)及高级驾驶辅助系统(ADAS)等广泛应用场景提供完整的高性能解决方案。例如在网络市场存在大量定制化需求,在存储、智能网关、深度学习等领域需要卸载主要计算任务,这些任务可由RISC-V架构的渲染器或基于RISC-V的IT系统构建。

Atlantis高性能SoC芯片平台

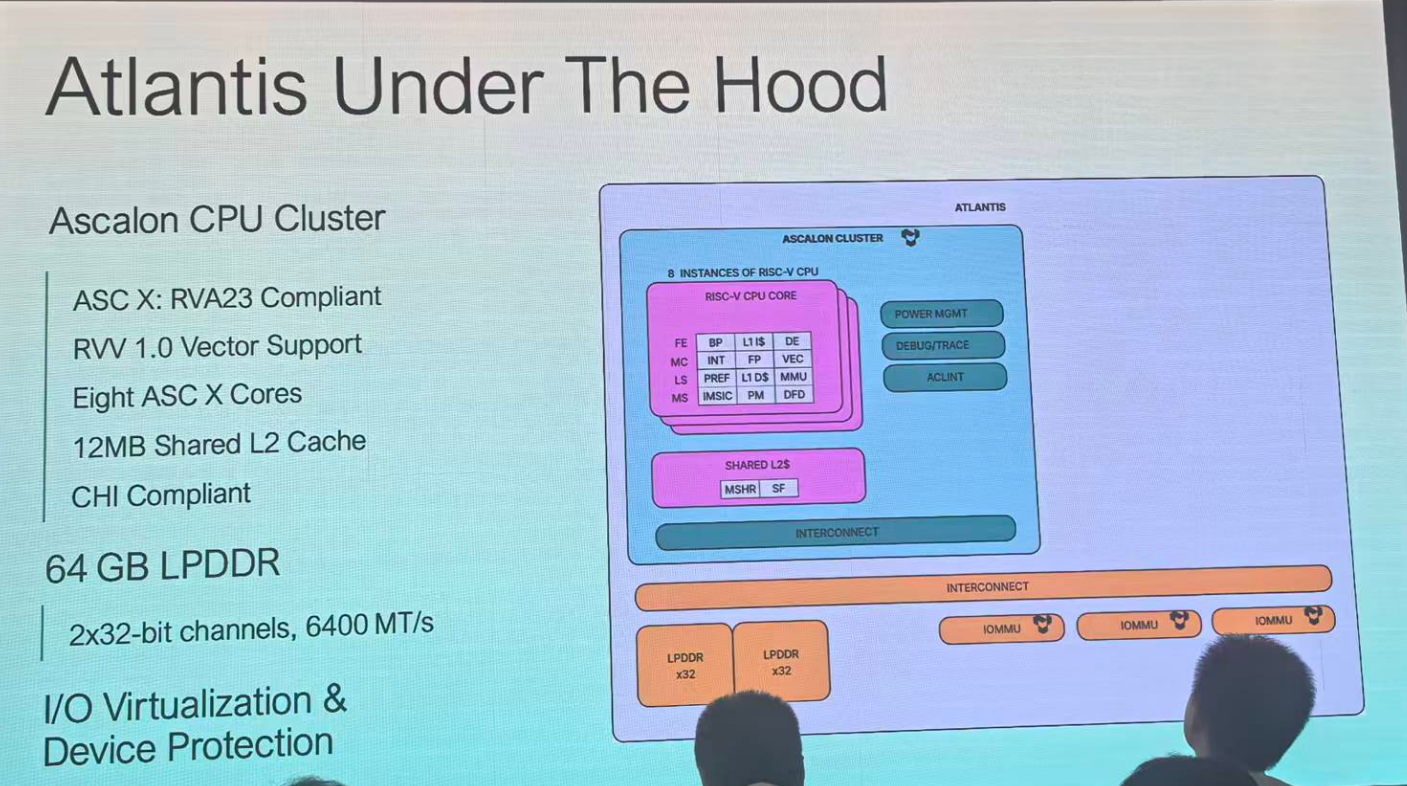

Tenstorrent已与CoreLab建立合作伙伴关系,推动区域客户支持和设计优化,帮助客户高效采用并快速部署其IP。Atlantis是高性能SoC芯片平台,围绕AscalonCPU构建集群。

从AscalonCluster来看,Ascalon可配置1-8个高性能核,每个核心搭配L1级缓存,多个核心共享L2级缓存。Tenstorrent首席工程师Sajosh Janarthanam表示,核心计算的实时性能有赖于内存带宽,我们配置64GBLPDDR内存运行速度可达6400MT/s,在Atlantis平台配备双通道LPDDR内存,高性能且低功耗。可利用软件轻松扩展并添加额外的I/O设备,包括20通道的PCIe Gen4接口,可以将其配置为16x1、4x5,或者2x8和1x4。USB3.1和USB2.0接口以满足设备的连接需求。配置网络控制功能,两个千兆以太网接口、SDA端口等。Atlantis配置GPU IP来自Imagination GPUBMX Force D40,视频解码器、多个显示端口、支持MP和SDMA协议,还有中断控制器用于处理来自设备和加速器的所有中断。并且添加加密引擎以及随机数生成器等。

在软件生态系统方面,Tenstorrent推出专有的调试功能,也与第三方供应商合作建立Atlantis的立方体模型用于测试、调试等。此外还提供开放的SVA功能用于内核支持,优化部分工具链例如LLVM、GCC以及开放的OCD脚本用于自动代码的分析等等。针对目前现有的RISC-V开发平台不允许软件开发者进行高性能软件开发、运行测试反馈慢等问题,Tenstorrent的生态平台能大幅缩短反馈时间,加速开发者的设计进程。

Tenstorrent不断丰富自有的IP体系,除了CPU IP之外还提供系统IP,众多子系统IP加持下的CPU组合、AI加速器组合等加速了客户的验证,助力产品快速上市。

希姆计算CEO梅迪认为,RISC-V在平衡可编辑性和通信加速能力上几乎是最好的方案,但是单纯的AI计算架构已经难有巨大突破,业界纷纷从单一芯片架构转到GPU、AI芯片、网络芯片的联合研发和优化上面。未来AI芯片发展方向必定是AI芯片和CPU的强强联合。基于这样的趋势,希姆计算与Tenstorrent、CoreLab建立密切的合作伙伴关系。希姆计算在成立的六年时间里研发两代AI芯片,出货超过1万张AI加速卡。合作三方基于硬件基础在系统层面、网络连接协议等做进深入的交互融合将产生更强大的生命力。

CoreLab Technology董事长吴雄昂指出,CoreLab平台极大地加速计算能力的实现,可以预制近80%的软硬件,让开发更高效。CoreLab通过开放可定制计算系统平台(OpenCSS)解决AI芯片的碎片化问题,支持客户在统一RISC-V基座上灵活定制加速器(如NPU、GPU),实现性能成倍提升。这个面向开发者的平台,支持AI PC、边缘服务器等应用。Tenstorrent提供高性能CPU的解决方案、希姆计算的AI加速卡可插接到Atlantis平台上。该平台还面向机器人市场,开发者能够将机器人的一些算法部署到Atlantis平台上进行优化。

Alexandria汽车芯片IP

Tenstorrent观察到快速发展的新能源汽车行业的痛点在于,缺乏通用编程模型。Tenstorrent力图基于Ascalon和Alexandria的平台采用相同的通用编程模型来打通数据的训练和推理。这套编程模型可以跨越不同代际不同层次的技术,而这正是RISC-V的灵活性开放性所赋予的。

TT Alexandria是 Tenstorrent 推出的一款高性能 RISC-V 汽车和机器人解决方案。Alexandria 以Ascalon处理器系列为基础打造,这一高性能IP添加功能安全特性。Alexandria 具备锁步(Lockstep)能力,可防护瞬态和永久性故障。Alexandria 所构建的安全特性使其能够支持 ADAS(高级驾驶辅助系统)、IVI(车载信息娱乐系统)和中央计算功能。它可以针对各种需求进行配置,并以 ISO 26262 认证为目标。

Alexandria 集成了硬件故障保护,以提供混合模式(Hybrid)、分离模式(Split)和锁定模式(Lock Modes);它优化了软件测试库(STL)和所有缓存上的内存保护,以及接口保护。Alexandria 适用于数字座舱、IVI、ADAS 和车辆中央计算。凭借这一系列特性,Alexandria 已经为用 RISC-V 应对汽车领域的挑战做好了充分准备,并满足市场对于一款高性能 RISC-V 设计的需求。

此外,Alexandria 将继续支持 Tenstorrent 建立一个真正的开放生态系统的愿景。在软件定义汽车的时代,Tenstorrent与AutoCore达成合作,AutoCore将以其旗舰产品AutoCore.OS赋能Tenstorrent高性能RISC-V处理器平台TT-Ascalon。这标志着成熟汽车软件与高性能RISC-V架构CPU及AI平台深度融合的里程碑。双方联合打造的该解决方案打破了传统封闭架构的垄断。Tenstorrent坚持开放性的解决方案,支持指令集架构(ISA)扩展及功能安全(FUSA),结合AutoCore灵活的软件配置,为主机厂(OEM)带来前所未有的自由度,让客户可以针对特定应用进行优化。

据悉,Alexandria IP计划在 2026 年第三季度发布,包括四核、4 兆字节的 ASIL B CPU IP,以及八核、12 兆字节的 ASIL B CPU IP两款。还将推出八核、12 兆字节的 ASIL D 和 B 兼容 CPU IP。

开放芯粒生态系统OCA

每一次科技浪潮几乎都伴随着一次芯片技术的飞跃,而随着 AI 的发展,人们对芯片的算力、存储都有了更高一个阶层的要求。随之而来的是芯片复杂度的提升,同时也是设计成本的极度提升。根据 IBS 的研究报告,如果从头设计一款 2 纳米的芯片,需要耗费7亿美元。这样的设计开销让许多量不是特别大的芯片,几乎没有办法使用2纳米或3纳米的工艺。随着设计成本的提高,芯片项目的成功率也在逐步降低,这和芯片本身的复杂度紧密关联。

一方面是设计成本的节节攀升,另一方面是成功率的稳步下降,这直接导致了越来越少的企业设计可产品化的高性能芯片。Tenstorrent 作为一个初创公司致力于高性能芯片,在经过多年的探索之后,认为有必要主导的一个开放芯粒生态系统Open Chiplet Atlas Ecosystem,简称 OCA 生态系统。

经济学之父亚当·斯密在他的著作《国富论》中提到:“分工是人类生产力的提高的第一要素。而开放的贸易交换是将分工转换成生产力的必要条件”。如果把朴素的经济学理论套用在芯片产业,那么芯粒(Chiplet)就是我们新芯片设计的再分工。而一个开源的生态系统,就是将这个芯粒转换成更高生产力的必要条件。

例如,在设计一颗芯粒的解决方案中,我们需要设计的仅仅是那一颗AI芯粒。所有其他功能都已经是现成的芯粒,你只需要拿来用。这样设计成本自然可以极大地降下来。同时,Tenstorrent 还提供芯粒的开发平台,可以进一步降低芯片开发成本。

Tenstorrent高级主任工程师Zhimin chen介绍,Tenstorrent 从六个方向支持OCA 生态系统,包括OCA 架构,它全面保障芯粒之间的互可操作性。OCA Harness,它是一个开源的芯粒系统逻辑的实现,它和架构的要求完全吻合。OCA Compliance,是一系列用于芯粒合规性的测试。OCA Chiplet Shell,是OCA Harness 和 Tenstorrent 连接芯粒之间的模块结合,目的是最大限度地简化芯粒设计当中的复杂度。OCA Chiplet,一个生态系统必须有很多芯粒,Tenstorrent 正在与合作伙伴全力开发OCA 芯粒。最后是OCA 芯粒模型,它包括功能模型和性能模型,主要可以帮助大家在设计芯粒时做协同仿真。这应该是现今业界对于一个芯粒生态系统最完整的支持。

截止目前,Tenstorrent 已经发布OCA 架构的 0.7 版本,以及 AXI over UCIe 的0.6 版本。已经得到来自业界非常广泛的支持,包括芯片设计公司、IP 提供商、芯片设计服务公司、Foundry、系统集成商、科研机构,还有一部分政府相关的产业部门。在国内包括蓝芯算力、中科创达(ThunderSoft)、Verisilicon 以及上海交大的孙亚男教授等纷纷给予支持。随着架构的完善,Tenstorrent计划于明年上半年对OCA架构 1.0 版本进行定稿。届时,该公司设计的一批基于 OCA 架构的芯粒也将完成封装,并完成一系列的测试。从而给业界提供经过实际产品验证的架构方案。

AI时代到来,RISC-V成为必然选择

在媒体群访环节,CoreLab Technology董事长吴雄昂谈到RISC-V赶上AI的大爆发,将获得前所未有的发展机遇。过去几年,计算机领域每次技术革命爆发初期都会催生大量新需求,且这些需求的计算方式差异巨大、迭代速度惊人。举例来说,过去是跑操作系统的时代,而现在是AI驱动的token生成时代。传统计算模式由Arm和英伟达主导,前者以通用处理器见长,后者则擅长数据密集型计算。Arm之所以能成功,正是因为其相对开放且成本可控的特性。

国内早期曾质疑Arm性能不足,认为“跑都跑不动”,但正是其开放性和低成本,让许多企业敢于尝试。一旦部分创新者验证成功,就会带动整个生态快速迭代。背后的经济逻辑很清晰:敢于尝试的新锐企业往往创新能力更强,在新一轮技术革命中更能抢占先机,最终脱颖而出。历史规律反复印证这点——英特尔击败IBM,正是凭借X86架构的开放性打破了封闭生态;Arm后来居上,则因其比x86更开放的授权模式,让安卓等软件生态得以蓬勃发展,吸引众多企业参与。同理,特斯拉初入电车领域时面临“没有充电桩”的质疑,但创新者敢于突破,最终改变了行业格局。

每一波技术创新浪潮中,由于新架构门槛较低,愿意试错的新玩家能够崛起。Jim Keller作为芯片设计领域顶尖技术团队的领导者,他愿意尝试新架构,正是看准RISC-V的巨大潜力。

AI正是这波技术创新浪潮的驱动力。有了这个驱动力,我们的硬件架构就有了用武之地。在硬件创新架构上,每一次有100倍成长的时候就会有新架构出来,这是经济规律,未来三大计算架构RISC-V必有其一。

在吴雄昂看来,AI计算的token generation会不断地演进,那么与之相适应的硬件和OS必然是全新的。其中硬件架构要体现性能和好用,但现在RISC-V性能尚可,但远未到好用的程度。CoreLab搭建的平台正是针对AI智能的平台化,重点解决AI计算的需求问题。

他认为,未来大模型就是OS,机器人或类机器人就是硬件承载体。而RISC-V的机会在于能否在这些自主式设备中驱动算力的释放。这就要求RISC-V的CPU具有区块化功能,可以根据大模型OS进行转换,芯片基于数据在算法基础上设计,算法又跟数据强相关,也就是说核心数据决定了OS以及芯片的最终形态。

发布评论请先 登录

RT-Thread 邀您参与“开放・连接”2026玄铁 RISC-V 生态大会,携手共铸 RISC-V“芯”纪元

Powered by XuanTie,Qwen Inside:阿里通义大模型携手玄铁 RISC-V开启“端侧智能”新纪元

Tenstorrent与AutoCore宣布战略合作,以AutoCore.OS赋能高性能RISC-V汽车计算

探索RISC-V在机器人领域的潜力

为什么RISC-V是嵌入式应用的最佳选择

提高RISC-V在Drystone测试中得分的方法

大湾区RISC-V生态全景展示:RISC-V生态发展论坛、开发者Workshop和生态应用专区

时擎科技亮相2025 RISC-V中国峰会,深度解析高性能RISC-V SoC技术挑战与创新

基于北海云计算试验平台的 RISC-V 虚拟化技术探索

知合计算:RISC-V架构创新,阿基米德系列剑指高性能计算

孟建熠:攀登 RISC-V 高性能高峰,打造标杆产品

RISC-V International CEO:RISC-V 应用全面开花,2031 年渗透率将达 25.7%

智芯公司RISC-V高性能CPU芯片获得权威认可

RISC-V架构下的编译器自动向量化

DC-ROMA RISC-V AI PC 正式发布!

Jim Killer掌舵,超强RISC-V高性能计算来了!大模型即OS时代,RISC-V势在必得

Jim Killer掌舵,超强RISC-V高性能计算来了!大模型即OS时代,RISC-V势在必得

评论