在电子工程师的日常工作中,选择一款合适的模数转换器(ADC)至关重要。今天,我们就来深入探讨TI公司的ADS624X系列ADC,包括ADS6245、ADS6244、ADS6243和ADS6242这几款产品,看看它们在性能、功能和应用方面有哪些独特之处。

文件下载:ads6242.pdf

产品概述

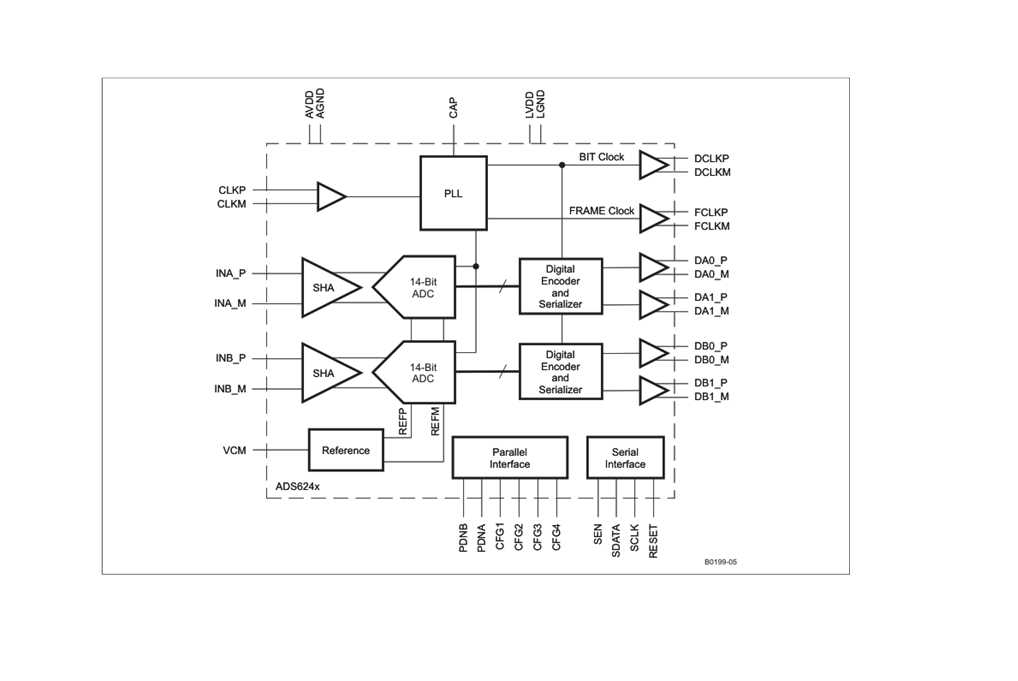

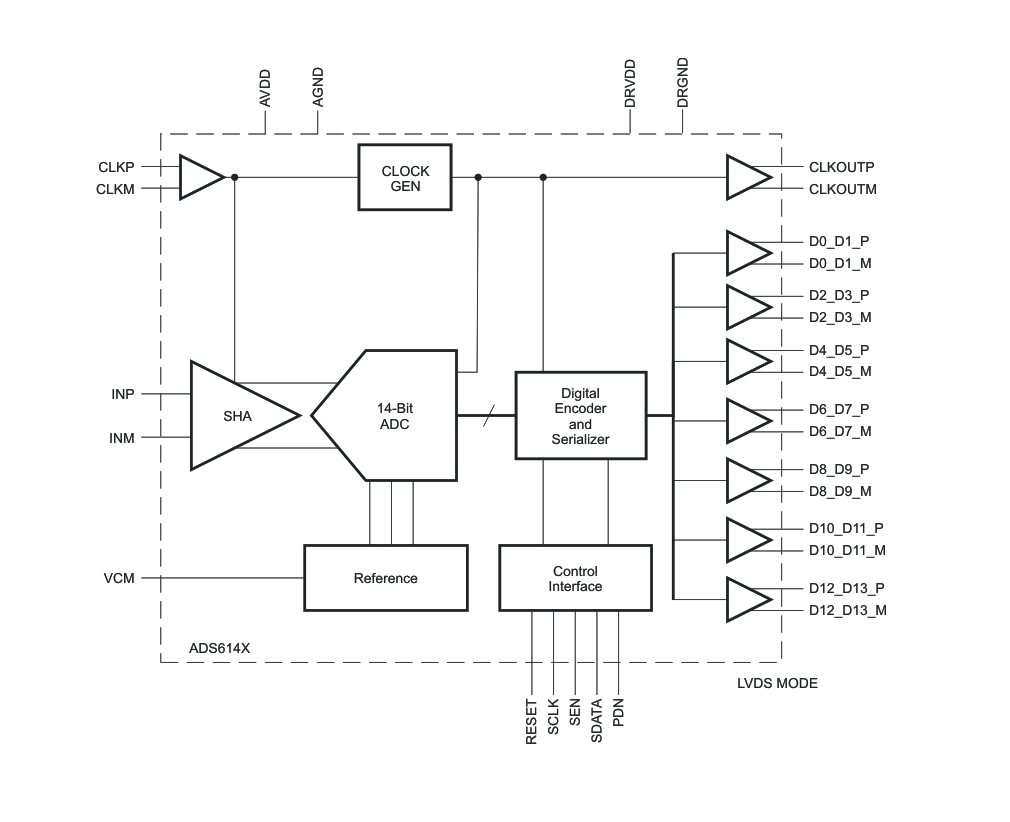

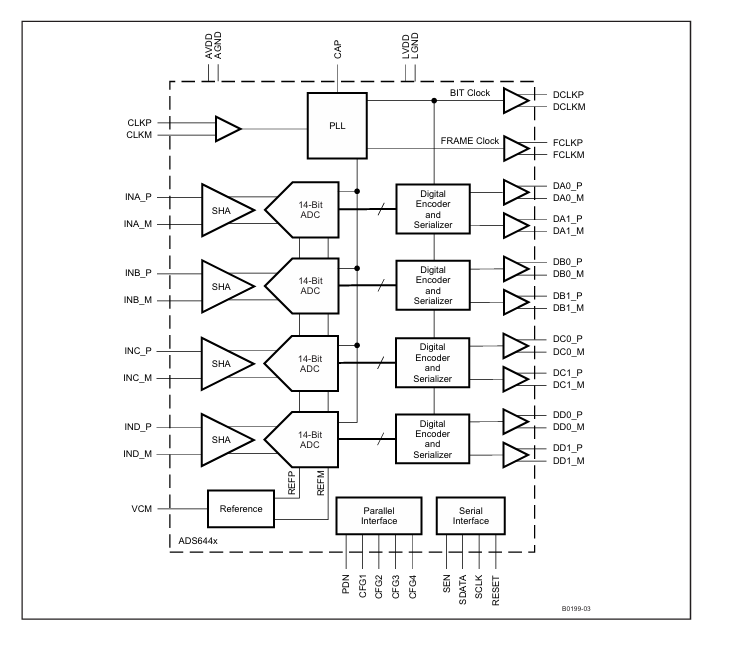

ADS624X系列是高性能的14位、125/105/80/65 MSPS双通道A - D转换器。其采用串行LVDS数据输出,有效减少了接口线数量,使得该系列产品能够封装在紧凑的48引脚QFN封装(7 mm × 7mm)中,极大地提高了系统集成密度。这对于空间有限的设计场景来说,无疑是一个巨大的优势。

主要特性

兼容性出色

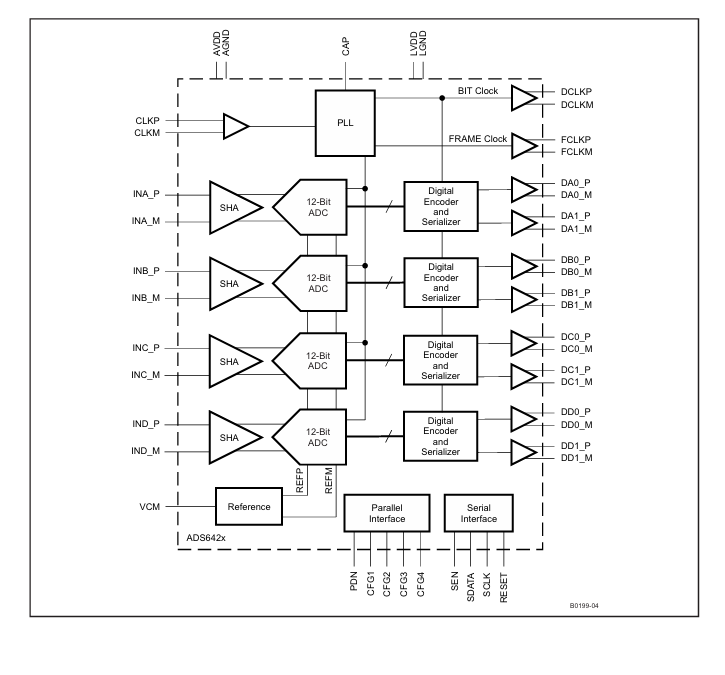

该系列产品与12位家族(ADS622X)引脚兼容,与四通道家族(ADS644X和ADS642X)功能兼容。这种兼容性为工程师在不同设计需求之间切换提供了便利,降低了设计成本和风险。

高性能指标

- 高分辨率与无失码:具备14位分辨率且无失码,能够提供高精度的转换结果,满足对数据精度要求较高的应用场景。

- 同时采样与保持:支持同时采样和保持功能,确保多通道输入信号的同步采集,避免了信号之间的时间差带来的误差。

- 增益灵活可调:拥有3.5 dB的粗增益和最高6 dB的可编程细增益,可用于在SFDR(无杂散动态范围)和SNR(信噪比)之间进行权衡。在不同的应用场景中,工程师可以根据实际需求调整增益,以达到最佳的性能表现。

- 多种时钟输入支持:支持正弦波、LVCMOS、LVPECL、LVDS时钟输入,且时钟幅度可低至400 mVpp。这种灵活性使得ADS624X能够适应各种不同的时钟源,方便与不同的系统进行集成。

- 内部参考与外部参考支持:内置内部参考,同时也支持外部参考模式,且参考无需外部去耦。这不仅简化了设计,还提高了系统的稳定性和可靠性。

应用领域广泛

ADS624X系列产品适用于多种应用场景,包括基站IF接收器、分集接收器、医学成像和测试设备等。在这些领域中,其高性能和灵活性能够充分发挥作用,为系统提供准确、可靠的数据采集。

性能对比

| 型号 | 采样率(MSPS) | SFDR(dBc) - Fin = 10MHz (0 dB gain) | SFDR(dBc) - Fin = 170MHz (3.5 dB gain) | SINAD(dBFS) - Fin = 10MHz(0 dB gain) | SINAD(dBFS) - Fin = 170MHz (3.5 dB gain) | 每通道功耗(mW) |

|---|---|---|---|---|---|---|

| ADS6245 | 125 | 87 | 79 | 73.4 | 68.3 | 500 |

| ADS6244 | 105 | 91 | 83 | 73.4 | 69.3 | 405 |

| ADS6243 | 80 | 92 | 84 | 74.2 | 69.4 | 350 |

| ADS6242 | 65 | 93 | 84 | 74.3 | 70 | 315 |

从这些数据可以看出,不同型号的ADS624X在采样率、SFDR、SINAD和功耗等方面存在差异。工程师可以根据具体的应用需求,选择最合适的型号。例如,对于对采样率要求较高的应用,可以选择ADS6245;而对于对功耗敏感的应用,则可以考虑ADS6242。

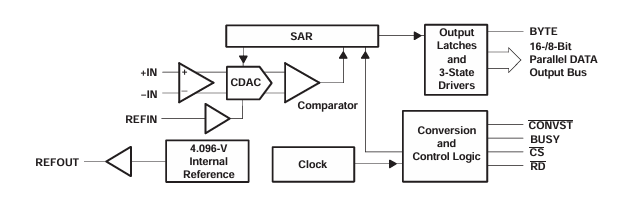

工作原理

ADS624X是基于CMOS技术的开关电容架构的双通道14位流水线ADC。在外部输入时钟的上升沿,所有四个通道同时启动转换。输入信号被每个通道的采样保持电路捕获后,通过一系列低分辨率阶段进行顺序转换。这些阶段的输出在数字校正逻辑块中组合,形成最终的14位字,整个过程存在12个时钟周期的延迟。每个通道的14位字被序列化并以LVDS电平输出,同时还输出位时钟和帧时钟,帧时钟与14位字边界对齐。

关键设计要点

模拟输入

- 采样保持架构:模拟输入采用基于开关电容的差分采样保持架构,这种拓扑结构即使在高输入频率下也能实现出色的AC性能。

- 偏置要求:INP和INM引脚需要在VCM引脚提供的1.5 V共模电压附近进行外部偏置。对于满量程差分输入,每个输入引脚需要在VCM + 0.5 V和VCM – 0.5 V之间对称摆动,从而实现2 - Vpp的差分输入摆动。

- 驱动电路要求:为了获得最佳性能,模拟输入必须采用差分驱动方式,以提高共模噪声抗扰能力和偶次谐波抑制能力。建议在每个输入引脚串联一个5 - Ω电阻,以抑制封装寄生效应引起的振铃。同时,需要为共模开关电流提供低阻抗路径(<50 Ω),例如通过使用两个电阻将每个输入端连接到共模电压(VCM)。此外,驱动电路还需要在所需的频率范围内提供低插入损耗,并与源阻抗匹配。

时钟输入

- 驱动方式多样:ADS624X的时钟输入可以采用差分驱动(SINE、LVPECL或LVDS)或单端驱动(LVCMOS),不同驱动方式之间的性能差异较小。

- 共模电压设置:时钟输入的共模电压通过内部5 - kΩ电阻设置为VCM,这使得可以使用变压器耦合驱动电路来驱动正弦波时钟,或者对LVPECL、LVDS时钟源进行交流耦合。

- 性能优化建议:为了获得最佳性能,建议采用差分驱动时钟输入,以降低对共模噪声的敏感性。对于高输入频率采样,建议使用低抖动的时钟源,并对时钟源进行带通滤波,以减少抖动的影响。此外,使用非50%占空比的时钟输入不会影响性能。

- 时钟缓冲器增益:当使用正弦时钟输入时,随着时钟幅度的增加,时钟抖动带来的噪声会减小。因此,建议使用较大的时钟幅度(>1Vpp),以避免性能下降。时钟缓冲器具有可编程增益,可以放大输入时钟,以支持非常低的时钟幅度。增益可以通过编程寄存器位进行设置,从Gain 0到Gain 5单调递增。

电源管理

- 电源模式丰富:ADS624X具有三种电源管理模式,分别是全局电源关闭、通道待机和输入时钟停止。

- 全局电源关闭:在全局电源关闭模式下,几乎整个芯片都会被关闭,包括四个ADC、内部参考、PLL和LVDS缓冲器。此时,总功耗典型值降至约77 mW(输入时钟运行时)。该模式可以通过设置寄存器位来启动,输出数据和时钟缓冲器处于高阻抗状态。从该模式唤醒到数据在正常模式下变为有效需要100 μs。

- 通道待机:在通道待机模式下,每个通道的ADC会被关闭,这有助于实现非常快速的唤醒时间。四个ADC可以通过寄存器位独立关闭,而输出LVDS缓冲器保持通电。从该模式唤醒到数据在正常模式下变为有效需要200个时钟周期。

- 输入时钟停止:当输入时钟频率低于1 MSPS,或者在任何采样频率下输入时钟幅度小于400 mV(pp,差分,默认时钟缓冲器增益设置)时,转换器会进入该模式。此时,所有ADC和LVDS缓冲器都会被关闭,功耗约为235 mW。从该模式唤醒到数据在正常模式下变为有效需要100 μs。

数字输出接口

- 输出选项灵活:ADS624X提供多种灵活的输出选项,包括1 - 线、1×帧时钟、14×和16×序列化与DDR位时钟;2 - 线、1×帧时钟、16×序列化,与DDR和SDR位时钟,字节方式/位方式/字方式;2 - 线、1×帧时钟、14×序列化,与SDR位时钟,字节方式/位方式/字方式;2 - 线、(0.5 x)帧时钟、14×序列化,与DDR位时钟,字节方式/位方式/字方式。这些选项可以通过并行引脚或串行接口轻松编程。

- 不同接口特点:不同的输出接口选项在最大采样频率、位时钟频率和输出数据速率等方面会有所不同。例如,1 - 线接口适合较低采样频率的应用,而2 - 线接口则更适合较高采样频率的应用。在2 - 线接口中,16×序列化可以方便未来无缝升级到16位ADC,而无需修改接收器捕获逻辑设计。

测试与验证

- 捕获测试模式:ADS624X输出的位时钟(DCLK)几乎位于数据转换的中心位置。建议在PCB上以最小的相对偏差布线位时钟、帧时钟和输出数据线,以确保接收器有足够的建立/保持时间进行可靠捕获。

- 测试模式多样:该系列产品包括DESKEW、SYNC等测试模式,以及全零、全一和翻转等其他测试模式。这些模式可以用于验证接收器捕获时钟边缘的位置是否正确,以及确保反序列化后的数据与帧边界对齐。

总结

ADS624X系列ADC凭借其高性能、多功能和灵活性,为电子工程师在数据采集和处理领域提供了一个优秀的解决方案。无论是在基站通信、医学成像还是测试设备等应用中,它都能够满足不同的设计需求。在实际设计过程中,工程师需要根据具体的应用场景,合理选择型号,并注意模拟输入、时钟输入、电源管理和数字输出接口等关键设计要点,以充分发挥ADS624X的性能优势。你在使用ADS624X系列ADC时遇到过哪些问题?又是如何解决的呢?欢迎在评论区分享你的经验和见解。

-

adc

+关注

关注

100文章

7419浏览量

553831 -

lvds

+关注

关注

2文章

1216浏览量

69134 -

模数转换器

+关注

关注

26文章

3967浏览量

129728 -

QFN封装

+关注

关注

0文章

193浏览量

17589

发布评论请先 登录

超声设计考虑及灵活性实现

ADS6245/ADS6244/ADS6243/ADS624

极具灵活性的电池充电器解决方案

具有串行LVDS输出的双通道14位模数转换器ADS624X系列的详细资料概述

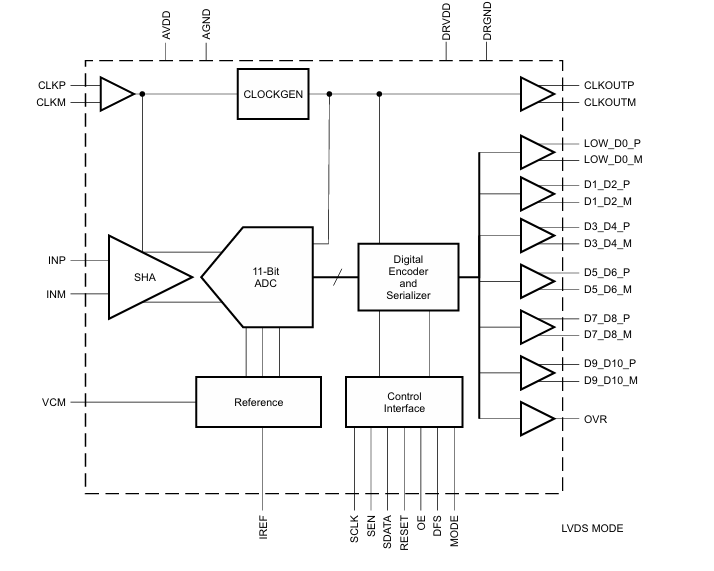

深入解析ADS5517:高性能11位200 MSPS ADC的卓越之选

探秘ADS612X系列12位ADC:高性能与低功耗的完美结合

TI ADS642X系列ADC:高性能与灵活性的完美结合

深入解析ADS2806:高性能12位ADC的设计与应用

深入解析ADS850:高性能14位ADC的卓越之选

深入解析ADS624X系列ADC:高性能与灵活性的完美结合

深入解析ADS624X系列ADC:高性能与灵活性的完美结合

评论