在当今高速发展的电子领域,数据采集系统对模拟 - 数字转换器(ADC)的性能要求日益严苛。TI推出的ADS62P15双通道11位ADC,凭借其出色的性能和丰富的功能,成为众多应用场景中的理想之选。下面我们就从多个方面对这款ADC进行详细剖析。

文件下载:ads62p15.pdf

一、核心特性概览

1. 高采样率与高精度

ADS62P15的最大采样率可达125 MSPS,能够快速准确地采集模拟信号。同时,它具备11位分辨率且无失码,保证了数据转换的高精度。在输入频率为50 MHz时,其无杂散动态范围(SFDR)可达84 dBc,信噪比(SNR)为67.1 dBFS,展现出了优秀的信号处理能力。

2. 丰富的输出接口

该ADC提供并行CMOS和DDR LVDS两种输出接口选项,可根据不同的系统需求灵活选择,增强了系统设计的灵活性。

3. 增益调节功能

ADS62P15拥有3.5 dB的粗增益和最高6 dB的可编程细增益,能够在SNR和SFDR之间进行有效的权衡,满足不同应用场景下对信号质量的要求。

4. 强大的数字处理模块

内置数字处理模块包含偏移校正、细增益校正(步长为0.05 dB)、2/4/8抽取以及内置和自定义可编程24抽头低/高/带通滤波器等功能。这些功能可以对采集到的数据进行进一步处理,提高数据的准确性和可用性。

5. 灵活的时钟支持

支持Sine、LVPECL、LVDS和LVCMOS时钟,且时钟幅度可低至400 mVPP,还具备时钟占空比稳定器,确保在不同时钟信号下都能稳定工作。

6. 内部参考与外部参考支持

ADS62P15内置参考,同时也支持外部参考,为系统设计提供了更多的选择。

7. 紧凑的封装与引脚兼容性

采用64 - QFN(9mm × 9mm)封装,体积小巧,便于集成。并且与14位和12位系列(ADS62P4X/ADS62P2X)引脚兼容,方便用户进行产品升级和替换。

二、应用领域广泛

ADS62P15的高性能和多功能使其在多个领域都有广泛的应用:

1. 无线通信基础设施

在无线基站等通信设备中,ADS62P15能够快速准确地采集和处理信号,提高通信系统的性能和稳定性。

2. 软件定义无线电(SDR)

SDR系统需要灵活的信号处理能力,ADS62P15的可编程增益和数字处理模块正好满足了这一需求,可实现不同通信标准的支持。

3. 功率放大器线性化

通过对信号的精确采集和处理,ADS62P15可以帮助实现功率放大器的线性化,提高功率放大器的效率和性能。

4. 医疗成像

在医疗成像设备中,如超声、CT等,高精度的ADC是保证图像质量的关键。ADS62P15的高分辨率和低噪声特性能够满足医疗成像对信号采集的严格要求。

5. 雷达系统

雷达系统需要快速、准确地采集目标信号,ADS62P15的高采样率和良好的动态性能使其能够胜任雷达信号的采集任务。

6. 测试与测量仪器

在测试与测量领域,对ADC的精度和稳定性要求极高。ADS62P15的出色性能可以确保测试结果的准确性和可靠性。

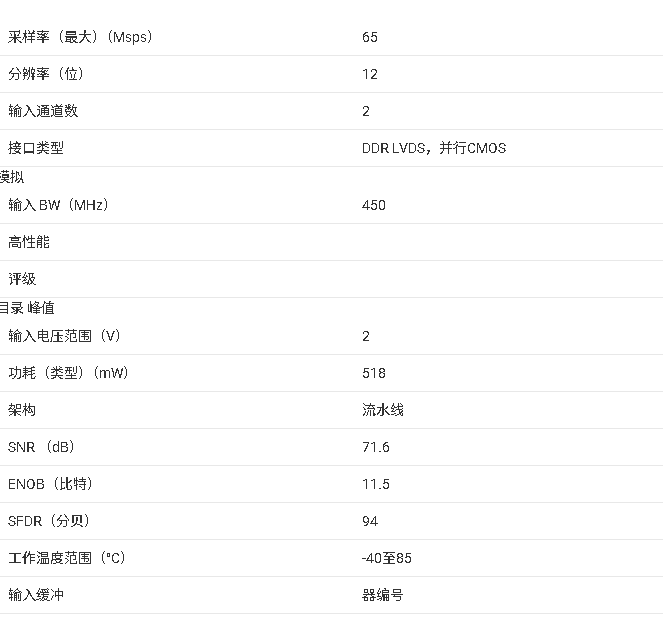

三、电气特性详解

1. 模拟输入特性

- 差分输入电压范围:为2 Vpp,能够适应较大范围的模拟信号输入。

- 差分输入电阻:大于1 MΩ,差分输入电容为7 pF,模拟输入带宽可达450 MHz,保证了在高频信号输入时的良好性能。

-

模拟输入共模电流:每个输入引脚的模拟输入共模电流为125 μA,VCM共模电压输出为1.5 V,VCM输出电流能力为4 mA。

2. 电源特性

- 模拟电源电流:AVDD的模拟电源电流为216 mA。

- 输出缓冲电源电流:在不同的接口和负载条件下,输出缓冲电源电流有所不同。例如,在CMOS接口、DRVDD = 1.8 V、2.5 MHz输入信号且无负载电容时,电流为17 mA。

-

总功率:不同接口和工作条件下的总功率也有所差异。如在CMOS接口、DRVDD = 3.3 V、50 MHz输入信号、10 pF负载电容时,总功率为1.225 W;在LVDS接口、DRVDD = 3.3 V时,总功率为0.94 W。此外,全局功率下电时功率为30 - 60 mW。

3. 直流精度特性

- 无失码:保证了数据转换的准确性。

- 差分非线性(DNL):范围为 - 0.8到±0.4到0.8 LSB。

- 积分非线性(INL):范围为 - 3.5到±1到3.5 LSB。

- 偏移误差:为 - 10到±3到10 mV,偏移误差温度系数为0.05 mV/℃。

-

增益误差:由内部参考不准确和通道增益误差两部分组成,内部参考不准确导致的增益误差为 - 1到+0.25到1 %FS,通道自身的增益误差为 - 1到+0.3到1 %FS,通道增益误差温度系数为0.005到4 %/℃。

4. 动态性能特性

- 信噪比(SNR)和信噪失真比(SINAD):在不同输入频率和增益条件下,SNR和SINAD表现出色。例如,在输入频率为50 MHz时,SNR为65.5 - 67.1 dBFS,SINAD为65 - 66.9 dBFS。

- 有效位数(ENOB):在输入频率为50 MHz时,ENOB可达10.5 - 10.8位。

- 无杂散动态范围(SFDR):在不同输入频率和增益条件下,SFDR也有较好的表现。如在输入频率为50 MHz时,SFDR为75 - 79 dBc。

- 总谐波失真(THD):在不同输入频率下,THD能够控制在较低水平。例如,在输入频率为50 MHz时,THD为72 - 77 dBc。

四、数字特性与时序要求

1. 数字输入输出特性

- 数字输入:高电平输入电压为2.4 V,低电平输入电压为0.8 V,输入电容为4 pF。

- 数字输出 - CMOS模式:高电平输出电压为DRVDD,低电平输出电压为0 V,输出电容(内部)为2 pF。

-

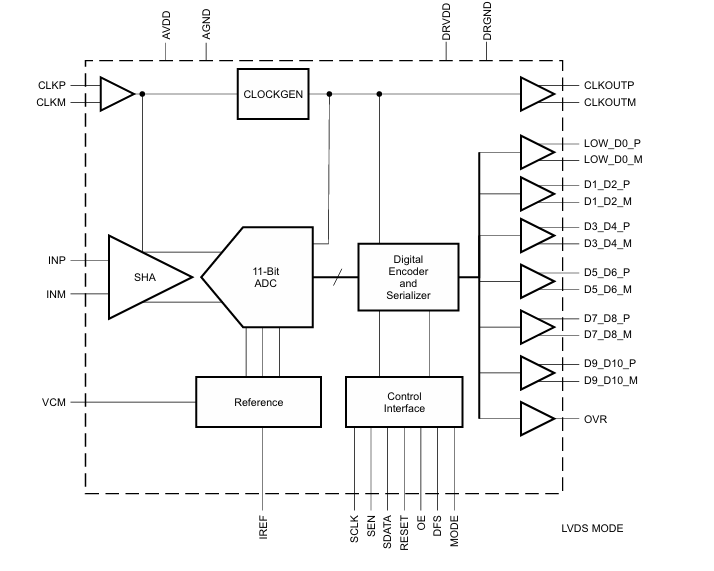

数字输出 - LVDS模式:高电平输出电压为1375 mV,低电平输出电压为1025 mV,输出差分电压为250 - 350 - 500 mV,输出偏移电压为1200 mV,输出电容为2 pF。

2. 时序要求

ADS62P15的时序要求较为严格,包括孔径延迟、孔径抖动、唤醒时间、潜伏期等参数。例如,孔径延迟典型值为1.8 ns,孔径抖动为130 fs rms。在不同的工作模式和状态下,唤醒时间和潜伏期也有所不同。如从全局功率下电到有效输出数据的唤醒时间为15 - 50 μs,在低潜伏期模式下潜伏期为10个时钟周期。

五、设备配置与接口

1. 设备配置方式

ADS62P15可以通过并行接口控制、串行接口编程或两者结合的方式进行配置。

- 并行接口控制:将RESET引脚接高电平(AVDD),通过SEN、SCLK、CTRL1、CTRL2和CTRL3引脚直接控制ADC的某些模式。

- 串行接口编程:将RESET引脚置低,SEN、SDATA和SCLK引脚作为串行接口数字引脚,用于访问ADC的内部寄存器。在编程前,需要将寄存器复位到默认值。

-

两者结合:将RESET引脚置低,并行接口控制引脚CTRL1 - 3和串行接口寄存器结合使用,增加了配置的灵活性。

2. 串行接口

- 数据传输:当SEN为低电平时,允许数据串行移位进入设备。在SEN有效(低电平)时,串行数据SDATA在SCLK的每个下降沿被锁存,并在第16个SCLK下降沿加载到寄存器中。

-

寄存器初始化:上电后,可通过硬件复位(在RESET引脚施加高电平脉冲)或软件复位(通过串行接口将位置高)将内部寄存器初始化为默认值。

3. 串行寄存器读出

在CMOS接口模式下,可通过设置寄存器位 = 1来读取内部寄存器的内容,用于诊断和验证串行接口通信。读取完成后,将 = 0以启用寄存器写入。

六、典型特性与应用信息

1. 典型特性

通过一系列典型特性图,我们可以直观地了解ADS62P15在不同条件下的性能表现,如不同输入信号频率下的频谱、SFDR与输入频率的关系、性能与电源、温度、输入时钟幅度和输入幅度的关系等。这些特性图为工程师在实际应用中优化系统性能提供了重要参考。

2. 应用信息

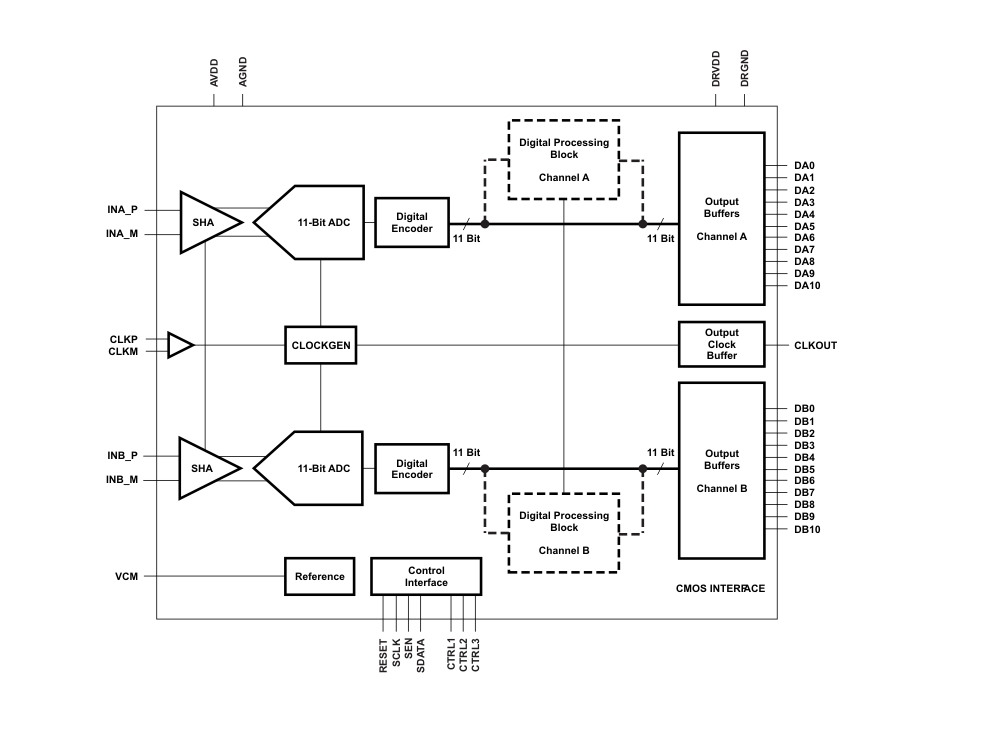

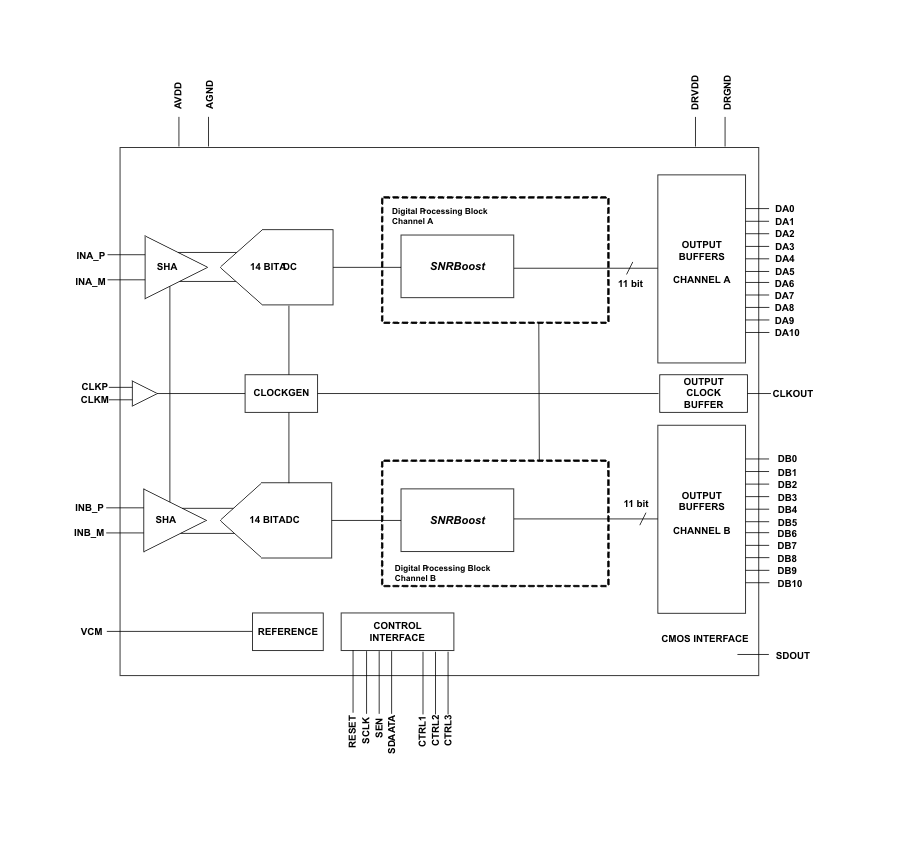

- 工作原理:ADS62P15采用CMOS工艺和开关电容技术,通过外部输入时钟的上升沿启动转换过程。信号被输入采样保持电路捕获后,经过一系列小分辨率级进行顺序转换,最终在数字校正逻辑块中组合输出。

- 模拟输入:模拟输入采用基于开关电容的差分采样保持架构,具有良好的AC性能。输入引脚INP和INM需外部偏置在1.5 V的共模电压附近,以实现2 Vpp的差分输入摆幅。

- 驱动电路:为了获得最佳性能,模拟输入应采用差分驱动方式。可使用RF变压器或差分放大器作为驱动电路,并根据输入频率的不同选择合适的配置。例如,在低输入频率时可使用单1:1匝数比变压器,在高输入频率时可使用两个相同的RF变压器背对背连接。

- 参考:ADS62P15内置内部参考REFP和REFM,无需外部组件。也可通过编程选择外部参考模式,在该模式下,VCM引脚作为参考输入,通过内部缓冲和增益生成REFP和REFM电压。

- 增益设置:具备粗增益和可编程细增益,可通过串行接口进行编程。粗增益为3.5 dB,旨在提高SFDR而对SNR影响较小;细增益可在0 - 6 dB范围内以0.5 dB为步长进行编程,可在SFDR和SNR之间进行权衡。

- 时钟输入:时钟输入可采用差分或单端方式驱动,对性能影响较小。为了获得最佳性能,建议采用差分驱动方式,并使用低抖动的时钟源。

- 功率下电:ADS62P15具有全局功率下电、单个通道待机和单个通道输出缓冲禁用三种功率下电模式,可通过串行寄存器位或控制引脚进行设置。

- 数字输出:提供并行CMOS和DDR LVDS两种输出接口,可通过串行寄存器位或并行引脚进行选择。在不同的接口模式下,输出数据的格式和特点也有所不同。例如,在CMOS模式下,DRVDD电流与采样频率和负载电容有关;在DDR LVDS模式下,默认LVDS缓冲输出电流为3.5 mA,且可进行编程调整。

七、数字处理模块详解

1. 偏移校正

ADS62P15内置偏移校正算法,可通过串行寄存器位(OFFSET LOOP EN)启用。启用后,算法会估计通道偏移并在每个时钟周期进行校正。校正环路的时间常数可通过寄存器位(OFFSET LOOP TC)进行控制。

2. 增益校正

可对ADC通道增益进行精细校正,校正步长为0.05 dB,最大校正量为0.5 dB,通过寄存器位(GAIN CORRECTION)进行控制。

3. 抽取滤波器

支持对ADC输出数据进行抽取,并可选择内置低通、高通或带通滤波器。抽取率和滤波器类型可通过寄存器位(DECIMATION RATE)和(DECIMATION FILTER TYPE)进行选择。默认情况下,抽取滤波器禁用,可通过寄存器位启用。

八、电路板设计要点

1. 接地

采用单个接地平面,同时对电路板的模拟、数字和时钟部分进行清晰分区,可获得良好的性能。具体布局和接地细节可参考EVM用户指南(SLAU237)。

2. 电源去耦

由于ADS62P15内部已包含去耦功能,外部去耦电容可适当减少。去耦电容应靠近转换器电源引脚放置,以过滤外部电源噪声。建议为模拟和数字电源引脚使用单独的电源,以隔离数字开关噪声。

3. 暴露热焊盘

为了获得最佳热性能,需将封装底部的暴露焊盘焊接到接地平面。详细信息可参考应用笔记QFN布局指南(SLOA122)和QFN/SON PCB附件(SLUA271)。

ADS62P15以其卓越的性能、丰富的功能和灵活的配置方式,为电子工程师在数据采集系统设计中提供了强大的支持。在实际应用中,工程师们需要根据具体的需求和系统要求,合理选择和配置ADS62P15,以充分发挥其优势,实现高性能的数据采集和处理。你在使用ADS62P15或者其他类似ADC的过程中,遇到过哪些挑战呢?欢迎在评论区分享你的经验和见解。

-

adc

+关注

关注

100文章

7945浏览量

556862 -

模拟信号

+关注

关注

8文章

1236浏览量

54786 -

带通滤波器

+关注

关注

18文章

270浏览量

44834 -

数字转换器

+关注

关注

0文章

348浏览量

28862

发布评论请先 登录

TI推出业界最快速的双通道14位元ADC -ADS62P49

双通道11位125MSPS模数转换器ADS62P15的详细资料概述

ADS62P2X 系列双通道12位ADC数据手册总结

深入解析ADS5517:高性能11位200 MSPS ADC的卓越之选

深入解析ADS7852:高性能12位8通道ADC的卓越之选

深度解析ADS62P15:高性能双通道11位ADC的卓越之选

深度解析ADS62P15:高性能双通道11位ADC的卓越之选

评论