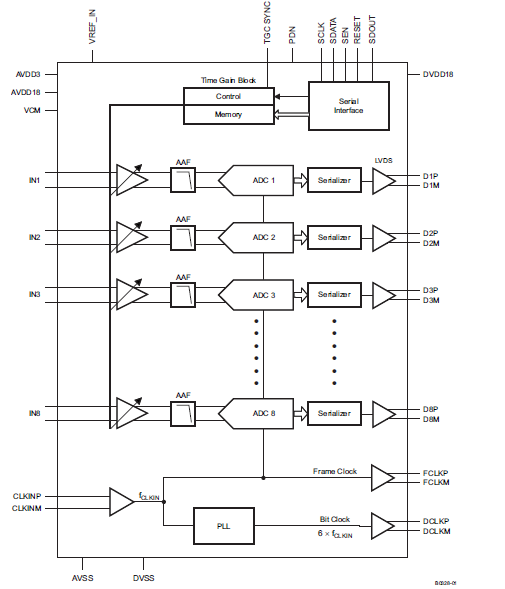

AFE5801是模拟前端,面向性能和集成水平至关重要的应用。该器件包含八个可变增益放大器(VGA),每个放大器后面跟一个高速(最高65MSPS)ADC,每件设备共计八个ADC。

八个差分输入中每个都有缓冲,最大响应2Vpp的输入摆幅,随后是增益范围从–5dB到31dB的VGA。VGA增益通过数字控制,增益曲线随时间的变化可以通过串行接口存储在设备内集成的内存中。

*附件:afe5801.pdf

VGA和ADC之间还集成了一个可选的钳形和抗锯齿低通滤波器(在7.5MHz、10MHz或14MHz处有3dB衰减)。

VGA/抗锯齿滤波器输出为差分式(限制为2Vpp),驱动板载12位、65MSPS ADC。如果选择较低采样率,ADC还会降低功耗。ADC输出以LVDS流串行化,进一步减少了功耗和板块面积。

该AFE5801采用64针QFN封装(9毫米×9毫米),并适用于整个工业温度范围(–40°C至85°C)。

特性

- 八个可变增益放大器(VGA)

- 八个差分缓冲输入,最大摆幅为2Vpp

- 5.5nV/√Hz VCA输入噪声(31dB增益)

- 可变增益,从–5dB到31dB,阶梯为0.125dB或1dB

- 数字增益控制

- 带有可编程截止频率(7.5、10或14MHz)的三阶抗锯齿滤波器

- 夹 紧

- 模数转换器(ADC)

- 八进制信道,12位,65MSPS

- 内部与外部参考支持

- 引用无需外部解耦

- 串行LVDS输出

- 1.8V和3.3V电源

- 每通道总功率50mW,30MSPS

- 每信道总功率58mW,50MSPS

- 64QFN封装(9毫米×9毫米)

- 应用

- 影像学:超声、PET

- 应用

- AFE5851:16通道VGA + ADC,32.5MSPS/通道

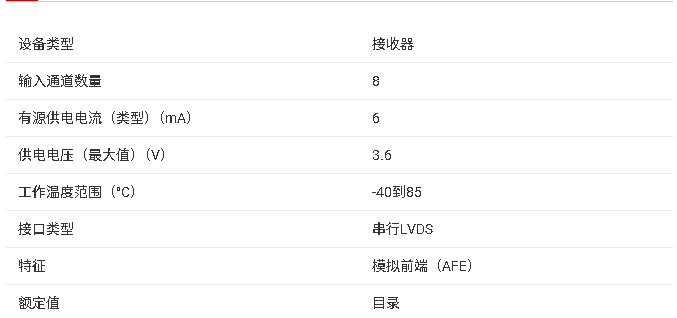

参数

一、产品核心概述

AFE5801 是德州仪器推出的高集成度模拟前端,专为超声、PET 等成像应用设计,核心优势为八通道同步信号调理与高速采样。产品集成 8 路可变增益放大器(VGA)+ 12 位 ADC,最高采样率 65MSPS,工作温度范围 -40°C~85°C,采用 64 引脚 QFN 封装(9mm×9mm),支持 1.8V 模拟 / 数字供电与 3.3V 模拟供电,单通道功耗低至 50mW(30MSPS),总功耗典型 522mW,集成抗混叠滤波器、钳位电路与 LVDS 串行输出,适用于多通道高速数据采集场景。

二、关键特性与规格

1. 核心性能参数

- 分辨率与线性度 :12 位 ADC,无丢失码;通道间增益匹配最大 0.6dB,增益误差 ±1.8dB(增益 > 28dB 时),偏移误差 ±50 LSB(31dB 增益),动态性能优异。

- 动态性能:信噪比(SNR)典型 66dBc,无杂散动态范围(SFDR)65dBc,总谐波失真(THD)64dBc,输入等效噪声 5.5nV/√Hz(31dB 增益),串扰 -92dB,抗干扰能力强。

- 输入与增益:八通道差分输入,最大输入摆幅 2Vpp(共模电压 1.6V);VGA 增益范围 -5dB

31dB,分辨率 0.125dB/1dB 可选,支持数字增益(0dB6dB,0.2dB 步进)。 - 滤波与防护:集成三阶抗混叠滤波器(AAF),截止频率可选 7.5/10/14MHz;内置钳位电路(可禁用),过载恢复时间 ≤1 时钟周期,适配强干扰场景。

2. 核心功能

- 多通道同步:八通道同步采样,孔径延迟匹配 ±150ps,群延迟变化 ±3.5ns,保证多通道信号相位一致性。

- 灵活工作模式:支持非均匀增益、均匀增益、静态 PGA 三种 TGC 模式,增益曲线可存储于内置内存,支持硬件 / 软件同步触发。

- 低功耗设计:支持全局掉电、单通道掉电与待机模式,掉电功耗低至 8mW;LVDS 输出支持 2 通道复用 1 路数据流,进一步降低功耗与布线面积。

- 数字信号处理:集成通道平均、数字高通滤波、偏移校正功能,数据格式支持二进制补码 / 偏移二进制,可输出测试图案用于调试。

三、封装与引脚

1. 封装信息

- 64 引脚 QFN 封装:尺寸紧凑,底部带散热焊盘(接 AVSS);MSL 等级 3,支持 260°C 回流焊,符合 RoHS 标准,散热性能优异(θJA=23.17°C/W)。

2. 关键引脚功能

- 电源与地:AVDD18(1.8V 模拟供电)、AVDD3(3.3V VGA 供电)、DVDD18(1.8V 数字 / LVDS 供电);AVSS(模拟地)、DVSS(数字地),建议单点共地。

- 输入与基准:IN1P/M

IN8P/M(八通道差分模拟输入);VREF_IN(外部基准输入,1.35V1.45V),支持内部 / 外部基准切换。 - 控制与输出:SCLK/SDATA/SEN(串行配置接口)、RESET(复位)、PDN(全局掉电)、SYNC(TGC 同步触发);D1P/M~D8P/M(LVDS 数据输出)、DCLKP/M(位时钟)、FCLKP/M(帧时钟)。

四、工作模式与核心功能

1. 核心工作模式

- TGC 增益模式:非均匀模式(自定义增益 - 时间曲线,148 个寄存器存储)、均匀模式(固定斜率增益 ramp)、静态模式(固定增益,粗调 1dB + 细调 0.125dB)。

- 采样输出模式:最高 65MSPS 采样率,ADC 延迟 11 时钟周期;LVDS 输出支持 12/10/16/14 位序列化,帧时钟对齐 12 位数据边界,支持双通道复用输出。

- 低功耗模式:全局掉电(全功能关闭)、单通道掉电(独立关闭指定 VGA+ADC)、待机模式(快速唤醒),适配不同功耗需求。

2. 关键功能

- 抗混叠滤波:三阶低通滤波器,阻带衰减 ≥95dB,有效抑制高频噪声混叠,无需外部滤波电路。

- 钳位与过载恢复:钳位电平限制在 ADC 满量程 +3dB,快速恢复过载信号,避免器件损坏,适配超声发射脉冲馈通场景。

- 串行配置:24 位串行接口(SCLK 最高 20MHz),支持寄存器读写,可配置增益、滤波、输出格式等参数,灵活适配不同应用。

五、应用场景与设计支持

1. 典型应用

2. 设计资源

- 电源与去耦:模拟与数字电源独立供电,各电源引脚就近并联 0.1μF 陶瓷电容,嘈杂环境可添加 1μF~10μF 钽电容滤波。

- 布局要点:模拟地与数字地单点共地,输入走线远离数字 / 时钟信号;LVDS 走线阻抗控制 100Ω 差分,长度误差 ≤3.81mm,保证时序一致性;散热焊盘需大面积接地。

- 时钟设计:支持差分(LVDS/LVPECL)或单端(LVCMOS)时钟输入,单端时钟需将 CLKINM 接 AVSS,差分时钟建议 AC 耦合(0.1μF 电容)。

- 输入驱动:模拟输入需 AC/DC 耦合至 1.6V 共模电压,AC 耦合电容建议 ≥10nF(适配 >1MHz 信号),源阻抗需匹配 5kΩ 内部偏置电阻。

六、可靠性与订单信息

- 可靠性保障:绝对最大额定值:AVDD3 3.8V,AVDD18/DVDD18 2.2V,引脚电压 -0.3V~3.6V,结温 125°C,ESD 防护符合工业标准。

- 可订购型号:AFE5801IRGCT(卷盘装 250 片)、AFE5801IRGCR(卷盘装 2000 片),引脚镀层 NIPDAU,MSL 等级 3(260°C 回流焊,168 小时防潮)。

-

MSPS

+关注

关注

0文章

574浏览量

28783 -

adc

+关注

关注

100文章

7451浏览量

553867 -

增益放大器

+关注

关注

2文章

179浏览量

30016 -

模拟前端

+关注

关注

3文章

295浏览量

30845

发布评论请先 登录

使用AFE5801器件的时候,如何转换所读取到的数据?

请问AFE5801的输出是如何进行差分到单端的处理进FPGA的?

用FPGA采集AFE5801输出信号,信号波形严重畸变的原因?

请问AFE5801的输入输出可以直接和FPGA的IO连吗?

不管是LTC6912还是AFE5801通过SPI总线对reg进行写的时候,在写的过程中,AFE5801还在工作状态吗?

AFE5801,pdf(8-Channel Variable

AFE5801 EVM User Guide

包含八个可变增益放大器的模拟前端AFE5801的详细资料概述

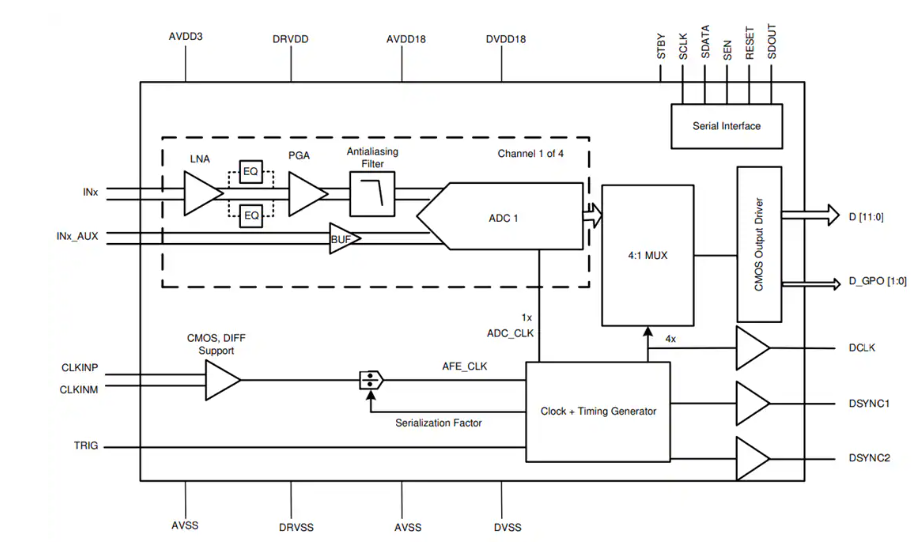

Texas Instruments AFE159x 4通道24位模拟前端(AFE)数据手册

Texas Instruments AFE5401-EP四通道模拟前端 (AFE)数据手册

AFE5801 八通道 12 位 65MSPS 模拟前端(AFE)产品手册总结

AFE5801 八通道 12 位 65MSPS 模拟前端(AFE)产品手册总结

评论