引言

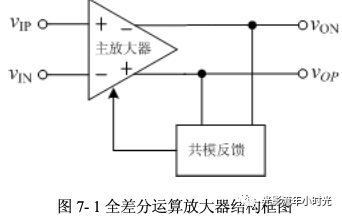

全差分运放(fully differential operation)相对于单端输出电路来说,不仅输出摆幅更大、共模噪声抑制更好,还能消除高阶谐波失真。然而,在高增益运放中,输出共模电平对器件的特性和失配相当敏感,而且不能通过差模反馈来达到稳定。因此,必须额外引入负反馈机制,即共模反馈(CMFB)来稳定运放的共模输出电平。共模反馈的基本原理是先通过检测网络得到输出共模电平Vo_cn,然后将Vo_cn和一个参考电压Vcn(一般为电源电压的一半)相比较,再用得出的误差信号来调节运放的偏置电流,从而达到使输出共模信号稳定的目的。这种方式的设计要点如下:

(1)共模信号检测应具有线性特性;

(2)共模反馈环路的增益必须尽可能的高;

(3)反馈环路的带宽不能小于差模通路(在许多实际应用中,这两个带宽必须一致);

(4)确保共模环路稳定;

(5)应引入保护机制,以避免“锁死状态”的出现(输出保持在电源电压的情况)。

目前已经有了大量关于差模反馈环路稳定性的理论研究,而对于共模反馈环路的研究却很少。现有的共模反馈电路的设计更多的是通过实际经验、反复调试来得到稳定环路。笔者通过对最常用的、采用一级共模反馈的两级运放的环路进行稳定性分析,明确得出了其稳定条件,从而理论化了共模反馈电路的设计。然后基于这个条件,并采用Bi-CMOS工艺设计了一种低成本、高稳定、匹配好的共模反馈电路。整个运放可应用于一款高性能音频CLASS-D芯片。

1共模反馈环路分析及稳定条件

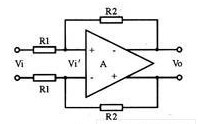

图1所示是全差分运放的一种典型应用电路。该电路*有三个环路:差模环路、共模反馈外环(结构相同,由R1、R2及运放本身构成);以及共模反馈内环(运放内部自带)。只有在三个环路均稳定的条件下,该运放才能正常工作。须特别注意的是:对于两级运放,共模反馈外环是一个正反馈。因为信号经过运放内部的两次反相后。共模信号从Vo反馈到Vi,是同相的,但对差模信号则是反相的。实际应用中,运放的输入端可能出现非常大的共模电平(使它是瞬时的),这将导致输入对管关断,输出电平接近电源电压。由于此时差模回路中断,整个外环呈现共模正反馈。这就会使运放呈现“锁死状态”。由于这种情况很可能发生在电路的启动过程。因此,对于共模环路的稳定性研究很有必要。

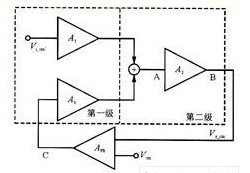

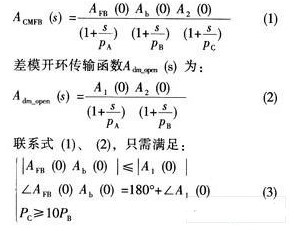

图2所示是采用一级共模反馈的两级运放的典型拓扑结构。其中Vi_cm、Vo_cm一分别为运放的输入、输出共模信号。A1、A2为运放的第一、二级。一般对两级运放多采用密勒补偿,使A点为主极点,B点为次主极点。AFB处设定比较电平Vcm(以下称之为共模反馈运放);Ab为共模内环与差模第一级的相交部分。各子运放均为单级运放,并假定它们内部的零、极点均远远大于带宽。共模反馈信号通过调节运放第一级的偏置电流,可以达到稳定第一、二级输出共模电平的目的。这个拓扑结构将三个环路紧密联系起来,其共模环路完整包括了运放的第二级和运放差模通路的主、次极点,而忽略了带宽外零极点。逐一分析三个环路,即可得出其共模环路的稳定条件。

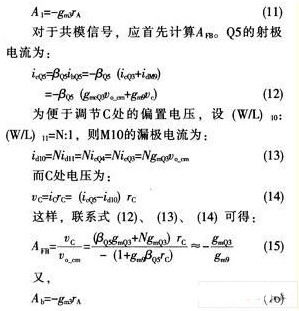

首先分析运放本身。其共模反馈内环传输函数ACMFB(s)为:

即可保证在差模开环稳定时,其共模内环也稳定。

继续分析由运放构成的环路。系数为β(一般地,β≤1),那么,输函数Adm_loop(s)为:其共模内环也设运放的反馈其差模环路传输函数Adm_loop(s)为:

即可保证共模外环的稳定。

联系式(3)、(5)、(1 0),可以得到该拓扑结构共模环路的稳定条件如下:

(1)运放的差模开环稳定;

(2)AFB(0)、Ab(0)与A1(0)满足相位相差180°、绝对值近似相等:

(3)共模反馈额外引入的极点不影响环路带宽。

基于上述条件可见,共模环路无需额外补偿。由于整个运放仅额外引入运放AFB,因此成本低、设计简单,且共模内环带宽与差模开环相等、增益相近,故能满足共模反馈设计要点(2)、(3)、(4)。

2低成本高稳定的共模反馈电路

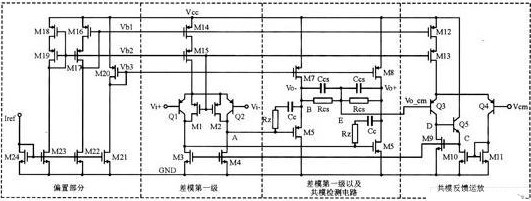

图3是本文所设计的两级全差分运放电路。该电路的共模反馈部分结构新颖、成本低、匹配好,基于图2的拓扑结构,可满足本文提出的稳定条件。图3中,Iref为基准电流,两级运放采用RZ和Cc组成密勒补偿,来满足稳定条件(1)。为了减小失调,运放的第一级和共模反馈运放采用三极管(Q1~Q4)作为输入对管。

电路中的Ml、M2分别与Ql、Q2并联,其栅极信号Vb2随电源电压的升高而升高,其作用相当于在输入级增加两个比较器。正常工作时,M1、M2关断,Ql、Q2处理信号,而在电源电压较低(启动时)以及输入信号的共模电平高于Vb2比时,Q1、Q2关断,M1、M2线性导通,以稳定环路各级共模电平。从而有效避免了电路启动过程锁死状态的出现,满足了设计要点(5)。

共模检测电路由电阻Rcs并联Ccs来完成。引人后者的目的是在高频时既可旁路电阻的寄生电容,又可产生一个零点。以阻止共模增益的降低,从而满足设计要点(1)。

共模反馈运放在Q3、Q4、M10、Mll组成的普通电流镜结构基础上,还额外增加了Q5和M9两个器件。Q5作为射随器可将原电流镜结构中的高阻、大电容输出结点分隔为C、D两点。分隔后,相对于两级运放的主、次极点A、B,D点,其电容减小(仅有寄生电容),而C点阻抗减小(连接Q5的射极),所以,C、D两处极点均不影响环路带宽,可满足稳定条件(3)。接着比较两者的增益,其差模第一级增益为:

联系式(11)、(15)、(16)可见,只需Q1~Q4,M3、M4、M9、M11以及M12~M15尺寸对应

在式(11)~(17)中,rA、rC、VA、VC分别为结点A、C处的小信号电阻值和电压值。

式(17)表明共模环路增益与差模开环增益绝对值近似相等、相位相差180°,可满足稳定条件(2)。由此,本电路已可同时满足本文提出的3个稳定条件以及5个共模反馈设计要点。

传统的共模反馈运放一般采用电流镜和二极管作为负载。即使严格按照稳定条件进行设计,由于电路的不匹配(共模反馈运放的结构、尺寸与差模第一级不相同),将导致器件的短沟道效应相异、工艺失配的差异较大,从而使得共模内环与差模开环的增益不可避免的存在偏差,因此,传统电路不能很好的满足稳定条件。

而本文提出的共模反馈运放电路匹配高、版图匹配容易。由式(15)可知,运放的右半电路几乎不影响运放的增益,且对C处偏置电压的影响也较小(受Q5和M9组成的负反馈作用)。所以,在平衡条件下,右半部分器件的短沟道效应及工艺失配带来的影响可以忽略。而运放的左半边电路以及尾电流源与差模第一级对应匹配,因而其短沟道效应也相近。因此只需使这部分器件的版图采用对称放置来设计,即可使它们的工艺匹配良好,从而确保电路严格满足稳定条件。

3仿真结果

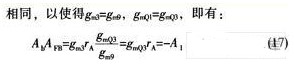

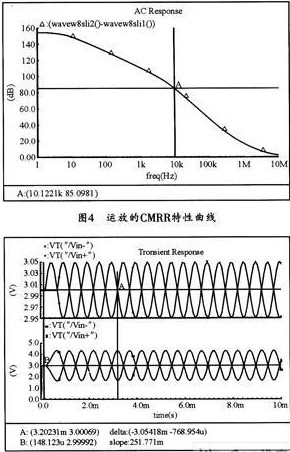

本电路的设计主要基于TSMC 0.5um BiCMOS工艺,电源电压为6 V。所有波形均可在Spectre下仿真所得。仿真结果表明,在开环条件下,该运放的正、负端增益相同,相位相差180°,而且电路匹配良好,输出精确平衡。图4所示是该运放的共模抑制比(CMRR)特性曲线。由图可见,在10kHz时,该电路的CMRR依旧高达85 dB。事实上,该运放已实际应用于一款高性能音频CLASS—D芯片之中。图5是其作为积分器处理音频数据的瞬态仿真波形,其中输入信号是3 V共模电平,幅度为50 mV,频率为1 kHz的正弦信号。输出信号为频率不变,幅度为3 V的余弦信号,其共模电平稳定在3 V,从而表明该运放工作良好。

4结束语

本文分析了全差分运算放大器的共模反馈原理,研究了采用一级共模反馈的两级运放拓扑结构并得出其稳定条件。基于这个条件,文章又提出的一种结构新颖、电路匹配良好、输出平衡高的共模反馈方案。整个运放现已用于一款高性能音频CLASS—D芯片。经Spectre仿真验证,本运放工作稳定,输出精确平衡。

-

芯片

+关注

关注

447文章

48015浏览量

410388 -

运算放大器

+关注

关注

211文章

3993浏览量

170814 -

仿真

+关注

关注

50文章

3876浏览量

132261

发布评论请先 登录

相关推荐

采用CLASS—D芯片构成全差分运算放大器的共模电路设计及仿真研究

采用CLASS—D芯片构成全差分运算放大器的共模电路设计及仿真研究

评论