继储存型快闪存储器价格走跌之后,原本报价尖挺的DRAM也开始松动,其中,连续八季涨价的DDR3率先走跌,***包括晶豪科、南亚科等业者都以DDR3为主要产品,将首当其冲。

存储器通路商透露,受虚拟货币挖矿机对DRAM拉货需求转弱,以及用户端转向主流DDR4 DRAM影响,连绩八季走高的DDR3近期报价开始走跌,是存储器产业在价格连续二年走坚后,首见疲态,是否会掀起骨牌反应,值得密切注意,但已为存储器产业攀高峰添变数。

集邦科技旗下存储器储存研究昨(6)日最新调查报告也指出,比特币价格虽止跌反弹,但存储器需求量高的乙太币矿机E3,受乙太币持续跌价影响,原本预期今年下半年会出现的强劲拉货动能已消失,连带让DDR3 1Gb的价格上涨预期落空。

DRAMeXchange认为,在乙太币价格回升到一定水位,或在支援高颗数存储器的全新挖矿机种出现前,所带起的存储器拉货热潮恐暂告一段落。

-

DRAM

+关注

关注

40文章

2373浏览量

188162 -

DDR3

+关注

关注

2文章

287浏览量

43933

原文标题:DRAM价格松动,八季度涨价的DDR3价格走跌

文章出处:【微信号:ic-china,微信公众号:ICExpo】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于DDR200T开发板的e203进行DDR3扩展

DDR200T中的DDR3的使用配置

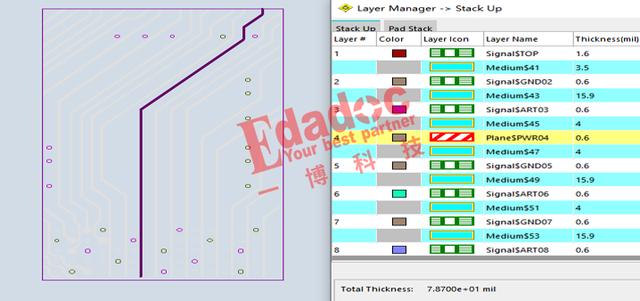

AD设计DDR3时等长设计技巧

AD设计DDR3时等长设计技巧

看点:三星DDR4内存涨价20% 华为与优必选全面合作具身智能

DDR4涨价20%,DDR5上调5%!

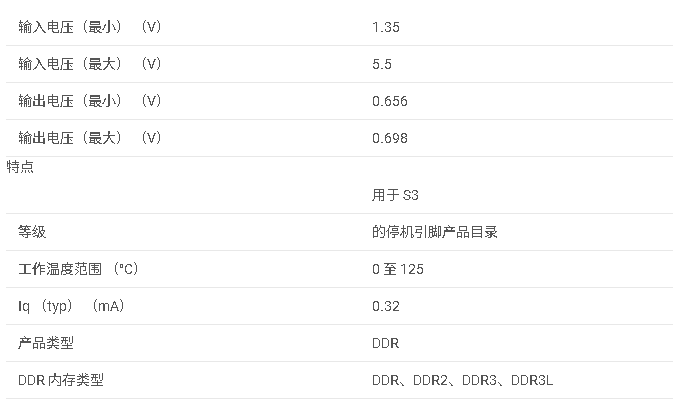

TPS51116 完整的DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据手册

LP2996A 1.5A DDR 终端稳压器,带关断引脚,用于 DDR2/3/3L数据手册

DDR3 SDRAM配置教程

DRAM开始松动,连续八季涨价的DDR3率先走跌

DRAM开始松动,连续八季涨价的DDR3率先走跌

评论