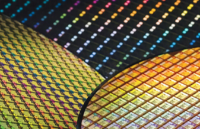

半导体晶圆抛光技术面临多重挑战,这些挑战源于工艺精度提升、新材料应用及复杂结构的集成需求。以下是主要的技术难点及其具体表现:

纳米级平整度与均匀性控制

原子级表面粗糙度要求:随着制程节点进入7nm以下,晶圆表面需达到亚纳米级的平整度(如RMS<0.2nm),这对化学机械抛光(CMP)设备的参数调控提出极高要求。例如,压力、转速和抛光液流量的微小波动都可能导致局部高低差,影响后续光刻成像质量;

微观结构区域的均匀去除:在三维集成电路(如FinFET晶体管或3D NAND闪存)中,不同材料的交叠区域存在物理特性差异,如何实现全局与局部同步平坦化成为关键难题。例如,多层金属互连层间的软硬材质交替分布易造成抛光速率不均。

材料多样性带来的适配难题

高硬度材料的低效率加工:第三代半导体材料(如碳化硅SiC、氮化镓GaN)硬度远超传统硅基材料,其研磨效率仅为硅的十分之一左右。常规磨料难以有效去除表层材料而不引入损伤,需开发激光辅助或等离子体刻蚀等复合工艺;

化学敏感性与副反应抑制:新型高介电常数材料、金属栅极材料对抛光液成分高度敏感,易产生表面缺陷或残留反应产物。例如,某些络合剂可能腐蚀特定金属层,导致电路性能下降。

超薄晶圆处理中的机械稳定性问题

碎片风险与应力管理:当晶圆厚度减薄至50μm以下时,机械强度急剧下降,加工过程中极易发生断裂。同时,机械研磨产生的残余应力可能引发微裂纹扩展,威胁器件可靠性;

临时键合技术的局限性:为支撑超薄晶圆进行的临时粘贴与解键合操作,需确保粘合剂完全剥离且不留残留物,否则会影响后续封装良率。

缺陷控制与污染管理

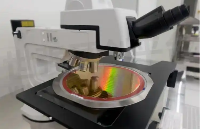

微划痕与颗粒残留检测:抛光过程中使用的纳米级磨粒若嵌入表面或聚集成团,将形成难以察觉的微观缺陷。这些缺陷可能在后续工艺中诱发漏电或断路,尤其对先进封装中的高密度互连线影响显著;

化学污染物清除难度大:抛光液中含有重金属离子和其他腐蚀性成分,若清洗不彻底会污染芯片活性区域,降低良品率。此外,抛光垫磨损产生的碎屑也可能成为二次污染源。

工艺一致性与可重复性保障

设备老化导致的性能漂移:长期使用的抛光垫因磨损导致微观结构变化,影响抛光液分布均匀性。定期修整虽能缓解此问题,但修整过程的随机性增加了工艺稳定性的控制难度;

跨批次材料的变异适应:不同供应商提供的晶圆在晶体取向、杂质浓度等方面存在差异,同一配方在不同批次间可能出现抛光速率偏差,需频繁调整工艺参数以维持一致性。

环保与成本双重压力

有害废弃物的处理成本攀升:含重金属的抛光废液需特殊处理流程,增加了制造环节的环保合规成本。行业正推动抛光液回收技术和低毒配方研发,但尚未大规模应用;

高耗材投入的经济性矛盾:高精度抛光垫、专用化学品及频繁的设备维护使得单片成本居高不下。在追求极致性能的同时,如何平衡投入产出比成为企业重要考量因素。

智能化监控与实时反馈瓶颈

终点检测精度不足:传统光学传感器难以准确判断超薄层的剩余厚度,容易导致过抛或欠抛。尽管智能系统已引入机器学习算法优化预测模型,但在复杂多层结构中仍存在误判风险;

多参数耦合效应解析困难:CMP涉及压力、温度、流速等多个变量动态交互作用,建立精确的数学模型需大量实验数据支持,而实际生产中的环境扰动进一步加剧了模型误差。

新兴应用场景的特殊需求

三维集成中的垂直贯通孔抛光:通过硅通孔(TSV)实现芯片堆叠时,需对深孔底部进行无损伤抛光,传统平面化工艺无法满足侧壁均匀去除的要求;

异质集成的材料兼容性挑战:将不同热膨胀系数的材料(如硅与化合物半导体)集成在同一封装内时,抛光应力可能导致界面分层或翘曲变形。

上述挑战推动着抛光技术向更高精度、更强适应性和更智能化五个方向发展。例如,基于分子动力学模拟的原子级去除机理研究正在突破传统理论局限;而AI驱动的自适应控制系统则有望实现工艺参数的动态优化。然而,这些创新仍需克服基础研究的滞后性和工程化落地的成本障碍。

审核编辑 黄宇

-

晶圆

+关注

关注

53文章

5344浏览量

131664 -

半导体晶圆

+关注

关注

0文章

46浏览量

5567

发布评论请先 登录

半导体国产替代材料 | CMP化学机械抛光(Chemical Mechanical Planarization)

半导体晶圆抛光有哪些技术挑战

半导体晶圆抛光有哪些技术挑战

评论