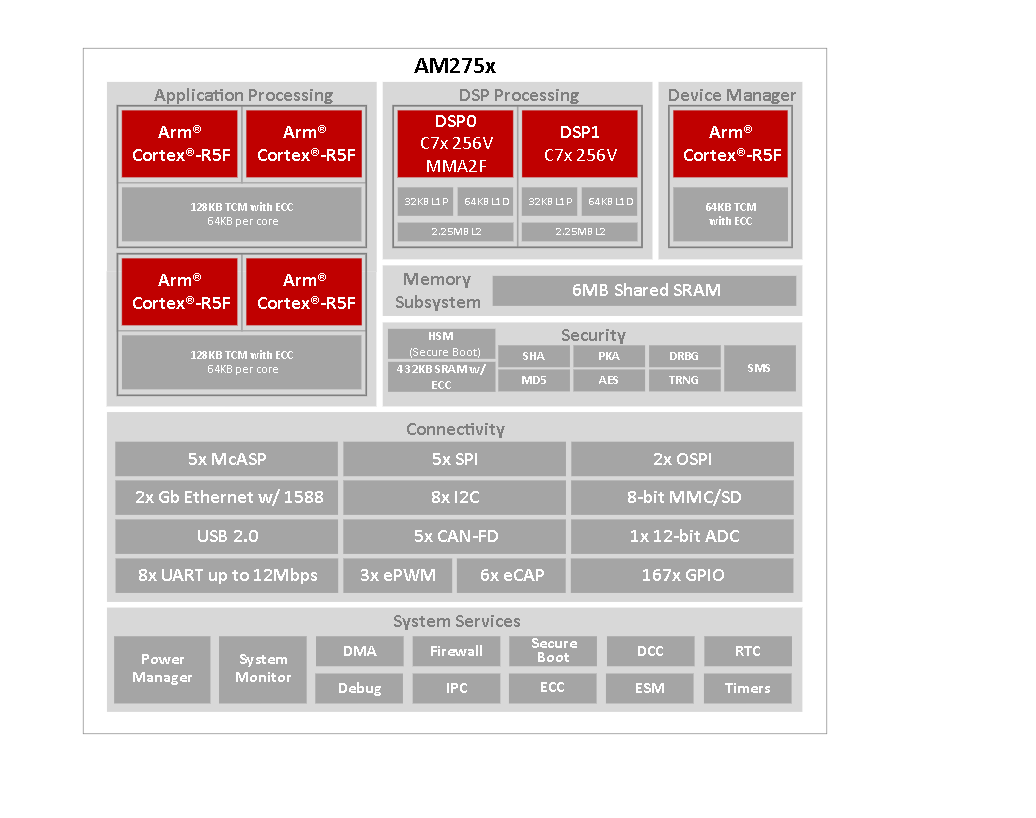

AM275x 系列高度集成、高性能微控制器基于 Arm Cortex R5F 和 C7x 浮点 DSP 内核。这些微控制器使原始设备制造商 (OEM) 和原始设计制造商 (ODM) 能够通过强大的软件支持和丰富的用户界面将设备快速推向市场。该器件提供了完全集成的混合处理器设计的最大灵活性

*附件:am2752-q1.pdf

主要特点和优点:

- 与 5 个 McASP 外设的广泛音频接口

- 支持系统级连接的外设,例如 2 端口千兆以太网、USB、OSPI/QSPI、CAN-FD、UART、SPI 和 GPIO。

- 通过内置硬件安全模块 (HSM) 支持最新的网络安全要求。

- 一个或两个双核 R5F 集群,每个集群 128KB TCM(每个内核 64KB),以及最多两个 C7x DSP 内核,每个 C7x DSP 具有 2.25MB 的 L2 SRAM,大大减少了对外部存储器的需求。

特性

- 双核或四核 Arm Cortex R5F CPU,每个内核运行频率高达 1GHz

- 32KB I-Cache,每个 CPU 内核 64 位 ECC

- 4x8KB 关联

- 单纠错、双误检测每 64 位 ECC 保护

- 32KB D 缓存,每个 CPU 内核 64 位 ECC

- 4x8KB 关联

- 单纠错、双误检测每 64 位 ECC 保护

- 每核 64KB 紧耦合内存 (TCM),具有 32 位 ECC

- 单纠错、双误检测每 64 位 ECC 保护

- 两个库,A 和 B,每个 32KB

- Bank B 分为 B0 和 B1,每个 16KB

- 128KB TCM 用于锁步模式下的 CPU0

- 高达 128KB 的远程 L2 缓存

- 32B缓存线

- 高达 128KB 的 L2 缓存,覆盖高达 16MB 的可缓存空间

- 只读、8 路缓存

- 快速本地复制 (FLC) 支持

- 对于每个集群,支持锁步或独立双核作

- 32KB I-Cache,每个 CPU 内核 64 位 ECC

- 单或双 C7x DSP 内核,每个内核运行频率高达 1GHz

- L1 内存架构

- 每个内核 32KB I-Cache

- 每个内核 64KB D 缓存

- L2 内存架构

- 2.25MB,在 L2 SRAM 上具有 ECC 保护

- 2MB“主”段

- 256KB“辅助”段

- 2.25MB,在 L2 SRAM 上具有 ECC 保护

- DSP0上的矩阵乘法加速器版本2f(MMA2F)

- L1 内存架构

- 2 个异步音频采样率转换器 (ASRC)

- 140dB信噪比(SNR)

- 每个 ASRC 最多 8 对输入和输出流(总共最多 16 个通道)

- 输入和输出采样率从 8KHz 到 216KHz

- 16位、18位、20位、24位数据输入/输出

内存子系统:

- 高达 6MB 的片上共享 SRAM

- 远程低延迟 L2 缓存 (RL2),软件可编程,从 SRAM 分配

- SMS子系统中的432KB片上SRAM

- 256KB 片上 RAM,在 SMS 子系统中具有 SECDED ECC

- 176KB 片上 RAM,在用于 TI 安全固件的 SMS 子系统中具有 SECDED ECC

- 2 个×闪存子系统 (FSS),支持高达 166MHz SDR 的八进制串行外设接口 (OSPI) 和 1.8V 和 3.3V 的 166MHz DDR,并具有完整的 XIP(就地执行),可用于

- 1 个 FSS,支持 OSPI OptiFlash 存储器技术、固件无线升级 (FOTA) 和动态高级加密标准 (OTFA)

- 1 个支持 OSPI 或 HyperRAM 的 FSS

- RAM 扩展

- 1 × 8 位多媒体卡/安全数字 (eMMC/SD) 接口

- 5 × 多通道音频串行端口 (McASP)

- 发射和接收时钟高达 50MHz

- 多达 26 个串行数据引脚,跨 5 个 MCASP,具有独立的 TX 和 RX 时钟

- 支持时分复用 (TDM)、IC 间声音 (I2S) 和类似格式

- 支持数字音频接口传输(SPDIF、IEC60958-1 和 AES-3 格式)

- 用于发送和接收的FIFO缓冲区(256字节)

- 支持音频参考输出时钟

- 8 × 通用异步 RX-TX (UART) 模块

- 5 ×串行外设接口 (SPI) 控制器

- 8 个×集成电路 (I2C) 端口

- 5 × 模块化控制器局域网 (MCAN) 模块,支持 CAN-FD

- 3 ×增强型脉宽调制 (ePWM) 模块

- 6 ×增强捕获 (ECAP) 模块

- 1 × 12 位模数转换器 (ADC),最大采样率为 4MSPS

- 多达 167 个通用 I/O (GPIO)

- 集成以太网交换机支持(总共 2 个外部端口)

- RMII (10/100) 或 RGMII (10/100/1000)

- IEEE 1588(附录 D、附录 E、附录 F,带 802.1AS PTP)

- 支持 802.1Qav (eAVB)

- 第 45 条 MDIO PHY 管理

- 基于 ALE 引擎的数据包分类器,具有 512 个分类器

- 优先级流量控制

- 四个 CPU 硬件中断起拍

- 硬件中的 IP/UDP/TCP 校验和卸载

- USB 2.0 接口

- 端口可配置为 USB 主机、USB 设备或 USB 双角色设备

- 集成 USB VBUS 检测

- 硬件安全模块 (HSM)

- 专用双核 ARM Cortex-M4F 安全协处理器,具有专用互连以确保安全

- 用于隔离处理的专用安全 DMA 和 IPC 子系统

- 安全启动支持

- 硬件强制实施的信任根 (RoT)

- 支持通过备份密钥切换 RoT

- 支持接管保护、IP 保护和防回滚保护

- 支持加密加速

- 调试安全性

- 安全的软件控制调试访问

- 安全感知调试

- 支持可信执行环境 (TEE)

- 安全存储支持

- 动态加密并支持 XIP 模式下的 OSPI 接口

- 符合功能安全标准的目标 [汽车]

- 专为功能安全应用而开发

- 提供文档以帮助 ISO 26262 功能安全系统设计

- 系统能力高达 ASIL-D 目标

- 硬件完整性达到 ASIL-B 目标

- 安全相关认证

- 计划通过 ISO 26262

- 设备管理器支持的电源模式:

- 积极

- 待机

- IO 保留

- UART

- I2C EEPROM

- OSPI NOR/NAND 闪存

- SD卡

- eMMC的

- USB(主机)大容量存储

- USB(设备)从外部主机启动(DFU 模式)

- 以太网

- 符合 AEC-Q100 标准,适用于汽车应用

- 16纳米FinFET技术

- 15.8mm x 15.8mm、0.8mm 间距 361 引脚 FCCSP

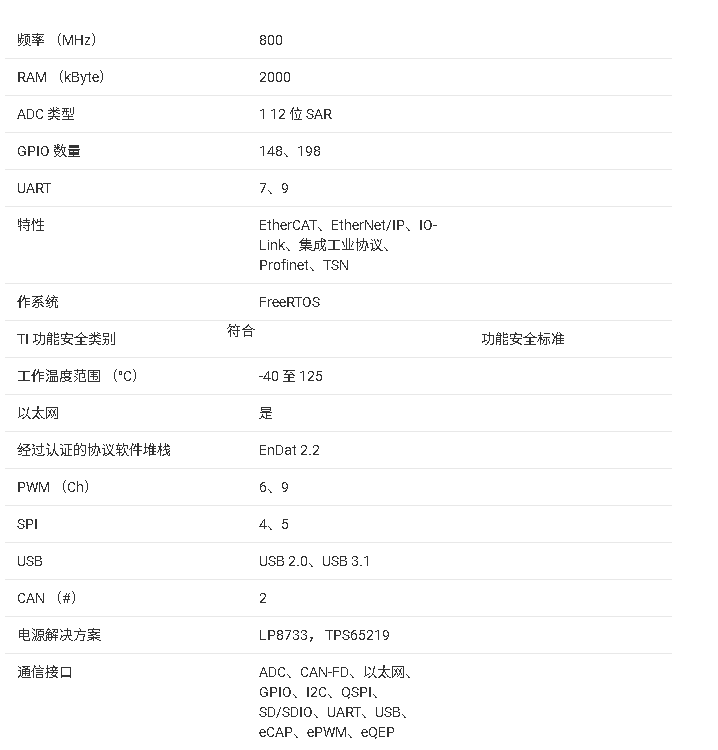

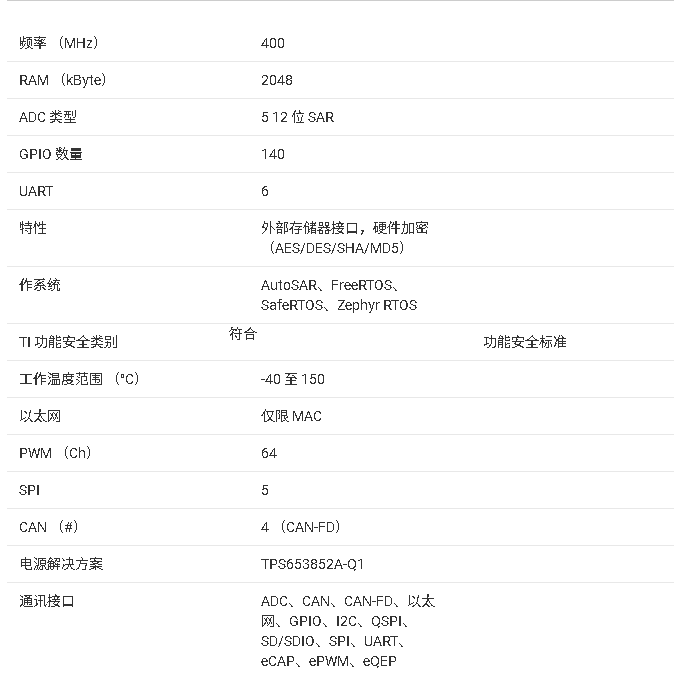

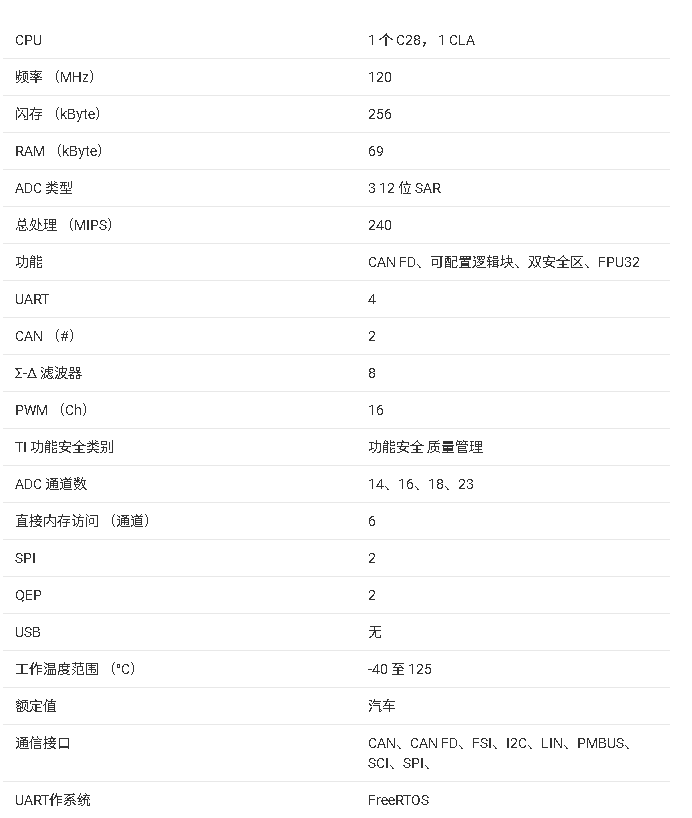

参数

方框图

1. 产品概述

AM275x是德州仪器(TI)推出的高性能多核微控制器系列,基于Arm® Cortex®-R5F CPU和C7x浮点DSP核心,专为汽车及高端音频应用设计。主要型号包括AM2754、AM2754-Q1(车规级)、AM2752和AM2752-Q1,采用16nm FinFET工艺,封装为361引脚FCCSP(15.8mm×15.8mm)。

2. 核心特性

- 处理器架构

- CPU: 双核/四核Cortex-R5F,主频1GHz,每核配备32KB I-Cache/32KB D-Cache(带ECC)及64KB TCM。

- DSP: 单/双C7x DSP核心,主频1GHz,支持MMA2F加速器,集成2.25MB L2 SRAM。

- 安全模块: 独立HSM(双核Cortex-M4F),支持安全启动、加密加速(AES/SHA/SM3/SM4)及抗侧信道攻击。

- 存储子系统

- 片上共享SRAM:最高6MB,支持ECC保护。

- 双OSPI接口:支持XIP执行、HyperRAM扩展及FOTA升级。

- 外设与接口

3. 应用场景

4. 安全与可靠性

- 符合ISO 26262功能安全标准(目标ASIL-D系统性/ASIL-B硬件完整性)。

- AEC-Q100车规认证(Q1型号),支持硬件加密与安全调试。

5. 电源与封装

- 多电源模式(Active/Standby/IO Retention),支持动态功耗管理。

- 工作温度范围覆盖汽车级要求,封装散热设计优化。

6. 开发支持

- 提供统一软件框架,支持TI安全固件及第三方工具链。

- 参考设计包括EVK原理图与BOM清单。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

微控制器

+关注

关注

49文章

8878浏览量

165731 -

处理器

+关注

关注

68文章

20333浏览量

255028 -

dsp

+关注

关注

561文章

8275浏览量

368277 -

信号处理

+关注

关注

49文章

1160浏览量

105250

发布评论请先 登录

相关推荐

热点推荐

AM2754-Q1 用于汽车音频的 80 GFLOPS DSP 微控制器数据手册

AM275x 系列高度集成的高性能微控制器基于 Arm Cortex R5F 和 C7x 浮点 DSP 内核。微控制器使原始设备制造商 (O

AM2754-Q1 用于汽车音频的 80GFLOPS DSP 微控制器技术文档总结

AM275x 系列高度集成、高性能微控制器基于 Arm Cortex R5F 和 C7x 浮点 DSP 内核。这些微控制器使原始设备制造商

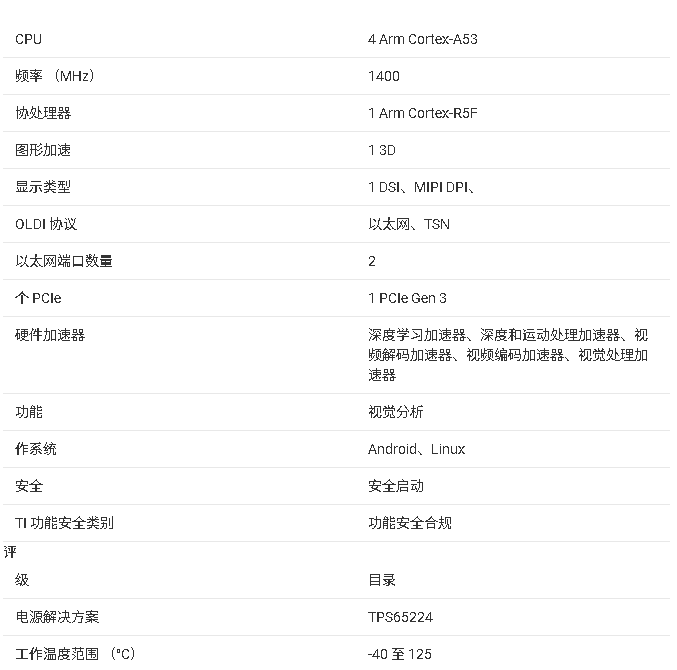

AM67x处理器技术文档总结

AM67x 可扩展处理器系列基于进化的 Jacinto™ 7 架构,面向智能视觉相机和通用计算应用,并建立在 TI 十多年来在视觉处理器市场领导地位积累的广泛市场知识之上。

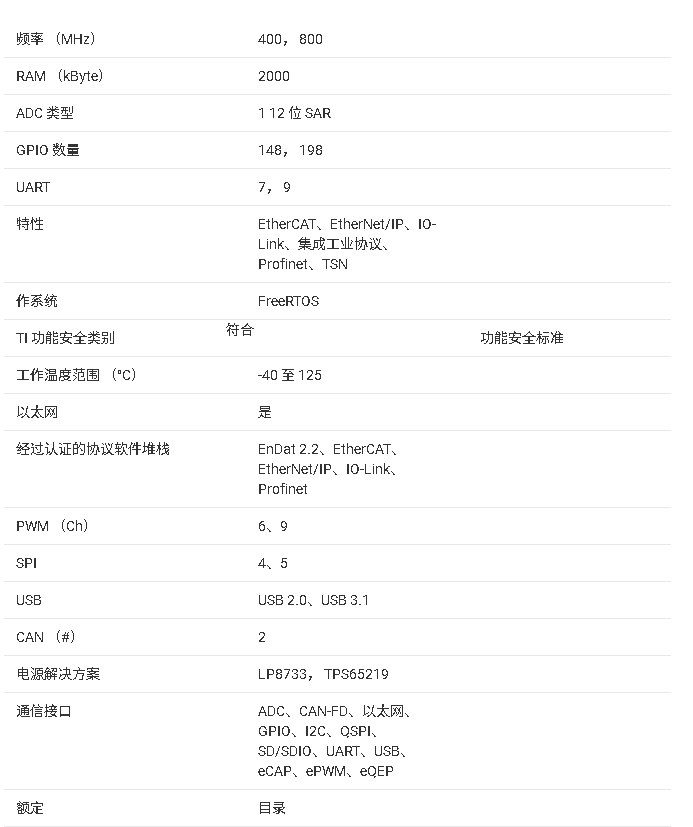

AM243x Sitara™ 微控制器技术文档总结

AM243x 是 Sitara 工业级产品组合向高性能微控制器的扩展。AM243x 器件专为工业应用而构建,例如电机驱动器和远程 I/O 模块,这些应用需要实时通信和

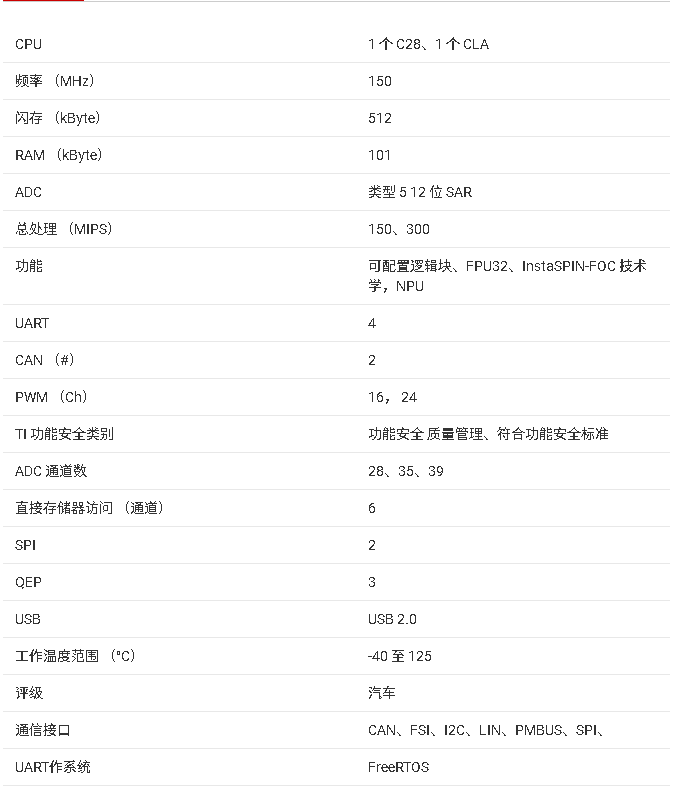

AM13E230x微控制器:高性能与多功能的完美融合

微控制器,看看它有哪些独特的特性和应用场景。 文件下载: am13e23019.pdf 一、AM13E230x微控制器概述 AM13E230x

MSP430x43x/44x系列混合信号微控制器深度剖析

MSP430x43x/44x系列混合信号微控制器深度剖析 在电子设备的设计领域,低功耗、高性能的微控制器

MSP430FW42x系列混合信号微控制器深度解析

MSP430FW42x系列混合信号微控制器深度解析 在电子设计领域,低功耗、高性能的微控制器一直是工程师们追求的目标。德州仪器(TI)的MS

深入剖析MSP430F563x系列混合信号微控制器

深入剖析MSP430F563x系列混合信号微控制器 在电子工程师的日常工作中,选择一款合适的微控制器对于项目的成功至关重要。今天,我们就来深

深入解析MSP430F42x系列混合信号微控制器

深入解析MSP430F42x系列混合信号微控制器 引言 在当今电子技术飞速发展的时代,低功耗、高性能的微

AM275x系列信号处理微控制器技术文档总结

AM275x系列信号处理微控制器技术文档总结

评论