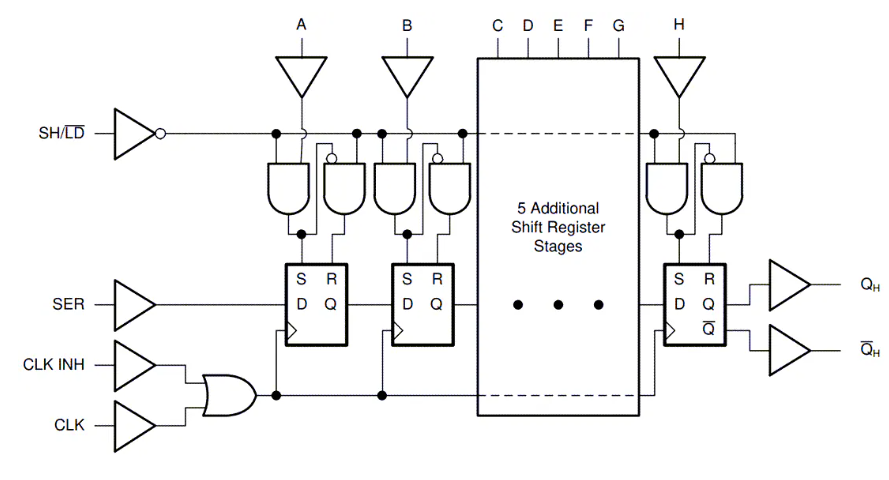

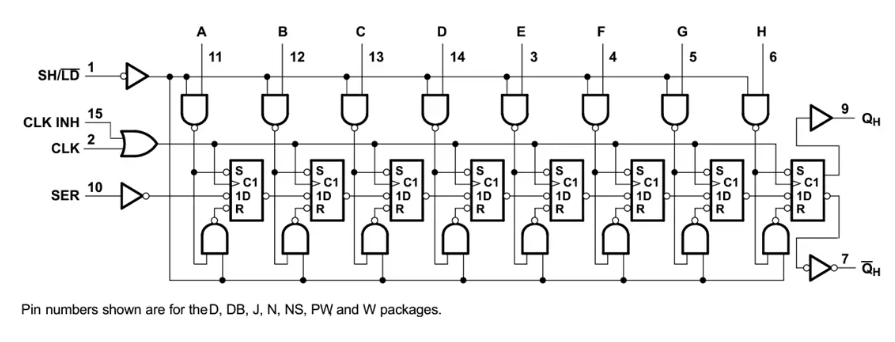

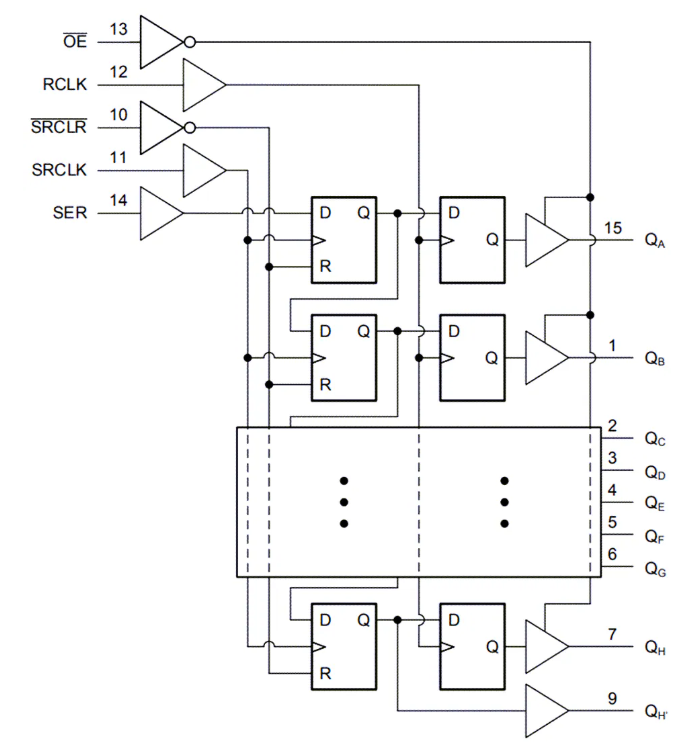

Texas Instruments SN74HCT165/SN74HCT165-Q1并联负载移位寄存器是一款并联或串联输入、串联输出8位移位寄存器。借助八个独立的直接数据 (A-H) 输入并行访问每个级,通过移位/负载 (SH/LD) 输入的低电平实现。SN74HCT165/SN74HCT165-Q1还具有时钟抑制 (CLK INH) 功能和互补串行 (Q H) 输出。Texas Instruments SN74HCT165-Q1器件符合汽车应用类AEC-Q100认证。

数据手册:

特性

- 兼容LSTTL输入逻辑

- V

IL(max)=0.8V、VIH(min)=2V

- V

- 兼容CMOS输入逻辑

- I

I≤1µA(VOL、VOH时)

- I

- 工作电压: 4.5V至5.5V

- 最多支持10个LSTTL负载的扇出

- 直接覆盖负载(数据)输入

- 门时钟输入

TA扩展环境温度范围:–40°C至+125°C

功能框图

SN74HCT165 8位并行输入移位寄存器技术解析

一、器件概述

SN74HCT165是德州仪器(TI)推出的一款8位并行或串行输入、串行输出的高速CMOS移位寄存器。该器件采用TSSOP-16封装,工作电压范围为4.5V至5.5V,具有LSTTL输入逻辑兼容性和低功耗特性。

主要特性:

- 兼容LSTTL输入逻辑(VIL(max)=0.8V, VIH(min)=2V)

- CMOS输入逻辑兼容(输入电流II ≤ 1μA)

- 4.5V至5.5V工作电压范围

- 可驱动多达10个LSTTL负载

- 工作温度范围宽达-40°C至+125°C

二、功能描述

SN74HCT165提供两种工作模式:数据加载模式和数据移位模式。

1. 数据加载模式

当SH/LD(移位/加载)输入为低电平时,器件处于并行数据加载模式。此时8个并行输入(A-H)的数据会被异步地加载到内部寄存器中。在此模式下:

- Q输出与H输入状态相同

- QH(反相输出)与H输入状态相反

2. 数据移位模式

当SH/LD输入为高电平时,器件处于数据移位模式。在时钟(CLK)上升沿触发下:

- 串行输入(SER)的数据被移入第一个寄存器

- 内部寄存器数据依次向后移位一位

- 最后一个寄存器的数据会丢失

- Q输出始终与最后一个寄存器状态相同

- QH输出为Q的反相

CLK INH(时钟禁止)输入可用于阻止时钟脉冲被检测,CLK和CLK INH是功能互换的输入。

三、关键参数

1. 电气特性

2. 时序特性

- 建立时间(tsu):25ns(CLK↑前SH/LD需保持高电平)

- 保持时间(th):9ns(数据在CLK↑后需保持稳定)

- 最小脉冲宽度(tw):25ns(CLK高或低电平持续时间)

四、典型应用

1. 微控制器输入扩展

SN74HCT165最常见的应用是扩展微控制器的输入端口。通过单个移位寄存器,可以将8个并行输入转换为串行输出,仅需占用MCU的3个I/O口(SH/LD、CLK和SER)。

2. 多器件级联

多个SN74HCT165可以级联使用,进一步扩展输入能力。前一级的QH输出连接至下一级的SER输入,所有器件的CLK和SH/LD并联连接。这种配置可以几乎无限扩展输入数量,仅受限于所需的采样速率。

应用设计要点:

- 在VCC和GND之间添加0.1μF去耦电容,应尽可能靠近器件放置

- 输出端容性负载应≤50pF以保证最佳性能

- 输出端电阻负载应大于(VCC/IO(max))Ω

- 未使用的输入端必须接VCC或GND,不能悬空

- 未使用的输出端可保持悬空

五、布局建议

良好的PCB布局对确保SN74HCT165的稳定工作至关重要:

- 推荐使用地平面铺铜,以提高信号隔离、降低噪声并改善散热

- 去耦电容应尽可能靠近器件放置

- 信号线应避免90°拐角,以减少反射

- 未使用的输入端应通过10kΩ电阻上拉或下拉,或直接连接至VCC/GND

- 未使用的输出端可保持悬空

-

并联

+关注

关注

5文章

260浏览量

37375 -

移位寄存器

+关注

关注

4文章

352浏览量

23418 -

串联输出

+关注

关注

0文章

2浏览量

5983

发布评论请先 登录

SN74HCT165 8位并行输入移位寄存器技术解析

SN74HCT165 8位并行输入移位寄存器技术解析

评论