高速先生成员--姜杰

其实,这次想聊的是差分信号通道的对称性。

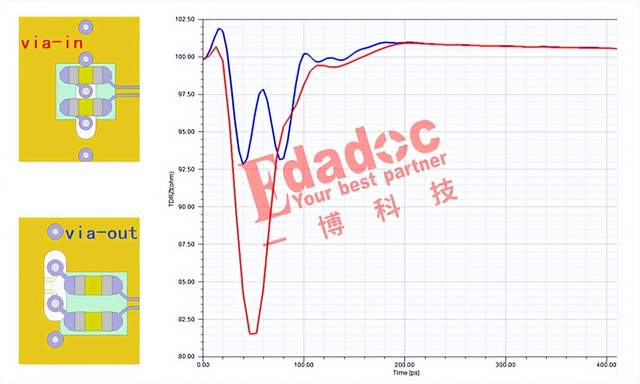

起因是高速先生前不久一篇关于AC电容的文章《为了节省AC电容打孔空间,你有没动过这个念头?》,当时从阻抗连续性的角度进行分析, 对于100欧的差分信号,via-in打孔方式的阻抗比via-out低了不少,阻抗波动较大。

结果,细心的网友又问了:如果信号差分阻抗是控85欧,via-in方式的阻抗岂不更连续?

确实是个好问题,想要解答却不容易,需要再换个角度分析。

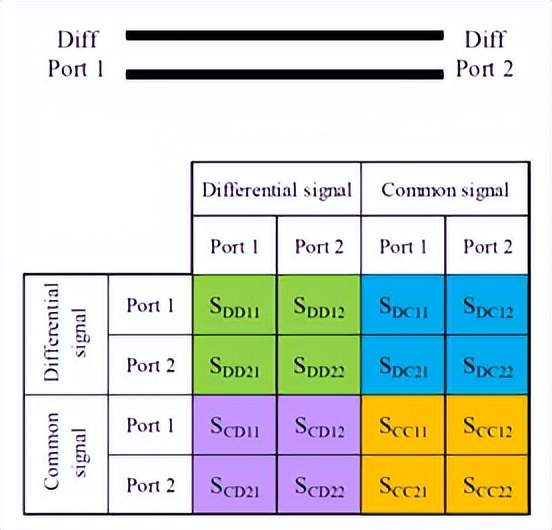

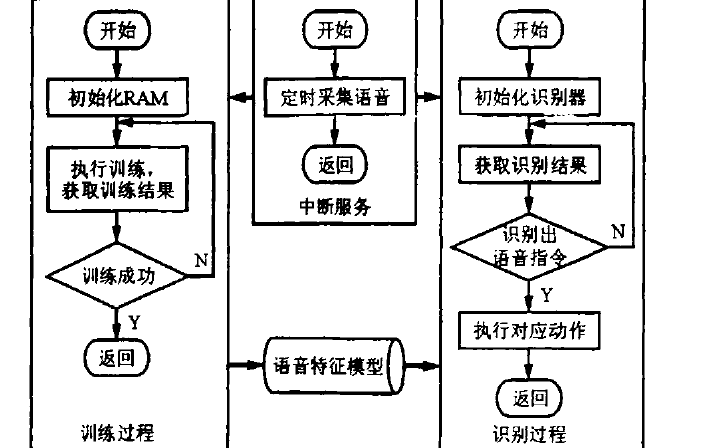

在此之前,先要了解差分信号的构成。差分信号通道传输的信号,可以分解为差分信号(Differential)分量和共模信号(Common)分量,差分信号分量携带有用信息,共模信号分量不携带信息。

理想情况下的共模信号恒定不变,此时不会产生不良影响。实际情况却是,差分信号通道上的任何不对称因素,都会导致共模信号的变化,可以理解为,通道的不对称性,导致一部分本应属于差分信号的能量转化成了共模信号。

至于共模信号分量变化的危害性,如果你知道它的另外一个名字——共模噪声,相信立马就会来了精神,而共模噪声会带来电磁干扰的风险。

简而言之,差分信号通道的不对称,导致部分有用的信号能量变成了噪声。

为了对差分信号的模态转换进行量化分析,必须搬出S参数。

其中,SCD表示差分信号输入,共模信号输出,用于衡量差分分量向共模分量的转换。

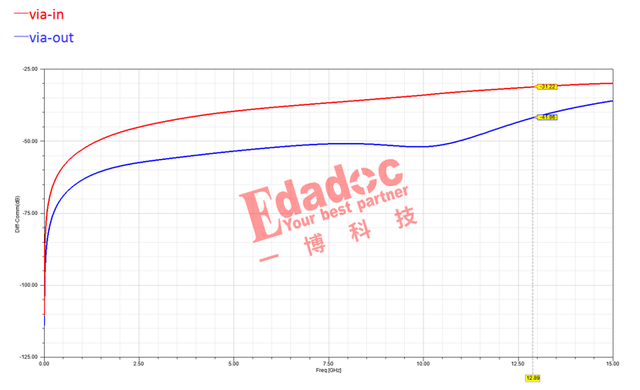

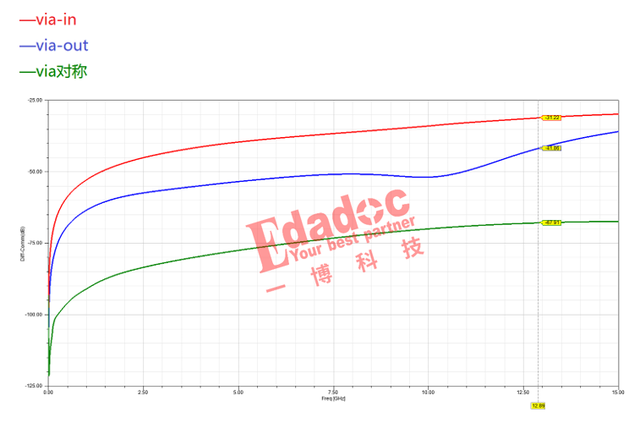

具体到AC电容的两种打孔方式。当差分走线特征阻抗为100欧时,两种情况的模态转换参数SCD21对比如下:via-in整体高于via-out,说明在关注频段内,via-in方式的差分信号转换为共模噪声的能量更多。

接下来,大家关心的85欧阻抗SCD21对比图来了:

显而易见,即便差分走线阻抗控85欧,via-in的SCD21仍然整体高于via-out近10dB,和100欧差分阻抗的情况类似。

回到文章开头,为什么说差分通道的对称性很重要?为了避免细心的网友继续追问,高速先生再做个对比,相信大家就明白了。

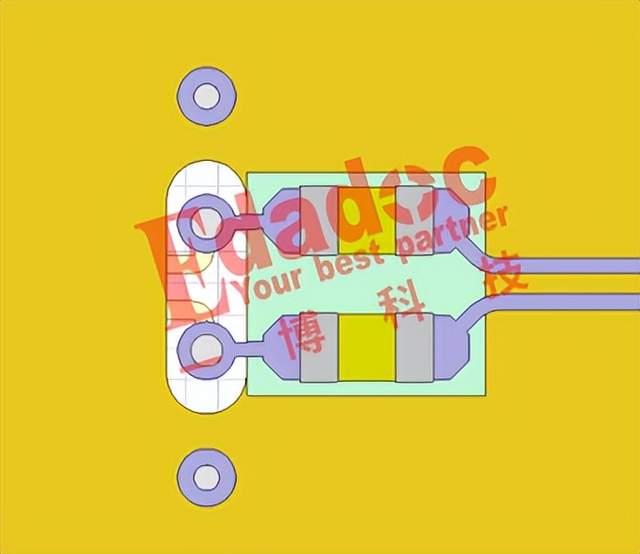

via-out的对称性只是比via-in更好,但也不是没有改进空间,起码过孔扇出可以避免45°角出线,与信号流向调整至同一直线上,从而使差分信号的N、P实现完全对称(下文简称:via对称):

85欧差分阻抗三种情况的SCD21参数对比如下:

和预期的一样,对称性最好的“via对称”,SCD21也最小。

问题来了:差分信号的对称性优化,主要从哪些方面入手?

一博科技成立于2003年3月,深圳创业板上市公司,股票代码: 301366,专注于高速PCB设计、SI/PI仿真分析等技术服务,并为研发样机及批量生产提供高品质、短交期的PCB制板与PCBA生产服务。致力于打造一流的硬件创新平台,加快电子产品的硬件创新进程,提升产品质量。

审核编辑 黄宇

-

差分线

+关注

关注

0文章

39浏览量

9281 -

PCB

+关注

关注

1文章

2347浏览量

13204

发布评论请先 登录

PADS PCB功能使用技巧系列 —— 如何走差分线?

【AD 问答8】如何画差分线

高速PCB设计中的差分线对

PADS PCB的差分线优势

传感器的选型技巧分享

差分线传输线长度差有关的问题

如何解救差分线设计错了的高速电路板

差分信号PCB布局的3大误区,不看后悔

差分线在高速PCB设计中有什么样的应用

什么是差模干扰?如何消除差模干扰?

戴尔PowerScale与Diskover Data让文件存储更加智能

PCB差分线,最重要是整整齐齐

PCB差分线,最重要是整整齐齐

评论