Nvidia刚刚发布的最强“GPU”DGX-2,由16颗V100+12颗NVSwitch芯片组成,能够提供2PFLOPS。而单颗V100的Deep Learning处理能力是120TFLOPS。如果我们要设计一颗能够实现40PFLOPS处理能力的AI芯片,该怎么操作?其实挺“简单”,把芯片面积尽可能做大。那么单个裸片(Die),最大能做多大呢?当然就是占满一片晶圆(Wafer)的面积。这就是今天要讨论的话题,Wafer Scale Integration(WSI)。

这不是一个凭空想像的话题,传说有人正在尝试一个8英寸x 8英寸的WSI。而它实现的指标就是40PFLOPS,能耗17KW(16nm工艺)。本文并不是为了讨论这个传闻,而是为了探讨WSI的可能性,毕竟之前的尝试都失败了。有个形象的感觉,我在A4纸上按照1:1的比例画了一下这个芯片的裸片(Die)想象图(面积41290.24mm2)。大家可以感受一下,差一点A4纸就放不下了。作为对比也画出了Nvidia的P100芯片的Die

(假设是正方形)(面积是610mm2)。这里用P100对比,是因为它也是用的16nm工艺。

做芯片的同学应该都了解一片晶圆只产出一个裸片意味着什么,所以当我把这张图贴到朋友圈的时候也引来了激烈的评论。除了问这是谁家的之外,问题主要围绕在良率,容错,封装,散热等话题上。当然,大家的问题都问到了点子上。

和我们之前讨论过的脉动阵列(脉动阵列 - 因Google TPU获得新生),异步电路(“传说中”的异步电路是否能在AI芯片中异军突起?)技术一样,WSI并不是什么新技术。从Wikipedia的“Wafer-scale integration”词条就可以看出它的历史。在上个世纪70和80年代,就开始有很多这方面的尝试,其目标主要是服务于超算领域(massively parallel supercomputers)。如果能够实现,好处是显而易见的,可以在一颗芯片上实现大量的运算和存储资源,而它们之间的通信可以使用芯片上相对“物美价廉”的连线资源。但是,当时的所有尝试都失败了。

在1984年的ISSCC会议上,有个关于WSI的讨论,组织者之一是David A. Patterson。在会议纪要中可以看到如下对问题的描述:

the 60s, various approaches were tried, primarily to reduce system cost. Then, the scale of integration was too low and the ratio of redundant circuits to active circuits was too high to be cost-effective compared to more direct means of improving yield.

Today, there are several additional motivations for wafer scale integration/redundancy including: system reliability; high performance through the use of very wide, fast data busses for array/systolic processors and CPUs; and system flexibility and reconfigurability.

The major issues for application of WSI include generality; technical problems such as testing and yield statistics; and practical problems such as packaging, ruggedness, repairability, and system partitioning.

而在后面的讨论中,既有乐观的看法,即未来5年内随着相关芯片技术的进步,就可以实现实用的WSI系统;也有悲观的论点,即它永远不可能成为主流的芯片技术。虽然我们很难预测未来,但至少到目前为止,后者更为准确。

虽然是冷门技术,但相信大家在看到40PFLOPS这样的指标时,还是会有兴趣再做一点深入的分析。其实我第一次听说有公司在做这东西的时候,基本是不相信的,直到从很多侧面得到了印证,才开始认真的思考它的可能性。

如前面所说,WSI最大挑战主要包括两个方面。首先是和硅片生产引入的缺陷相关的技术问题。然后是集成中面对的实际问题,包括封装,散热,供电等。我们先看看前者。

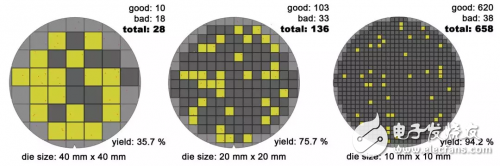

芯片生产过程中一定会产生缺陷,缺陷应该是以工艺复杂度不同而以不同概率出现在wafer上。以平均缺陷密度D0表征。一般的芯片生产中,一片晶圆都会切割出很多裸片。对于有缺陷且无法“修复”的芯片,剔除就可以了。在同样的缺陷分布情况下,晶圆上的裸片越大(分割的数量越少),缺陷的影响就越大(剔除的面积就约大)。上图就是反映良率(yield)的和裸片面积的关系。对于WSI这种一片晶圆一颗裸片的极端情况,如果剔除就是整个晶圆都浪费了。所以,如果只看一片Wafer,我们可以说它的良率是‘0%’。WSI的良率应该看所有Wafer中能够正常(或者基本正常)工作的裸片的比例。不难看出,WSI的挑战主要就是在一定会有错误的情况下,如何尽量减少错误的影响,即容错设计的问题。

对于容错设计,其实在芯片设计中是有过大量的探索和经验的,有的也相当成熟。对于运算,存储和互连中可能出现的错误及修复方法(包括硬件和软件的修复),我们可以找到很多参考。而考虑到AI芯片的一些特点,容错设计可能会相对容易处理一些。第一,AI芯片中,存储器所占比例很高,而存储器的容错设计是比较成熟的技术。第二,考虑到AI算法的特点,不论是DNN还是类脑计算(SNN),都有可能在算法层面做一些容错设计。([2]中也可以看到对此的描述)第三,AI芯片一般采用比较规则的多核架构(以NoC连接),在WSI中可以比较自然的分成不同的区域(类似于一个Wafer上虚拟的“分割”成很多裸片)。这样,即使出现无法通过软件修复的缺陷,还可以通过牺牲性能,关闭某个独立内核的方法来部分解决。

在各种缺陷当中,最为头疼的是短路问题,一旦电源地短路,整个域都会挂掉。电源地短路的可能性很多,还是相当麻烦的。这一点还不知道是否有好的办法。另一个问题是制程均一性问题,高端制程很难保证整片wafer这么大区域内器件性能一致,可能导致不同区域性能不一致,wafer中心和边缘的核心速度不一致。在这种情况下,芯片间互连需要特别处理,而系统运行和调度也很有挑战。

一些容错设计需要建立在定位缺陷的基础上,只有准确定位了缺陷的位置,才有可能实现修复。如果是同步设计,基本上现有的DFT方法问题不大,主要是测试规模的问题。另外,时间中应该会进行大量的功能测试,需要比较长的时间来进行测试,修复和调试。不过,这种规模的芯片肯定是以系统的方式销售,即使需要更多的调试时间也问题不大。

当然我们在实践中不可能做到100%容错,而最终的考量还是经济性,即付出多少代价(比如冗余的芯片面积,性能损失等等)来预防,测试和修复缺陷在经济上是可以接受的。这一部分话题挺多,以后有机会可以深入探讨一下。

-

AI芯片

+关注

关注

17文章

2065浏览量

36570

发布评论请先 登录

如何设计一颗40PFLOPS量级AI芯片_操作过程详解

如何设计一颗40PFLOPS量级AI芯片_操作过程详解

评论