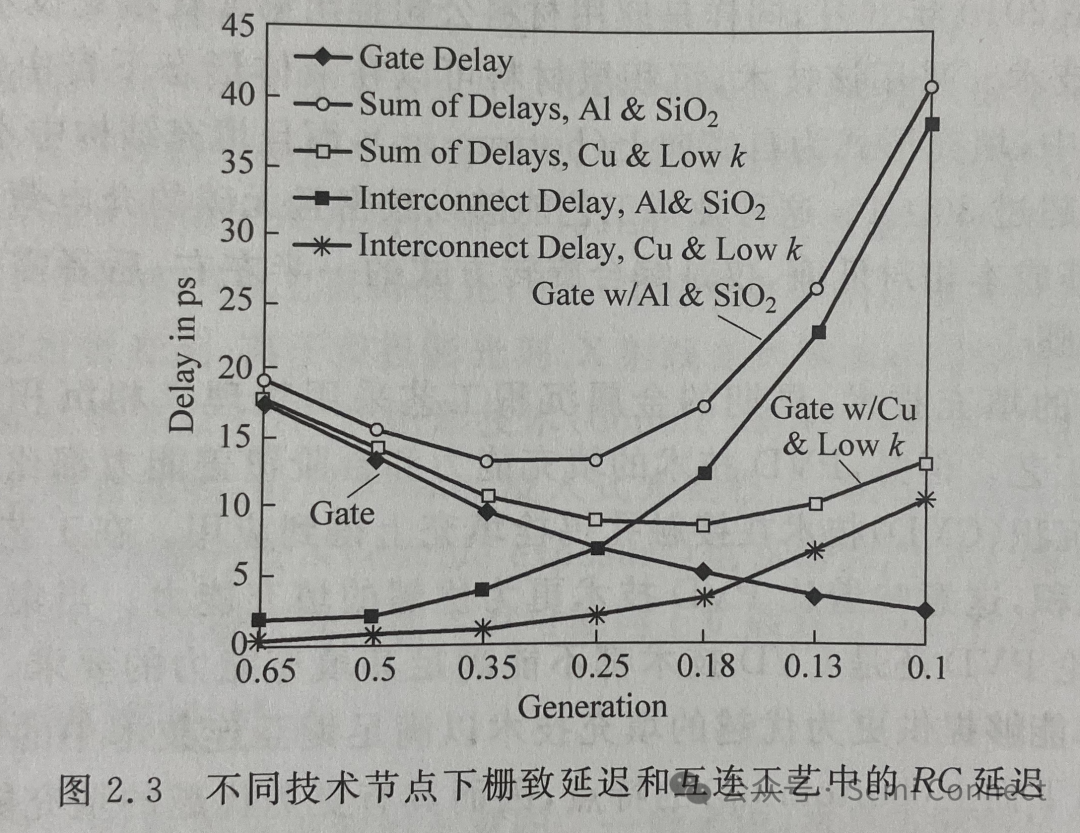

随着集成电路技术节点的不断减小以及互连布线密度的急剧增加,互连系统中电阻、电容带来的 RC耦合寄生效应迅速增长,影响了器件的速度。图2.3比较了不同技术节点下门信号延迟(gate delay)和互连层RC延迟(RC delay)。在早期,栅致延迟占主导地位,互连工艺中的RC延迟的影响很小。随着 CMOS 技术的发展,栅致延迟逐步变小;但是,RC延迟却变得更加严重。到 0.25μm 技术节点,RC延迟不再能够被忽略。

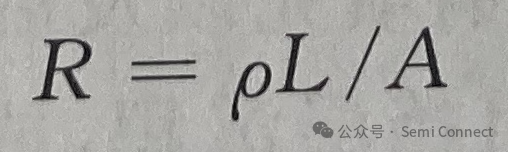

降低 RC 延迟可以分别通过降低阻抗和容抗以达到目的。首先来考察与阻抗相关的相关参数

式中,p是导线材料的电阻率,A和L 分别是与电流方向垂直的导线截面积和电流方向的导线长度。由于A和L是几何微缩过程中已经确定了的重要参数,降低阻抗R的最好的方法就是降低电阻率p值。在0.18μm 和0.13μm技术节点,工业界引入了低电阻值的铜互连线来代替铝互连技术,铜互连将至少沿用到 22nm技术节点。

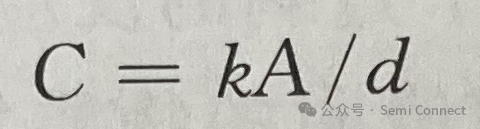

接着,来看容抗相关的物理参数

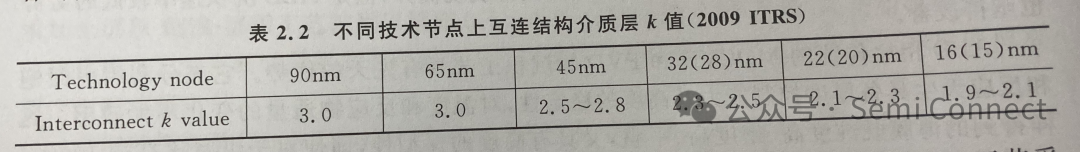

在上述等式中,k是介电材料的介电常数,A和d分别是导线之间的正对面积和导线之间的距离。同样,由于A和L是几何微缩过程中已经确定了的重要参数,工业界采用低电容的低介电常数(低k)绝缘材料,其发展趋势就是介电常数不断降低(见表2.2)。

二氧化硅的k值在4.2左右,通常通过掺杂其他元素以降低k值,比如 0.18

μm 工艺采用掺氟的二氧化硅,氟是具有强负电性的元素,当其掺杂到二氧化硅中后,可以降低材料中的电子与离子极化,从而使材料的介电常数从4.2 降低到3.6左右。

更进一步地,通过引入碳原子在介电材料也可以降低k值,即利用形成Si-C及C-C键所联成的低极性网络来降低材料的介电常数。针对降低材料密度的方法,其一是采用化学气相沉积(CVD)的方法在生长二氧化硅的过程中引入甲基(一CH3),从而形成松散的SiOC:H薄膜,也称CDO(碳掺杂的氧化硅),其介电常数在3.0左右。其二是采用旋压方法(spin-on)将有机聚合物作为绝缘材料用于集成电路工艺。这种方法兼顾了形成低极性网络和高空隙密度两大特点,因而其介电常数可以降到2.6以下。但致命缺点是机械强度差,热稳定性也有待提高。

当低k材料中的一部分原子被孔隙所替代时,很自然的,其k值继续下降。通常来说,介电材料的孔隙率越高,k值越低。介电材料中增加的孔隙率对材料的热-机械性能会带来不利的影响。此外,随着孔隙率的增加,材料的弹性模量和导热系数的退化速度(幂指数规律)比其材料密度和 k值的降低速度要快,后两者是以线性规律下降的。这种不利影响能被随后的修复(cure)技术所补偿,包括热处理、紫外线照射和电子束照射等方法,去除致孔剂,并同时破坏低k膜材料中 Si-OH及Si-H键,形成Si-O键网络,大角度的Si-O-Si键向更加稳定的小角或者“网络”结构转变,同时交联程度也得到提高,从而能使机械强度得到提高。

到65nm 技术节点以下则采用低k 材料(k≤3.2),到超低介电常数材料(ULK,k≤2.5),乃至到空气隙(air gap)架构(k≤2.0)。同传统的氧化硅薄膜相比,低k薄膜在机械强度、热稳定性和与其他工艺衔接等方面有很多问题,给工艺技术带来了很大挑战。

-

集成电路

+关注

关注

5464文章

12681浏览量

375677 -

CMOS

+关注

关注

58文章

6232浏览量

243388 -

工艺

+关注

关注

4文章

720浏览量

30390

原文标题:互连层 RC延迟的降低

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

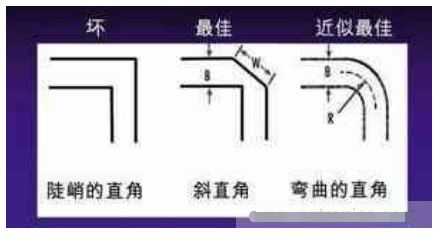

[原创]PCB互连设计过程中最大程度降低RF效应的基本方法

[原创]PCB互连设计过程中最大程度降低RF效应的基本方法

降低RF效应的重要方法

降低PCB互连设计RF效应的技巧和方法

PCB互连设计过程中最大程度降低RF效应的基本方法

如何降低PCB互连设计RF效应?

互连线RC模型应用条件的仿真研究

集成电路互连延迟问题的研究及对策

降低PCB互连设计RF效应小技巧分享

有哪些方法可以降低分布式光伏集群通信网络中的延迟?

互连层RC延迟的降低方法

互连层RC延迟的降低方法

评论