文章来源:半导体与物理

原文作者:jjfly686

本文介绍了先进集成电路制造多重曝光中的套刻精度要求。

在半导体工厂的洁净室里,光刻机如同一位在纳米画布上作画的艺术家。但当这位“画家”的笔触精细到20纳米以下时,它的双手开始颤抖——不是源于技艺不足,而是物理定律的桎梏。

为了突破这一限制,工程师们发明了多重曝光技术,却意外打开了潘多拉魔盒:对准复杂度(Overlay Complexity)的指数级暴增。这场纳米级的叠影战争,正在重塑芯片制造的底层逻辑。

一、光刻机的“视力衰退”与拆解艺术

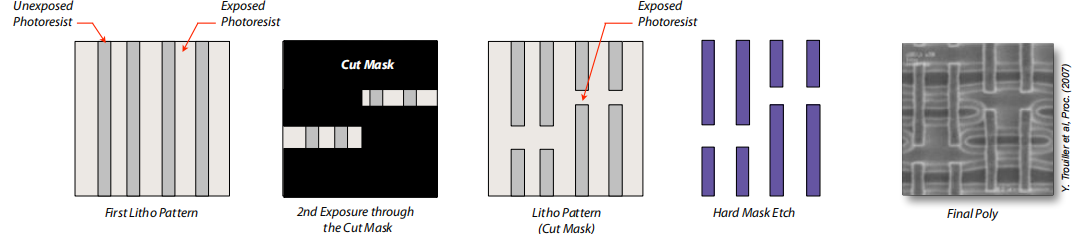

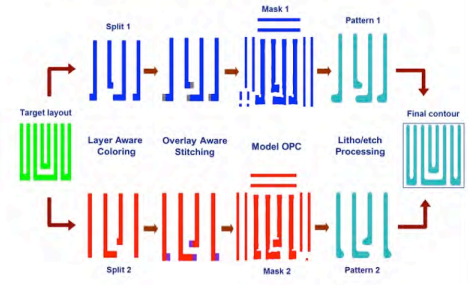

当芯片制程进入20纳米节点(相当于人类头发直径的1/4000),193nm浸没式光刻机遭遇物理极限——其光学系统如同近视加深的双眼,无法分辨间距小于80纳米的密集电路。为此,工程师将一张电路设计图拆解为多张“分镜稿”:

双重曝光:将金属层分解为红蓝两版,如同把乐高模型拆成两套组件。

三重曝光:在10nm节点,甚至需要将图形拆分为三套独立掩模

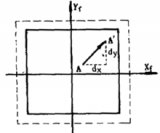

但拆解后的图案需要完美拼接,这要求每次曝光后的硅片位置必须精准对齐,误差需控制在3纳米以内。

二、对准步骤的“多米诺骨牌效应”

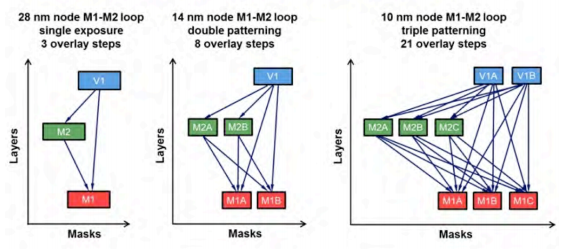

以芯片中最基础的金属-通孔(Metal-Via)连接结构为例:

28nm节点(单次曝光):只需3次对准操作,如同拼装三块标准积木。

14nm节点(双重曝光):对准步骤激增至8次,相当于用八根不同颜色的线穿同一枚针眼。

10nm节点(三重曝光):需要21次对准,复杂度堪比用21把钥匙同时开启一把锁

更惊人的是,若10nm节点采用四重曝光,对准操作将达40次。

纳米叠影的“蝴蝶效应”

对准误差带来的不仅是时间成本,更会引发更多的问题:

短路危机:金属层间5纳米的错位,可能导致相邻电路导通。

电阻增大:通孔偏移,接触电阻可能飙升。

良率降低:在7nm节点,10%的对准失误会直接导致整片晶圆报废。

-

集成电路

+关注

关注

5464文章

12688浏览量

375744 -

半导体

+关注

关注

339文章

31248浏览量

266607 -

芯片制造

+关注

关注

11文章

735浏览量

30532

原文标题:芯片制造多重曝光中的套刻精度要求

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

《大话芯片制造》阅读体会分享_1

数字曝光打印技术

相机成像不产生拖影的曝光时间计算

直接成像数字曝光技术介绍

KLA公司正式推出了Archer 750套刻量测系统

编码器刻线数与精度数的关系

MEMS制造领域中光刻Overlay的概念

芯片制造多重曝光中的套刻精度要求

芯片制造多重曝光中的套刻精度要求

评论