概述

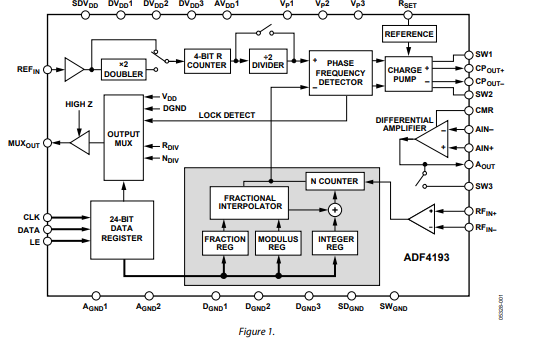

ADF4193频率合成器可以用来在无线接收机和发射机的上变频和下变频部分实现本振,其结构经过特别设计,符合基站的GSM/EDGE锁定时间要求。它由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。还有一个差分放大器,用来将电荷泵的差分输出转换为外部电压控制振荡器(VCO)的单端电压。

Σ-Δ型小数插值器与N分频器一起使用,能够实现可编程模数小数N分频。此外,4位参考(R)分频器和片内倍频器允许PFD输入端的参考信号(REFIN)频率为可选值。如果频率合成器与外部环路滤波器和VCO一起使用,则可以实现完整的锁相环(PLL)。开关结构确保PLL能在GSM时隙保护期间内建立,而无需第二PLL及相关的隔离开关。与以前的乒乓式GSM PLL结构相比,这种结构能节省成本,降低复杂度,减小PCB面积,并减少屏蔽和特性测试工作。

数据表:*附件:ADF4193低相位噪声、快速建立PLL频率合成器技术手册.pdf

应用

- GSM/EDGE基站

- PHS基站

- 仪器仪表和测试设备

特性

- 新型快速建立小数N分频PLL结构

- 单个PLL可取代乒乓式频率合成器

- 在5 µs内完成整个GSM频段上的跳频,相位建立时间为20 µs

- 相位误差:0.5°均方根值(2 GHz RF输出)

- 数字可编程输出相位

- RF输入范围最高可达3.5 GHz

- 三线式串行接口

- 片内低噪声差分放大器

- 相位噪声品质因数:–216 dBc/Hz

- 利用ADIsimPLL可实现环路滤波器设计

- 通过汽车应用认证

框图

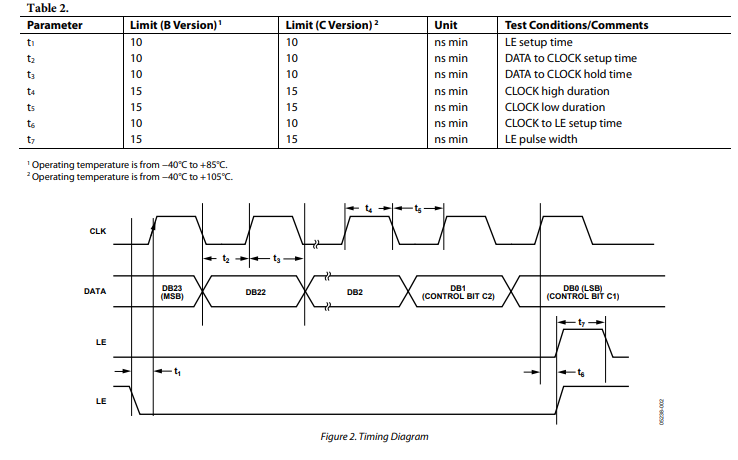

时序特征

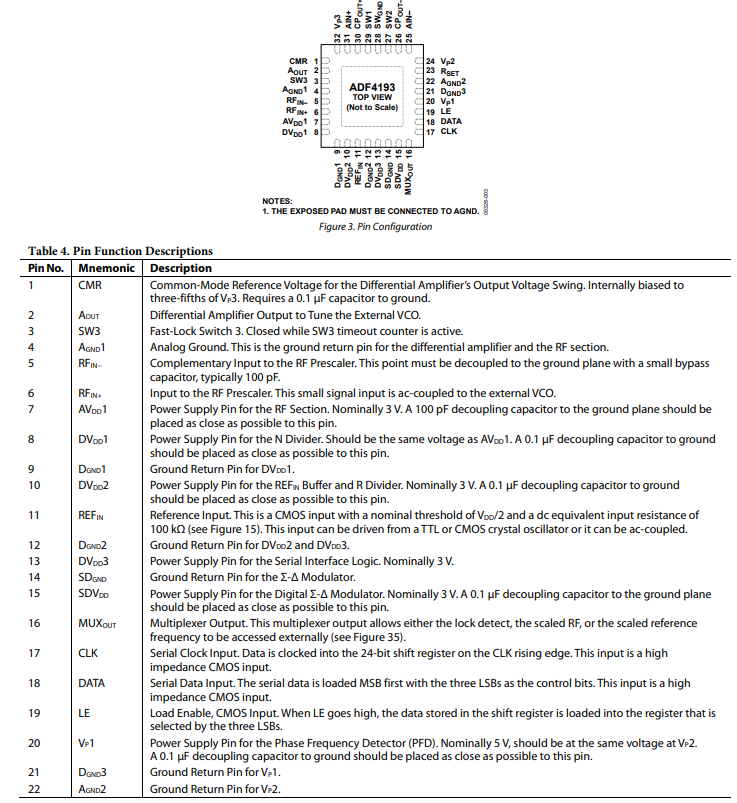

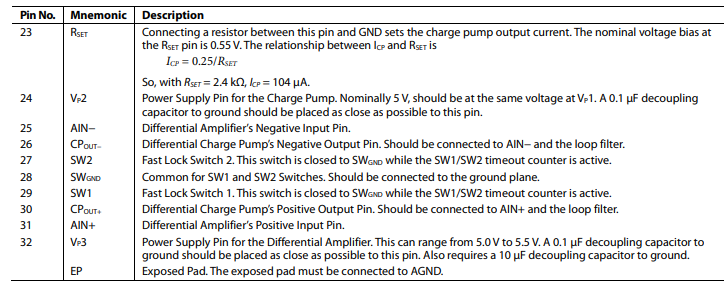

引脚配置描述

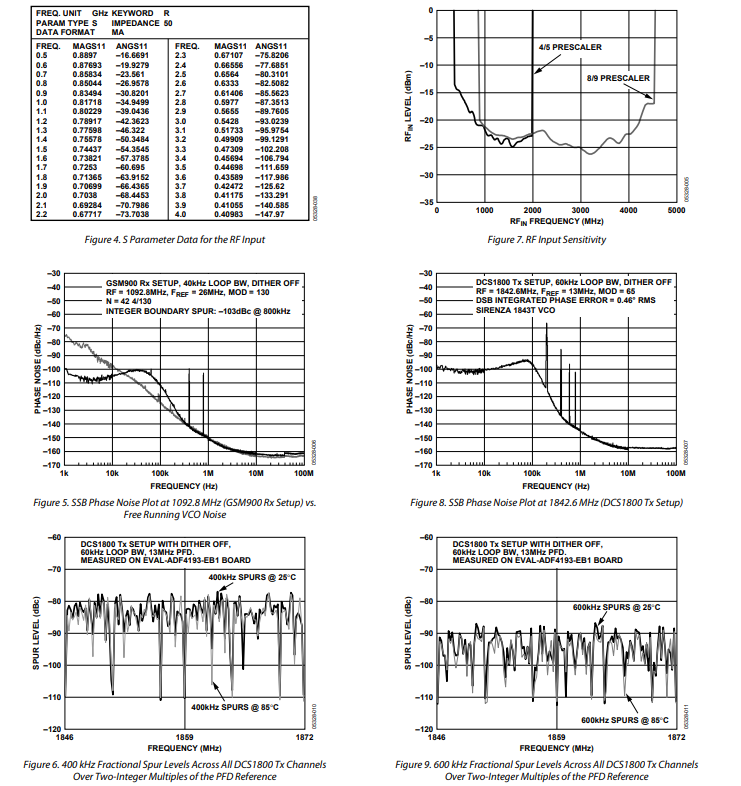

典型性能特征

ADF4193专为满足GSM基站要求而设计,尤其适用于评估乒乓解决方案。它在快速锁定时,能在频率切换和窄环带宽期间实现宽环路带宽,进而实现频率锁定。通过增加电荷泵电流来实现稳幅。电路中设有开关,用于切换环路滤波器组件值,以此在宽环路带宽时确保相位噪声和杂散符合要求。采用差分电荷泵和环路滤波器拓扑结构,有助于确保快速锁定时间,且在环路恢复到窄带宽正常工作模式时,仍能维持环路带宽。

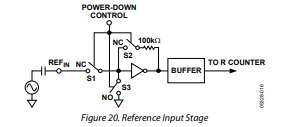

参考输入部分

参考输入级如图20所示。开关S1和S2通常处于闭合状态,S3通常处于断开状态。在掉电模式下,S3闭合,S1和S2断开,以确保参考引脚((REF_{IN}))无负载。(REF_{IN})的下降沿是正沿触发鉴频鉴相器(PFD)的有效边沿。

R计数器和倍频器

4位R计数器可对输入参考频率进行分频,以产生送往鉴频鉴相器(PFD)的参考时钟。可选择性地在R计数器后插入一个可翻转的双频器。使用此选项时,PFD参考频率会有50%的占空比,该比率可进一步除以2。利用此可编程选项,可在(REF_{IN})和PFD之间实现0.5到30的分频比。产生的参考时钟下降沿是PFD中的有效边沿,上升沿则在PFD中被禁用。建议对所有偶数R分频值启用此可翻转双频器功能,不过仅当(REF_{IN})频率大于120 MHz时才需启用。

此外,还可选择在R计数器前设置一个4位低通(REF_{IN})分频器,最高可处理20 MHz的频率。通过这些可编程选项,可实现不同的参考分频比,满足多种需求。

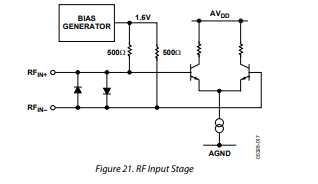

射频输入部分

射频输入级如图21所示。其后接一个两级限幅放大器,以生成预分频器所需的电流模式逻辑(CML)时钟电平。预分频器有两种选择,分别是4/5和8/9。当N分频器值大于80时,选择8/9预分频器。

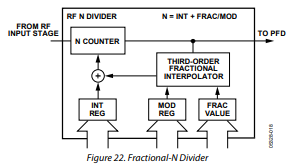

射频N分频器

射频N分频器可在锁相环(PLL)反馈回路中实现分数分频比。分频中的整数部分和分数部分通过编程设置,具体方式见图22及“整数(INT)、分数(FRAC)与模数(MOD)的关系”部分说明。整数分频比范围为26至255 ,同时采用三阶Σ - Δ调制器对分数值进行插值处理。

整数(INT)、分数(FRAC)与模数(MOD)的关系

INT、FRAC和MOD的值可通过串行接口进行编程设置,它们相互配合,能够生成间隔为鉴频鉴相器(PFD)分数间隔的射频输出频率。射频压控振荡器(RF VCO)频率公式如下:

[ RF_{OUT} = F_{PD}×[INT + (FRAC/MOD)] ]

其中:

- (RF_{OUT})是外部压控振荡器(VCO)的输出频率。

- (F_{PD})是鉴频鉴相器频率。

-

频率合成器

+关注

关注

5文章

368浏览量

33882 -

变频

+关注

关注

2文章

471浏览量

35380 -

ADF4193

+关注

关注

0文章

5浏览量

5661

发布评论请先 登录

ADI发布相位噪声性能的PLL频率合成器ADF4153A

ADF4350低相噪频率合成器在射频无线通信设备中的

ADF4193 低相位噪声、快速建立PLL频率合成器

ADF4193低相位噪声、快速建立PLL频率合成器技术手册

ADF4193低相位噪声、快速建立PLL频率合成器技术手册

评论