概述

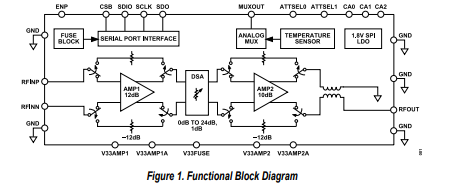

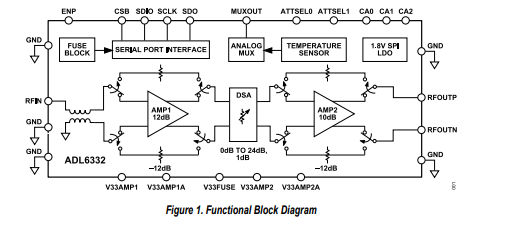

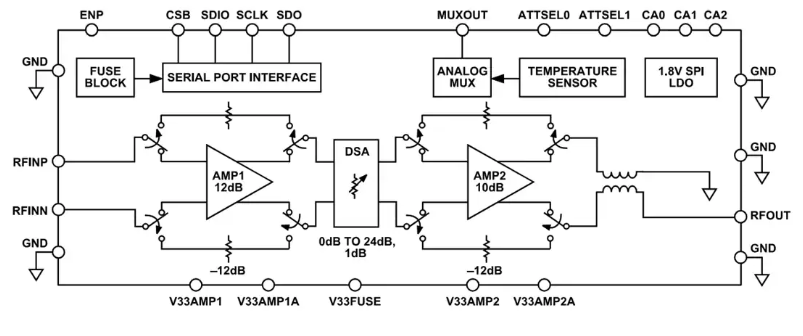

ADL6331 发射可变增益放大器(TxVGA)提供从 RF 数模转换器(RF DAC)到单端功率放大器(PA)信号链的接口。每个 ADL6331 IC 均由一个平衡-不平衡转换器、两个带旁路衰减器的差分 RF 放大器和一个数字步进衰减器(DSA)组成,以在 24 端子、4.0 mm x 4.0 mm LGA 封装中提供合适的发射器性能。

串行端口接口(SPI)控制可用于配置 RF 信号路径或优化电源电流与性能。

集成式 RF 巴伦用于提供 0.38 GHz 至 8.0 GHz(ADL6331-A)或 1.0 GHz 至 12.0 GHz(ADL6331-B)范围内的单端输出,且具有良好的阻抗匹配。

数据表:*附件:ADL6331 0.38GHz至12GHz TxVGA技术手册.pdf

应用

特性

- 宽带 TxVGA 将 RF-DAC 与波束合成和 PA 连接

- 工作频率范围:0.38 GHz 至 12 GHz,2 种产品型号

- ADL6331-A:0.38 GHz 至 8 GHz

- ADL6331-B:1.0 GHz 至 12 GHz

- 优化 RF-DAC 的共模抑制、偶次谐波和互调

- 50 Ω 差分输入和 50 Ω 单端输出

- 集成宽带射频输出平衡器

- 增益控制范围为 70 dB,步长为 1 dB

- RF DSA 范围:24.0 dB,步长为 1.0 dB

- 每个放大器旁路损耗为 12 dB

- 多个预定义衰减值和旁路放大器级之间的异步切换。

- 4 GHz 时的功率增益:15.1 dB (ADL6331-A), 15.4 dB (ADL6331-B)

- 4 GHz 时的噪声指数:7.5 dB (ADL6331-A), 7.5 dB (ADL6331-B)

- 4GHz 时的 OIP3:31.0 dBm (ADL6331-A),31.0 dBm(ADL6331-B)

- 4GHz 时的 OIP2:58 dBm (ADL6331-A), 56 dBm (ADL6331-B)

- 4GHz 时的 OP1dB:12.4 dBm (ADL6331-A), 12.0 dBm (ADL6331-B)

- 通过 3/4 线 SPI 完全可编程

- 3.3 V(单电源)

- 24 引脚、4.0 mm x 4.0 mm LGA

逻辑图

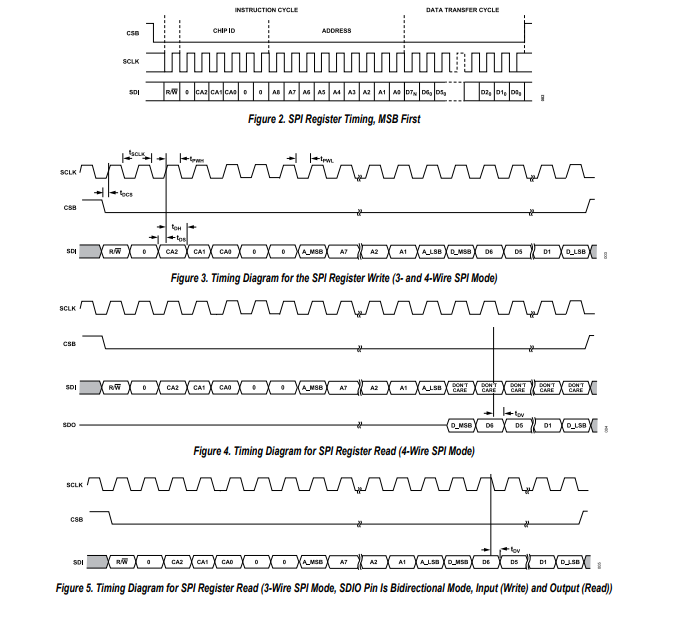

SPI时序图

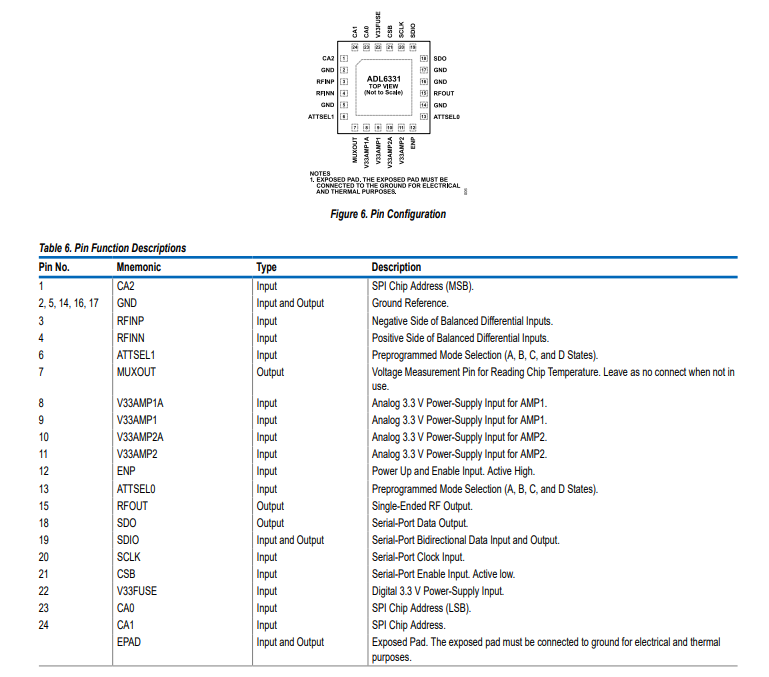

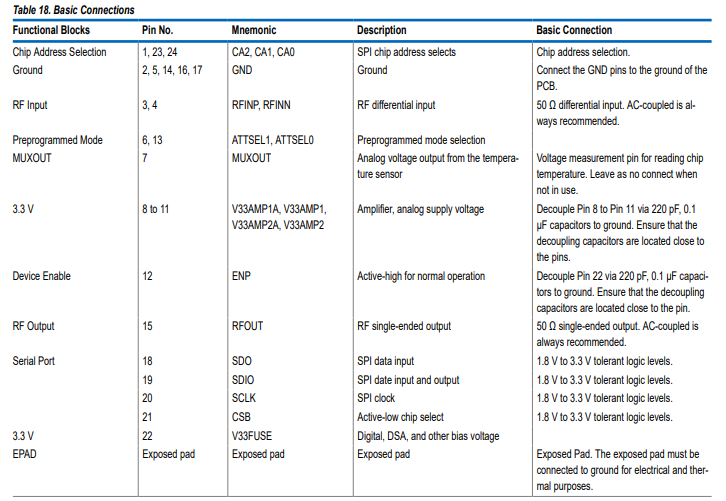

引脚配置描述

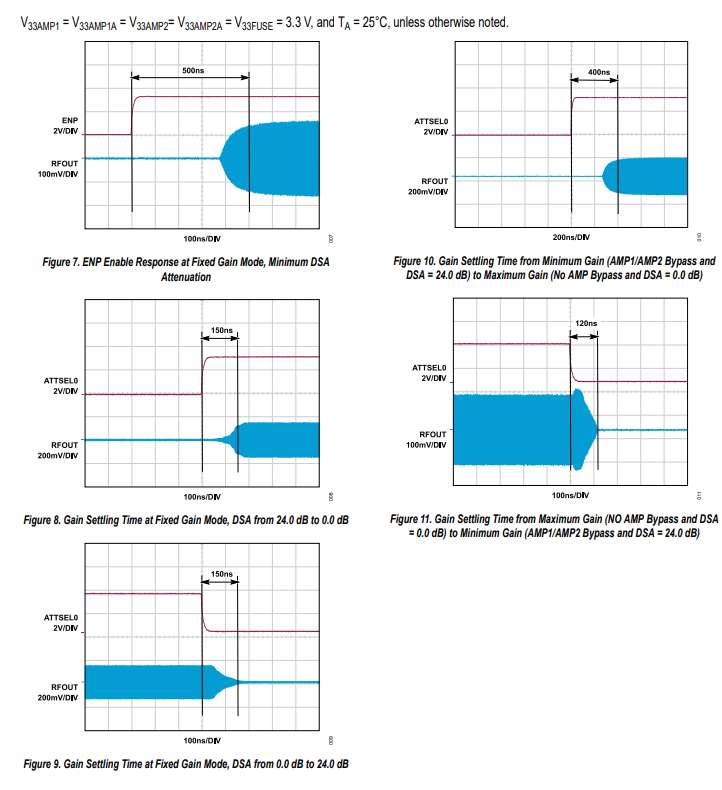

典型性能特征

串行端口接口(SPI)

ADL6331的SPI允许用户通过三线或四线SPI模式为特定功能或操作配置设备。该串行端口接口由四条控制线路组成:SCLK、SDIO、SDO和CSB。对于四线SPI模式,SCLK、SDIO和SDO被使用;三线SPI模式则是SPI模式的默认状态。要启用四线SPI模式,必须将SDOACTIVE[3]和SDOACTIVE[4]在寄存器0x000中设置为1。SPI中的定时要求列于表3中。

ADL6331协议由一个读/写操作、四个芯片地址位(最高有效位始终为0 )、九个寄存器地址位以及八个数据位组成。地址和数据字节均先传输最高有效位,最后传输最低有效位。为正确寻址设备,芯片地址前缀位必须与外部配置的芯片地址引脚CA2、CA1和CA0匹配。

ADL6331写入SPI的输入逻辑电平为1.8 V或3.3 V。在回读周期中,通过设置SPI_3P3_CTRL位(寄存器0x121,位4 ),SDO可配置为1.8 V(默认 )或3.3 V回读输出电平。

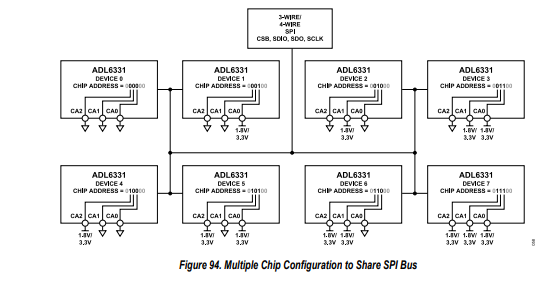

配置多个芯片共享SPI总线

最多可以使用同一条三线或四线SPI总线,通过单个CSB引脚寻址八个ADL6331设备。对于此功能,ADL6331的芯片选择引脚(CA2、CA1和CA0 )用于标识带有SPI写芯片地址前缀的芯片(SPI接口端口如图2所示 )。

ADL6331协议会忽略芯片地址最高有效位与芯片地址引脚设置不相等的地址写入,只有当芯片地址前缀位的高四位与芯片地址引脚设置相等时,芯片才会接受地址。唯一的例外是软件复位地址0x000。共享总线上的所有ADL6331芯片都会接受来自SPI主机控制器的0x000寄存器软件复位。

图94展示了如何配置芯片地址引脚CA2、CA1和CA0以及相关的芯片地址前缀位。

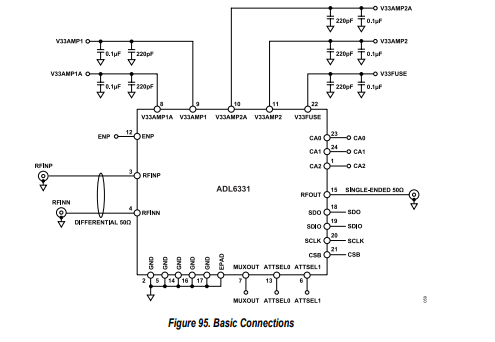

基本连接

应用信息

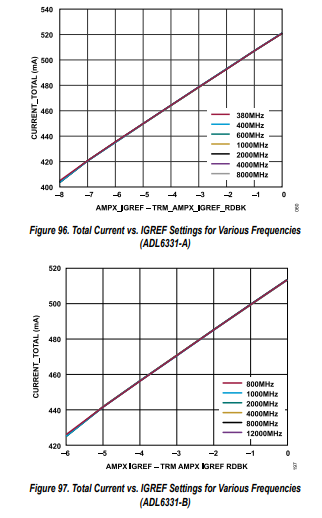

电流消耗优化

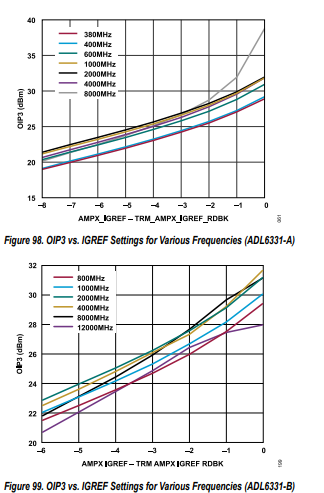

当寄存器0x104、寄存器0x105和寄存器0x106(适用于AMP1 )以及寄存器0x111、寄存器0x112和寄存器0x113(适用于AMP2 )中的最高有效位(MSB)都设置为0时,这六个寄存器可供用户使用。如果需要降低电流消耗,可根据需要设置AMP1的IGREF(在寄存器0x104中 )和AMP2的IGREF(在寄存器0x111中 )。工厂调校的IGREF(分别在寄存器0x140和寄存器0x143中,适用于AMP1和AMP2 )可实现最佳的OIP3性能,如图98和图99所示。

不建议将IGREF设置增加到高于AMP1和AMP2的回读值,这样做可能会影响器件的长期可靠性。

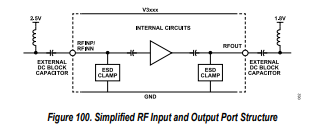

交流耦合

静电放电(ESD)钳位电路紧邻输入端口和输出端口(见图100 )。当施加的直流电压大于或等于1.0 V(这是常见情况 )时,存在硅控制整流器(SCR)触发的风险,即使是单个直流电压尖峰也可能导致SCR触发。带有直流偏置的部件始终建议使用隔直电容进行交流耦合。

-

RF

+关注

关注

66文章

3197浏览量

171076 -

数模转换器

+关注

关注

14文章

1275浏览量

85205 -

可变增益放大器

+关注

关注

1文章

41浏览量

46248

发布评论请先 登录

LMX2595在8GH,12GHz, 24GHz都会产生杂散,为什么?

电源技巧#8:设计12GHz,超低相位噪声(0.09 ps rms抖动)锁相环

安捷伦1169A 12GHz探头放大器套件特性参数

ADL6331:0.38千赫至12千赫TxVGA初步数据表 ADI

ADL6332:0.38千兆赫至12千兆赫RxVGA初步数据表 ADI

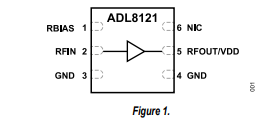

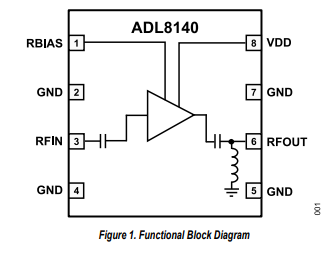

ADL8121 GaAs、pHEMT、MMIC、低噪声放大器,0.025GHz至12GHz技术手册

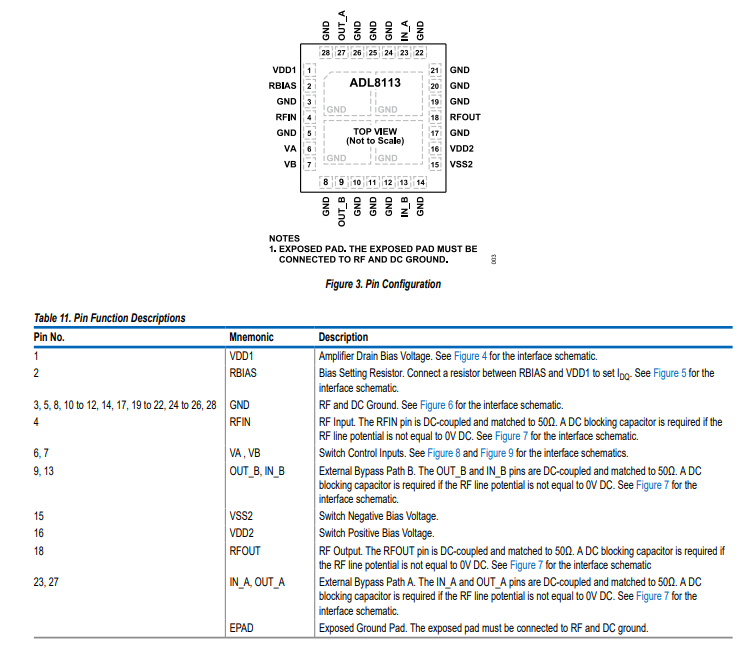

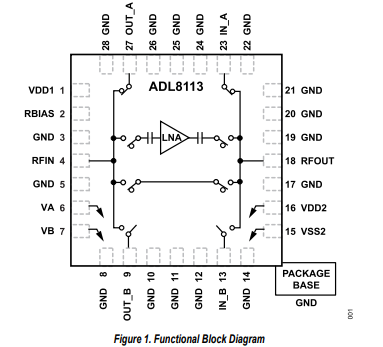

ADL8113 10MHz至12GHz低噪声放大器,带10MHz至14GHz旁路开关技术手册

ADL6332 0.38GHz至15GHz RxVGA技术手册

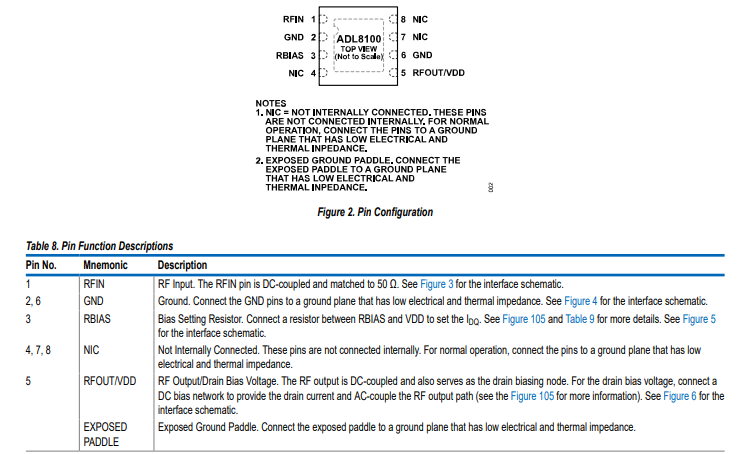

ADL8100 GaAs、pHEMT、MMIC、低噪声放大器,0.01 GHz至20 GHz技术手册

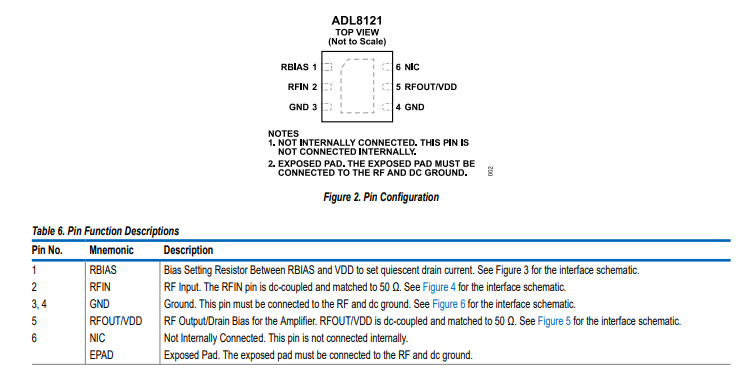

ADL8121 GaAs、pHEMT、MMIC、低噪声放大器,0.025 GHz至12 GHz技术手册

ADL8113 10MHz至12GHz低噪声放大器,带有10MHz至 14GHz旁路开关技术手册

Analog Devices Inc. ADL6331发射可变增益放大器 (TxVGA)数据手册

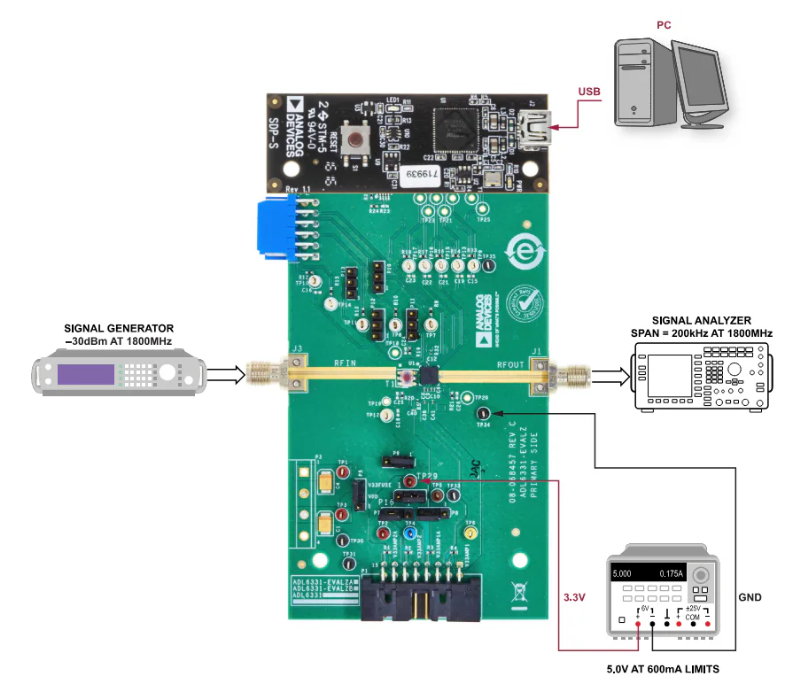

Analog Devices Inc. ADL6331-EVALZA 评估板数据手册

ADL6331 0.38GHz至12GHz TxVGA技术手册

ADL6331 0.38GHz至12GHz TxVGA技术手册

评论