概述

AD9551接受一个或两个参考输入信号,然后由这些信号产生一个或两个输出信号。这两个输出信号的频率为谐波相关的,可编程因子为1至63。AD9551能将参考频率转换成需要的输出频率。输入接收器和输出驱动器同时具备单端和差分工作模式。

数据表:*附件:AD9551多业务时钟发生器技术手册.pdf

参考调节和转换电路在内部使两个参考同步,以便一个参考失效时,输出端实际上不出现相位扰动现象。

AD9551采用一个26 MHz外部晶体(标称值)和内部DCXO来提供保持模式工作。如果两个参考都失效了,该器件会维持一个稳定的输出信号。

小数N分频PLL可实现超精细的输出频率调谐精度。所有目前定义的网络标准(包括前向纠错率)都可能实现(假设采用一个26 MHz的晶体)。

AD9551具备引脚可选的预置分频器值,从而提供频比分类。由于具备对大多数所需频比进行编程的能力,因此SPI接口拥有更多灵活性。

应用

特性

- 任意两个标准网络速率之间转换

- 双路参考输入和双路时钟输出

- 引脚可编程(标准网络速率转换)

- SPI可编程(任意合理速率转换)

- 输出频率范围:10 MHz至777.6 MHz

- 输入频率范围:19.44 MHz至806 MHz

- 片上VCO

- 欲了解更多特性,请参考数据手册

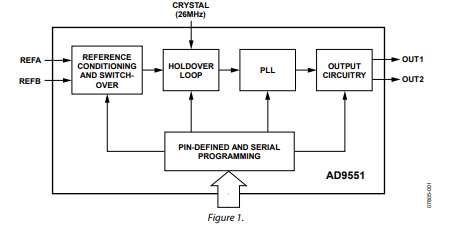

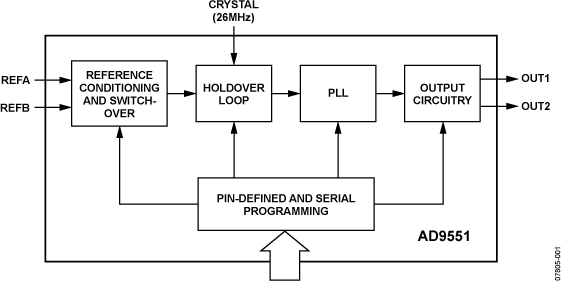

框图

AD9551可通过外部控制引脚(A[3:0]、B[3:0]和Y[3:0])轻松配置。这些引脚的逻辑状态设置预定义的分频器值,以建立特定的输入 - 输出频率比。对于需要不同频率比的应用,用户可通过串行端口覆盖任何预配置的设置,从而启用各种广泛的应用。

AD9551架构由两个级联的PLL级组成。第一级由分数分频(通过Σ - Δ调制)组成,随后是一个基于晶体谐振器的DCXO数字PLL。DCXO使用外部晶体,频率范围为19.44 MHz至52 MHz。DCXO构成第一个PLL,在较窄的频率范围(±50 ppm)内围绕晶体谐振器频率工作。这个PLL的环路带宽约为180 Hz,提供初始的抖动净化输入参考信号。第二级是一个频率乘法PLL,将19.44 MHz至52 MHz的输入频率(在104 MHz的范围内)转换为约3.7 GHz。这个PLL采用基于Σ - Δ调制的分数反馈分频器,实现分数频率乘法。第二个PLL输出端的可编程整数分频器将最终输出频率设置为高达900 MHz。

理解AD9551的一个重要方面是,其产生的输出频率很可能与输入参考频率不一致。原因是输入和晶体频率通常不是谐波相关的,因此输出和晶体频率之间没有固定关系。因此,输入和输出信号之间的相位关系一般是不断变化的。

AD9551包含参考信号处理模块,可在两个参考输入之间实现平滑的切换过渡。该电路会自动检测参考输入信号的存在。如果只有一个输入存在,器件将其用作有效参考。如果两个输入都存在,一个将成为有效参考,另一个将成为备用参考。该电路与备用参考的有效参考边缘对齐。如果有效参考失效,电路会自动切换到备用参考(如果可用),使其成为新的有效参考。同时,失效的参考一旦再次可用,将成为新的备用参考,并与新的有效参考边缘对齐(防止故障再次发生的预防措施)。

如果无法使用备用参考,AD9551支持保持模式。请注意,外部晶体对于切换器和保持功能至关重要。它也是参考同步和监测功能的时钟源。

AD9551使用单个外部电容作为输出PLL环路滤波器。凭借适当的端接,输出可兼容LVPECL、LVDS或CMOS逻辑电平,尽管AD9551是严格在CMOS工艺中实现的。

AD9551可在 -40°C至 +85°C的扩展工业温度范围内运行。

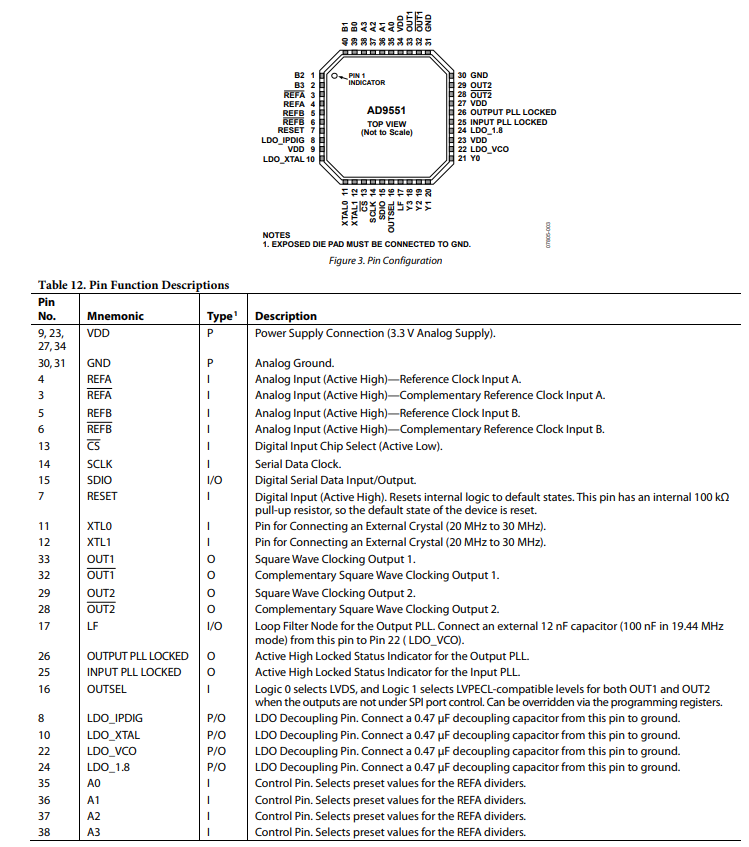

引脚配置描述

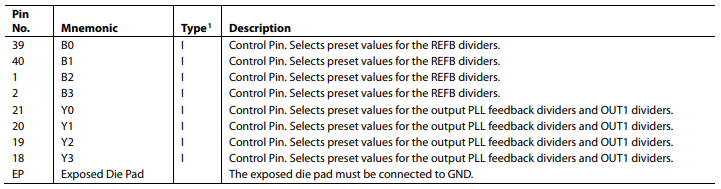

典型性能特征

-

接收器

+关注

关注

15文章

2651浏览量

77531 -

pll

+关注

关注

6文章

990浏览量

138377 -

时钟发生器

+关注

关注

1文章

358浏览量

70163

发布评论请先 登录

AD9551,pdf datasheet (Multiser

AD9551 多业务时钟发生器

AD9551多业务时钟发生器技术手册

AD9551多业务时钟发生器技术手册

评论