串行外围设备接口(Serial Peripheral Interface,SPI)是由 Motorola 公司开发的,用来在微控制器和外围设备芯片之间提供一个低成本、易使用的接口(SPI 有时候也被称为4线接口)。这种接口可以用来连接存储器、AD/DA转换器、实时时钟日历、LCD驱动器、传感器、音频芯片,甚至其他处理器。目前支持 SPI 的元件很多,并且还在不断增加。

这里需要提一下,由于专利在电子行业是很关键的,因此部分厂商可能会将 SPI 通讯协议更名以规避高昂的专利费,但其硬件处理方式是一样的,只是换了一个名称而已(或者在协议上做了一些修改),例如 TI 的 SSI(Synchronous Serial Interface)通讯协议。与标准的串行端口不同,SPI 是一个同步协议接口,所有的传输都参照一个共同的时钟,这个同步时钟信号由主机(处理器)产生。接收数据的设备(从设备)使用时钟对串行比特流的接收进行同步化。可能会有许多芯片连到主机的同一个 SPI 接口上,这是主机通过触发从设备的芯片的片选输入引脚来选择接收数据的从设备,没有被选中的外设将不会参与 SPI 传输。SPI 主要使用4个信号:主机输出/从机输入(MOSI)、主机输入/从机输出(MISO)、串行时钟(SCLK或SCK)和外设片选(nCS)。有些处理器有 SPI 接口专用的片选,称为从机选择(nSS)。MOSI 信号由主机产生,从机接收。在有些芯片上,MOSI 只被简单地标为串行输入(SI),或者串行数据输入(SDI)。MISO 信号由从机产生,不过还是在主机的控制下产生的。在一些芯片上,MISO 有时被称为串行输出(SO),或者串行数据输出(SDO)。外设片选信号通常只是由主机的备用 I/O 引脚产生。SPI 接口在内部硬件实际上是两个简单的移位寄存器,在主器件的移位脉冲下,数据按位传输,高位在前,低位在后,为全双工通信,数据传输速度总体来说比 I2C 总线要快,速度可达到 Mbps 级别。

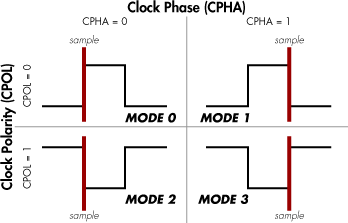

根据时钟极性和时钟相位的不同,SPI 有四个工作模式。时钟极性有高、低两极:

1、时钟低电平时,空闲时时钟(SCK)处于低电平,传输时跳转到高电平;2、时钟极性为高电平时,空闲时时钟处于高电平,传输时跳转到低电平。

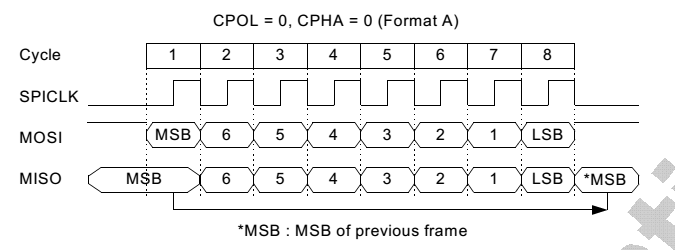

时钟相位有两个:相位0 和 相位1。对于时钟相位0,如果时钟极性是低电平,MOSI 和 MISO 输出在时钟(SCK)的上升沿有效(如图1所示)。

图1. 时钟极性为低电平且时钟相位0时的SPI时序图

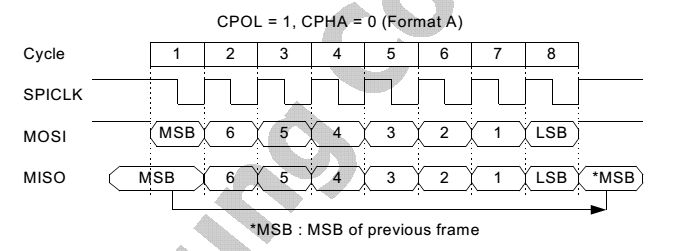

如果时钟极性为高电平,对于时钟相位0,这些输出在 SCK 的下降沿有效(如图2所示)。

图2. 时钟极性为高电平且时钟相位0时的SPI时序图

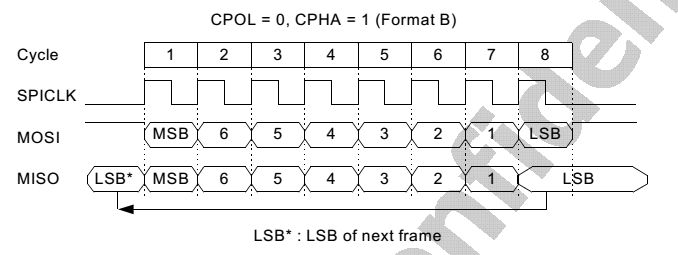

对于时钟相位1,情况则相反。此时如果时钟极性是低电平,MOSI 和 MISO 输出在时钟(SCK)的下降沿有效(如图3所示)。

图3. 时钟极性为低电平且时钟相位1时的SPI时序图

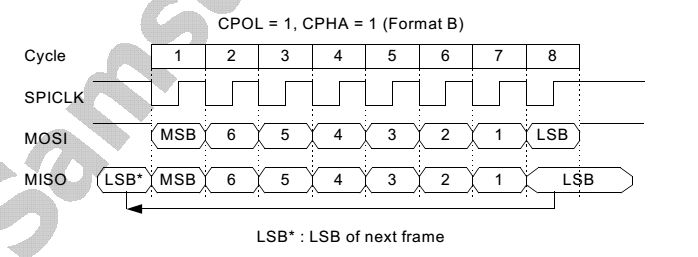

如果时钟极性是高电平,这些输出在 SCK 的上升沿有效(如图4所示)。

图4. 时钟极性为高电平且时钟相位1时的SPI时序图

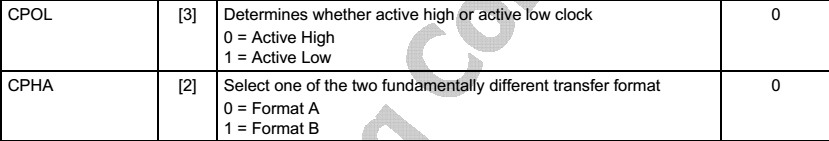

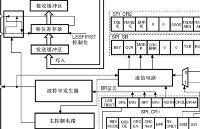

工程中一般会用 CPOL 代表时钟极性,用 CPHA 代表时钟相位,在 S5PV210 的 datasheet 中,我们可以看到相应的 SPI 接口配置寄存器(如图5所示)。

图5. S5PV210的SPI配置寄存器CH_CFGn

也就是由两个位(CPOL 和 CPHA)共同决定 SPI 的工作模式,所以有 2 * 2 = 4 种工作模式。其中,时钟极性(CPOL)决定的是时钟空闲时电平的高低状态(0:空闲时低电平,1:空闲时高电平);时钟相位(CPHA)决定的是数据在时钟的上升沿或下降沿锁存/采样(0:第一个边沿开始,1:第二个边沿开始)。

最后,SPI 接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。

-

驱动器

+关注

关注

54文章

9111浏览量

156441 -

寄存器

+关注

关注

31文章

5618浏览量

130389 -

时钟

+关注

关注

11文章

1999浏览量

135225 -

SPI

+关注

关注

17文章

1898浏览量

102093

原文标题:浅谈串行外围设备接口(Serial Peripheral Interface)SPI总线

文章出处:【微信号:gh_c472c2199c88,微信公众号:嵌入式微处理器】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CDC2516:高性能锁相环时钟驱动器的深度解析

迅通科技模块PTR7002的SPI时钟能跑多高

LMK02002精密时钟调节器技术文档摘要

CDC3S04 四通道正弦波时钟缓冲器技术文档总结

当波特率设置为高时,SPI 时钟延长,数据丢失问题怎么解决?

FPGA时序约束之设置时钟组

根据时钟极性和时钟相位的不同,SPI有四个工作模式

根据时钟极性和时钟相位的不同,SPI有四个工作模式

评论