高速先生成员--周伟

今年开始其实我们已经围绕100G的高速信号仿真写了多篇文章啦,2025年高速先生第一篇文章就是和这个相关:当DEEPSEEK被问到:如何优化112GBPS信号过孔阻抗?文章里面也介绍了不同速率下长、短过孔阻抗的差异,以及不同板厚情况下,长、短过孔阻抗的偏差还不一样。今天我们还是从仿真的角度出发,给大家介绍一下哪些因素会影响100G以上信号,这样大家也就知道为什么说100G以上信号的仿真会比较耗时了。

首先最大的影响因素还是在过孔上,我们之前反复说过,高速信号的仿真其实大部分的时间都是在和过孔打交道,目的就是让过孔阻抗和线路的阻抗尽量匹配。但说起来简单,要实现起来就没那么容易了。

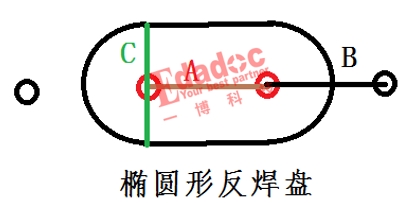

我们先来简单看下几种不同高速差分过孔的基本结构吧,常见的差分过孔结构如下图所示。

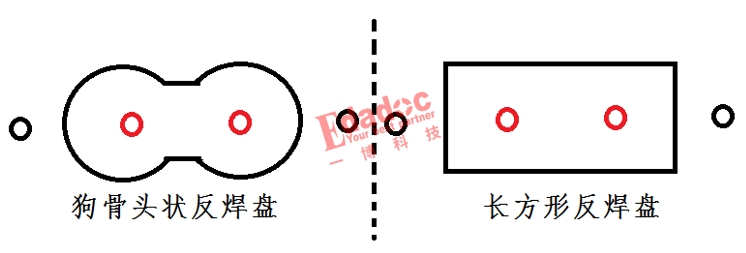

中间两个红色的孔为信号孔,两边黑色的为地孔,黑色椭圆形的圈为反焊盘,也就是圈内除了孔,所有层的铜皮都是被掏掉的,我们也叫禁布区;图中两个信号孔之间的距离为A,信号孔到旁边地孔的距离为B,反焊盘的直径为C,差分过孔的阻抗和A、B、C的数值相关,同时又和孔本身的孔径(我们又叫drill直径)及焊盘大小相关。除了和孔结构及尺寸等有关外,过孔阻抗还和板子(孔)的厚度,铜皮层数及介质材料有关,另外也和反焊盘的形状及大小有关,比如下面还有常见的狗骨头状及长方形状反焊盘结构。

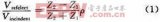

正是因为差分过孔的阻抗影响因素太多,目前还没有一个公认的差分过孔阻抗公式,所以过孔的阻抗就没法像走线那样可以通过软件来计算,设计人员很多时候就只能靠经验、设计参考书等来做,但不同的信号阻抗标准也不一样,常见的有85ohm,90ohm,100ohm等,所以最终过孔和线路阻抗是否匹配也就不得而知,这个时候SI攻城狮就顺利登场了。是的,差分过孔阻抗没法计算,但是可以通过3D仿真能模拟出来,我们把过孔对应的结构及尺寸搭配一定的材料特性,在3D仿真软件中建立起相应的模型,这样就可以算出来这个孔的无源特性,也能看到大致的阻抗情况。如果阻抗差异大,我们就会对模型进一步优化,比如根据不同的过孔距离,过孔长度等,修改不同的反焊盘形状或者尺寸,有时不同层还会有不同的要求。

以上只是常规的一些要求,懂的都懂,但到了100Gbps以上速率的信号又会有什么不一样的要求呢?主要有下面几点:

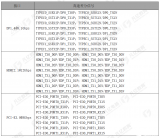

1、同样的过孔及反焊盘形状和尺寸,长孔和短孔的过孔阻抗差异较大;

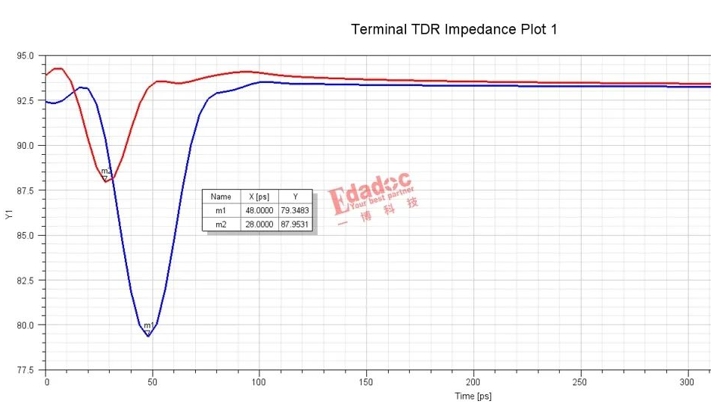

如下图为50GHz下长孔和短孔的阻抗特性。

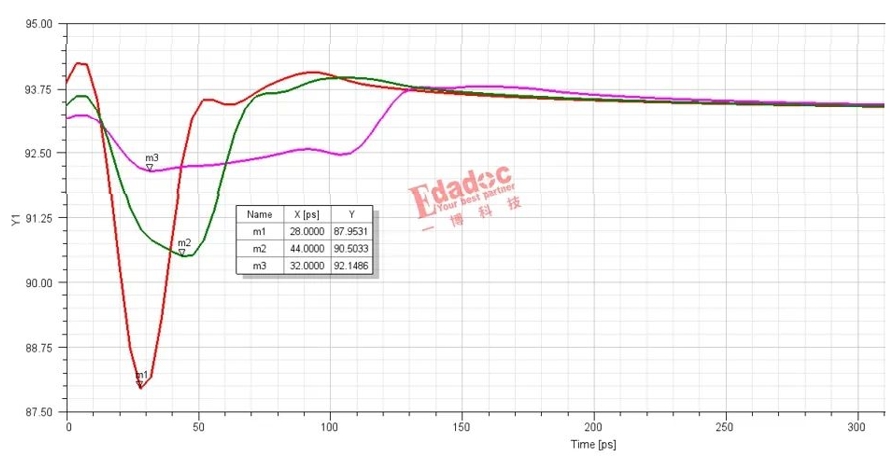

2、同一个过孔,不同频率情况下感受到的过孔阻抗也有较大的差异;如下图为同样的过孔尺寸,分别在5GHz,25GHz和50GHz带宽的情况下看到的阻抗也是不一样的,频率越高,阻抗越低。

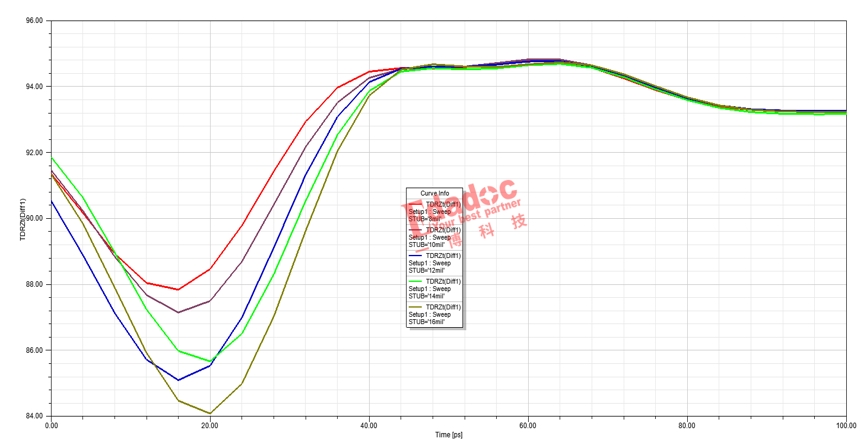

3、频率越高,过孔stub的影响越大,也就是对stub越敏感,这个时候我们就要考虑过孔最大留多长的stub能满足要求,同时也还要考虑工厂的背钻加工能力。从下图仿真结果来看,stub相差2mil过孔阻抗约相差1ohm。

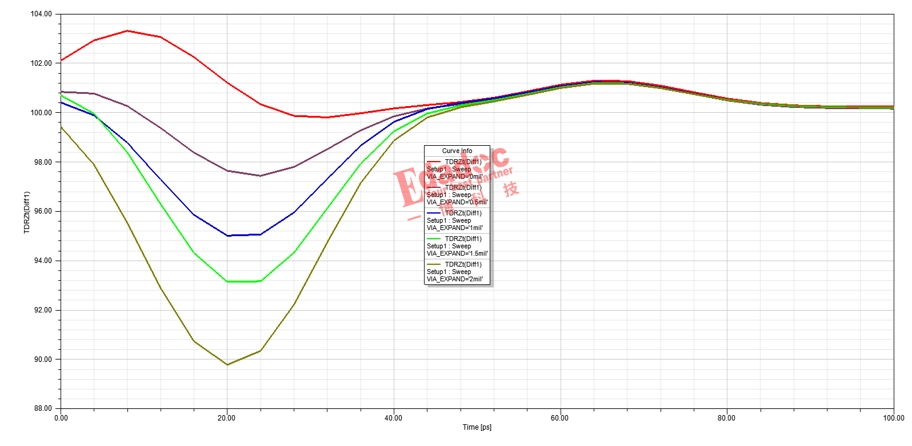

4、钻孔孔径对过孔的影响也在逐步加大,孔径越大,过孔阻抗越小。

另外还有孔间距的影响,100Gbps信号我们基本要看到50GHz的频率,在高频下这些影响因素会变得更加敏感,所以我们需要花更多的时间来调整这些参数,在25Gbps速率下,长孔和短孔用同样的尺寸参数影响不大,但到了100Gbps以上,不同层需要不同的过孔参数,这样就会多出更多的建模工作量。

除了阻抗的评估,还需要进行串扰的评估,这是因为每个芯片对于信号的排列不一样,芯片的pin间距也不一样,所以每种情况都需要单独的进行评估,我们其实在过孔排列上也有单独的文章介绍,大家可以看看下面这篇文章。距离一样时,你们知道两对过孔怎么摆串扰最小吗(链接)

关于过孔仿真的介绍,大家也可以看看前面我们写过的一些文章:

当DeepSeek被问到:如何优化112Gbps信号过孔阻抗?

总而言之就是100Gbps以上信号,由于不同的芯片/连接器等pin排列及间距不同,对于过孔的优化方式也会千差万别,另外在高频下各种影响会更敏感,频率越高,所需要计算的数据也越多,从而导致需要更多的时间来优化模型。

除了过孔影响因素,还有信号协议本身的要求也更严格了(后面有时间我们再单独说说100Gbps信号的协议),因为要看到更高频率的数据,频率越高,材料的损耗特性变得没有那么线性了,高频会加剧损耗的变化,所以对材料选型和叠层设计也是一种考验。

本期问题:除了上面说到的过孔和信号协议、材料和叠层影响,100Gbps信号还有哪些需要考虑的?

审核编辑 黄宇

-

pcb

+关注

关注

4417文章

23964浏览量

426131 -

仿真

+关注

关注

55文章

4535浏览量

138661 -

高速信号

+关注

关注

1文章

278浏览量

18526

发布评论请先 登录

100Gbps数据吞吐量?Samtec can do it!

聊聊高速PCB设计100Gbps信号的仿真

升特推出首个高频宽100Gbps Gearbox芯片组

基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真

聊聊高速PCB设计100Gbps信号的仿真

聊聊高速PCB设计100Gbps信号的仿真

评论