设计规则检查(Design Rule Check,简称DRC)是芯片设计中的一个关键步骤,旨在确保电路设计的物理布局符合制造工艺的要求。可以把它类比为建筑设计中的检查流程,确保建筑图纸中的所有尺寸和结构符合建筑标准,否则建造出来的建筑可能会有安全隐患或不符合使用要求。类似地,DRC 就是对芯片设计的物理版图进行检查,确保其符合生产厂商的工艺规则。

1、DRC的作用:

DRC 的主要作用是验证芯片版图中的各种物理设计是否符合制造过程中的工艺限制。芯片制造涉及微小的尺寸和精密的制造工艺,如果设计不符合这些规则,可能会导致芯片在生产过程中无法正确制造,甚至无法正常工作。

2、DRC的工作原理:

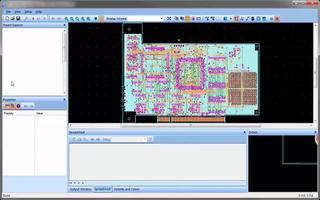

DRC 会对芯片设计中的每个物理元素(如线路、元器件、接触点等)进行检查,确保它们的尺寸、间距和布局符合以下要求:

线路宽度:芯片上的电线(连线)不能太窄,必须达到制造工艺要求的最小宽度。如果过窄,电流可能会不稳定,甚至导致电路短路。

线路间距:电路中的不同线路之间必须有足够的间距,以避免它们之间发生短路或干扰。间距过小可能导致信号干扰,影响芯片功能。

过孔和接触点:在不同层次之间需要通过过孔连接电路,过孔的尺寸和位置也必须符合规则。接触点(例如电源和地线的接触点)也必须符合最小尺寸和间距要求。

层间对齐:芯片设计有多个层,每层都要有明确的对齐规则。DRC 会检查这些层是否正确对齐,确保信号能准确通过每一层。

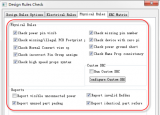

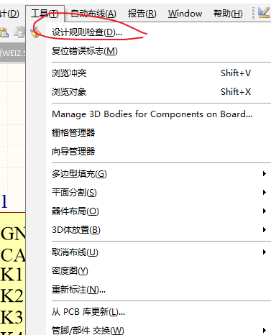

3、DRC检查的具体步骤:

规则设置:设计工程师需要根据所使用的制造工艺来设置DRC规则。例如,不同的工艺(如14nm、7nm工艺)有不同的规则。

规则应用:DRC 工具会自动将这些规则应用到芯片的版图设计中,逐一检查每个物理元素是否符合规定。

检查报告:如果版图设计存在违反规则的地方,DRC 工具会生成一个报告,指出哪些地方存在问题,并给出解决方案。这些问题可能是某条线路太细、两条线路间距太小,或者过孔的位置不正确等。

4、DRC的优化:

通过 DRC 检查,设计工程师可以发现并修复设计中的问题,确保版图能够顺利通过制造环节。这不仅能避免生产中的错误,还能提高芯片的可靠性和性能。

优化版图:设计师可以根据 DRC 提供的反馈,调整电路的布局、尺寸、间距等,使设计符合工艺规则。

减少制造失败:DRC 可以有效避免制造过程中的故障,降低返工率,节省时间和成本。

5、DRC与其他检查的关系:

除了 DRC,芯片设计中还会进行其他类型的检查,如:

LVS(Layout Versus Schematics)一致性检查:检查版图设计是否与原理图一致,确保电路功能没有错误。

STA(Static Timing Analysis)静态时序分析:分析电路中的信号传输延迟,确保时序满足要求。

后仿验证:通过仿真验证电路在实际工作中的表现。

6、DRC的重要性:

DRC 是芯片设计中的必要步骤,它可以有效地保证芯片设计的可靠性和制造可行性。通过 DRC,设计工程师能够在早期发现问题,避免由于设计错误导致的生产失败,减少生产成本,提高产品质量。没有 DRC 检查,芯片设计很可能在生产过程中出现严重问题,甚至无法完成制造。

●总结●

DRC(设计规则检查)是芯片设计中的一项重要步骤,确保设计符合制造工艺的限制,避免因不合规设计而导致生产失败。通过 DRC 工具,设计师能够自动检查版图中的尺寸、间距、过孔等是否符合要求,确保芯片的稳定性和可靠性。在现代集成电路设计中,DRC 是芯片成功制造和高效生产的关键环节之一。

直接转载来源:老虎说芯。

-

元器件

+关注

关注

113文章

5042浏览量

100299 -

芯片设计

+关注

关注

15文章

1171浏览量

56775 -

DRC

+关注

关注

2文章

157浏览量

38326

原文标题:想在芯片设计领域突围?先攻克设计规则检查(DRC)这道难关

文章出处:【微信号:gh_454737165c13,微信公众号:Torex产品资讯】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

altium designer规则检查问题

编写PCB设计规则检查器技巧

编写属于自己的PCB设计规则检查器

【硬件电路】AltiumDesigner18规则检查含义

PCB设计电气规则检查器解决DRC问题

分享PCB布线设计规则检查分析

pcb规则检查怎样检查

orcad物理规则检查的含义是什么

AD学习问题记录(二):pcb设计规则检查报错Silk To Solder Mask Clearance Constraint

芯片设计中的设计规则检查

芯片设计中的设计规则检查

评论