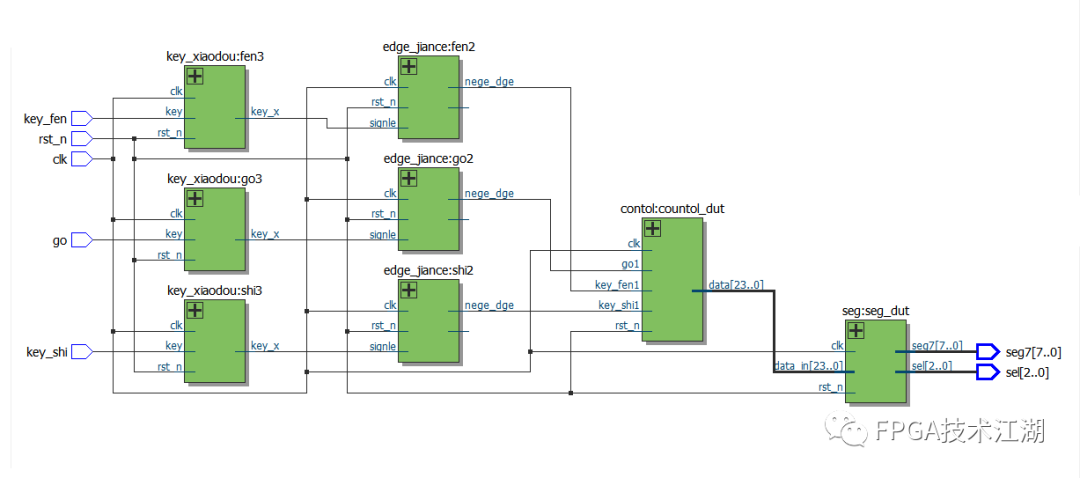

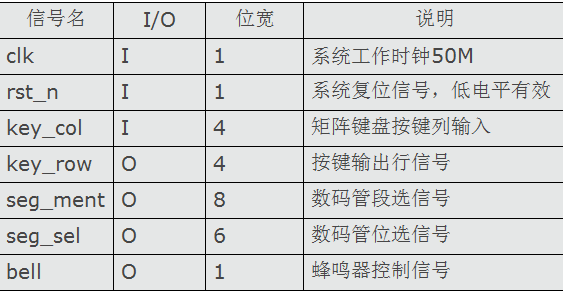

本次的设计的数字钟思路描述如下,使用3个key按键,上电后,需要先配置数字时钟的时分秒,设计一个按键来控制数字时钟的时,第二个按键来控制数字时钟的分,本次设计没有用按键控制数字时钟的秒,原理一样,大家可以自己做拓展设计再使用一个按键控制数字时钟的,然后用第三个按键来控制数字时钟的运行。采取"Top to down"设计思想,分模块设计,由于本次设计比较简单,这里就没有设计总设计框架图,上面也大致描述了设计思路,给大家截取RTL级视图提供参考,具体设计如下:

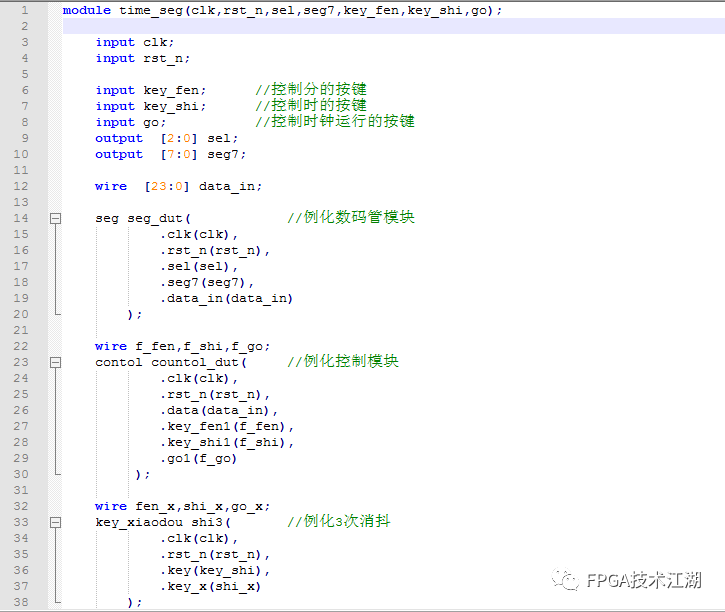

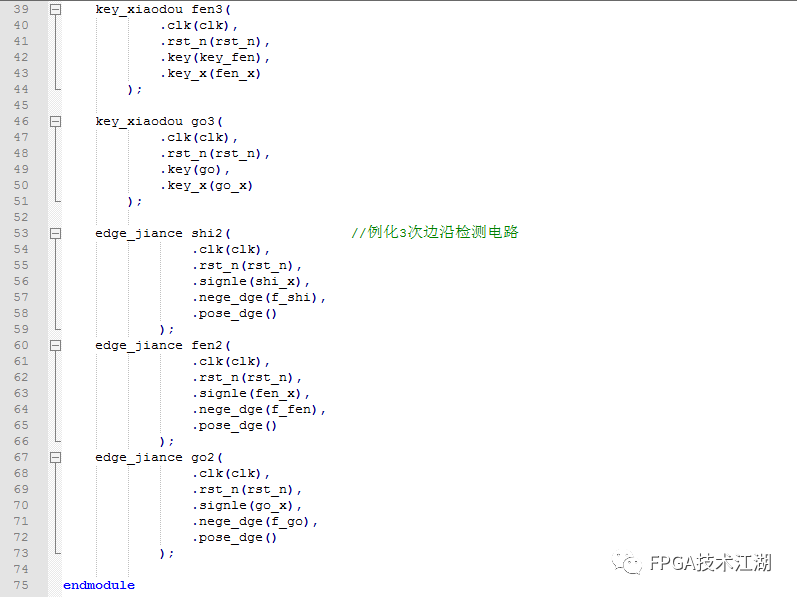

附设计代码:(源码文件可从公众号内部获取) 总模块:

按键模块:

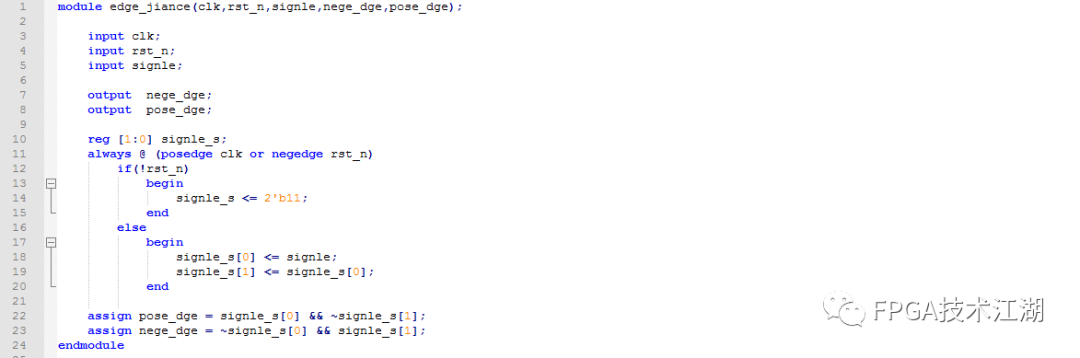

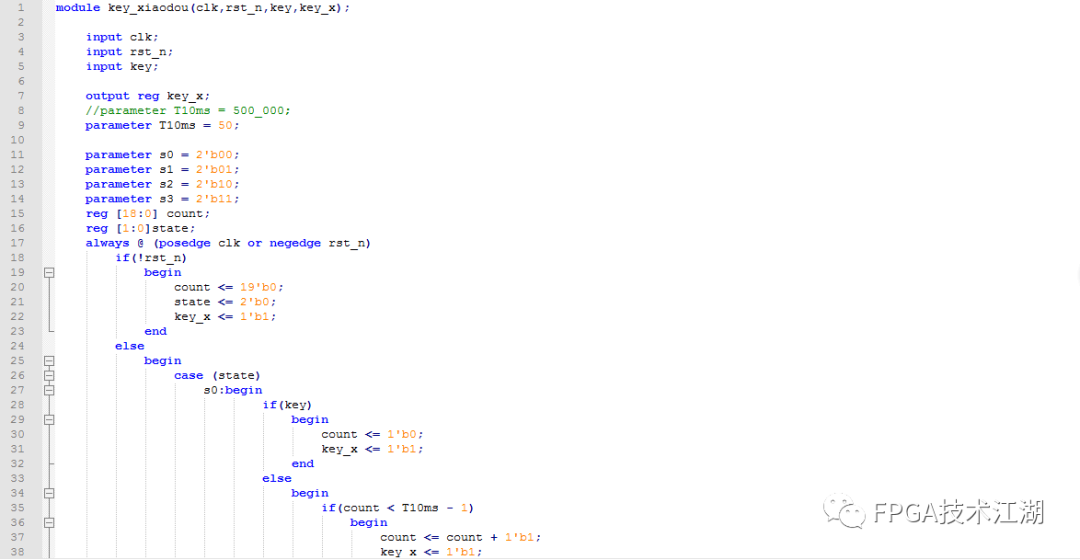

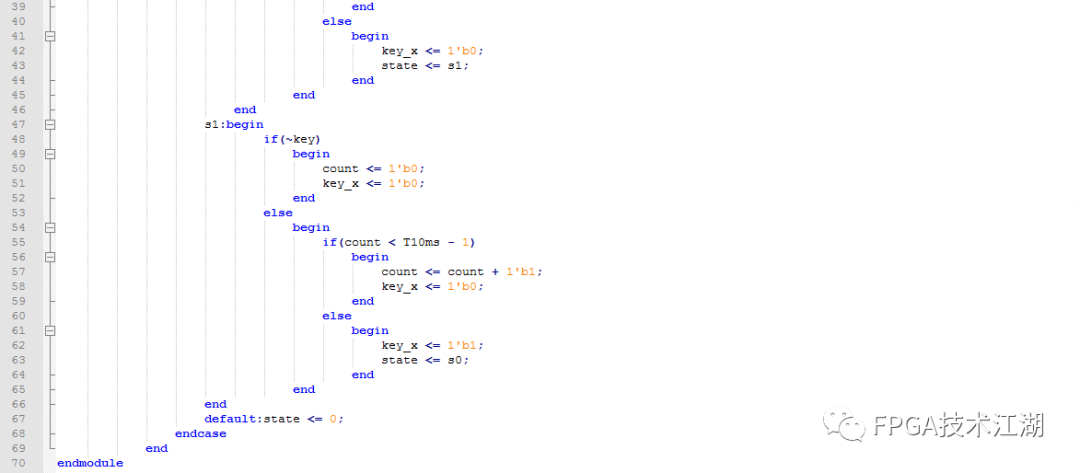

消抖模块:

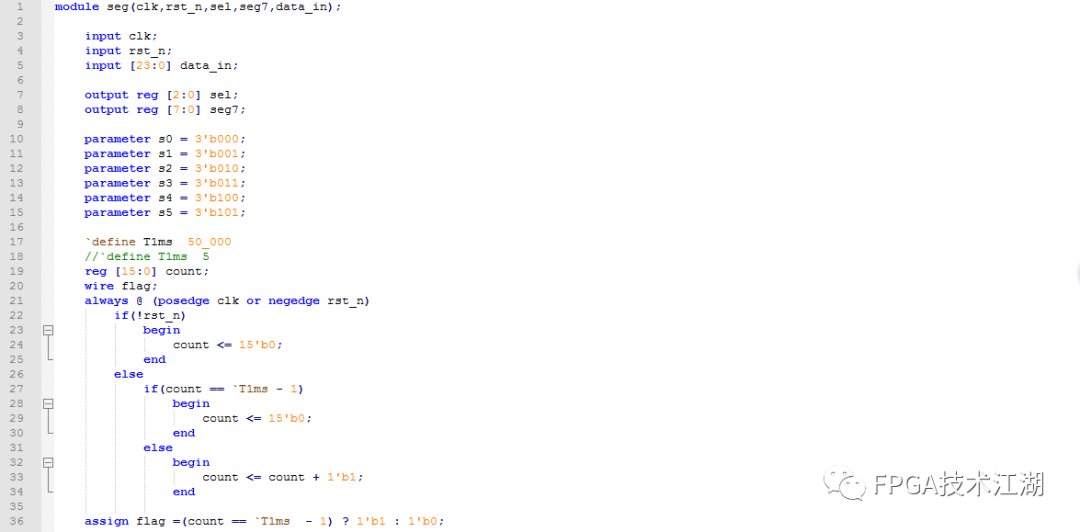

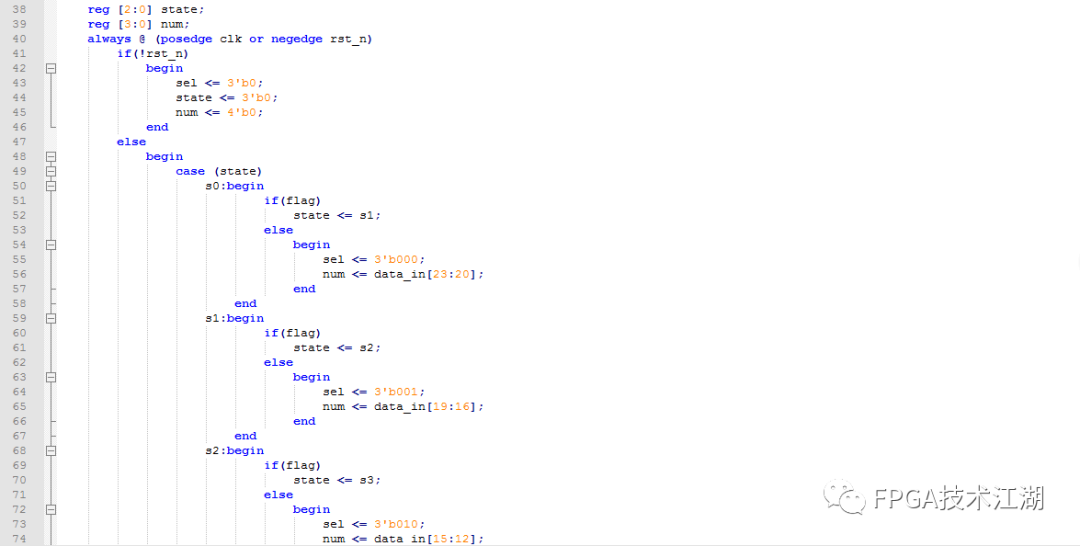

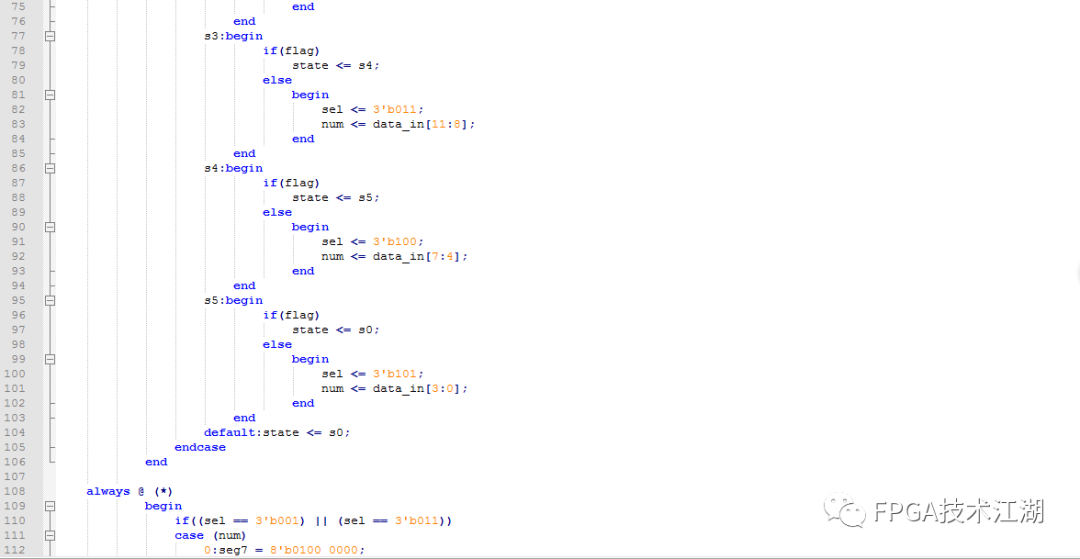

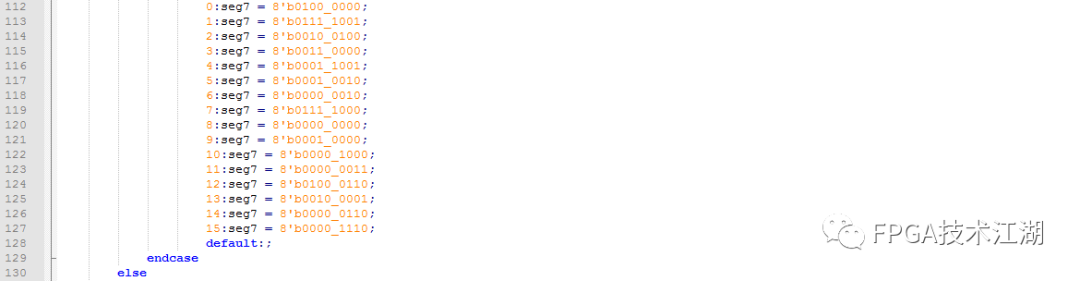

数码管模块:

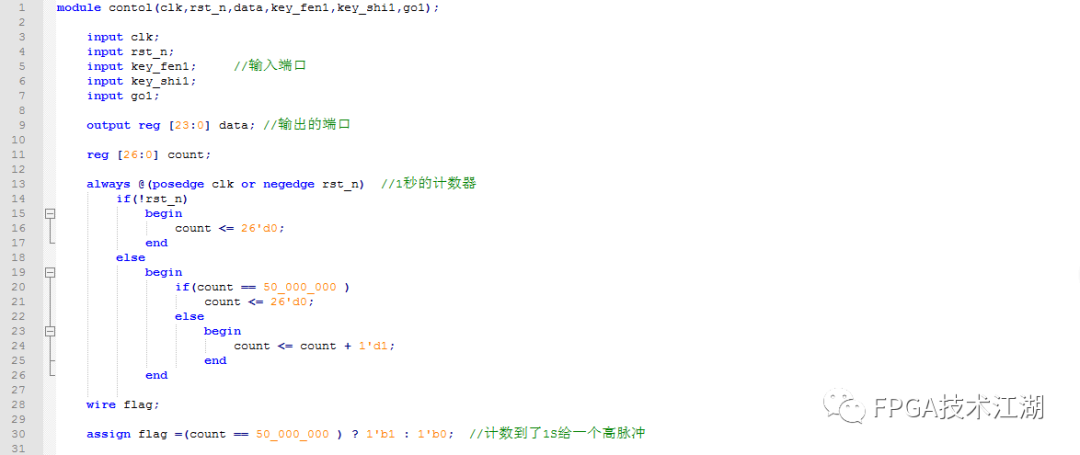

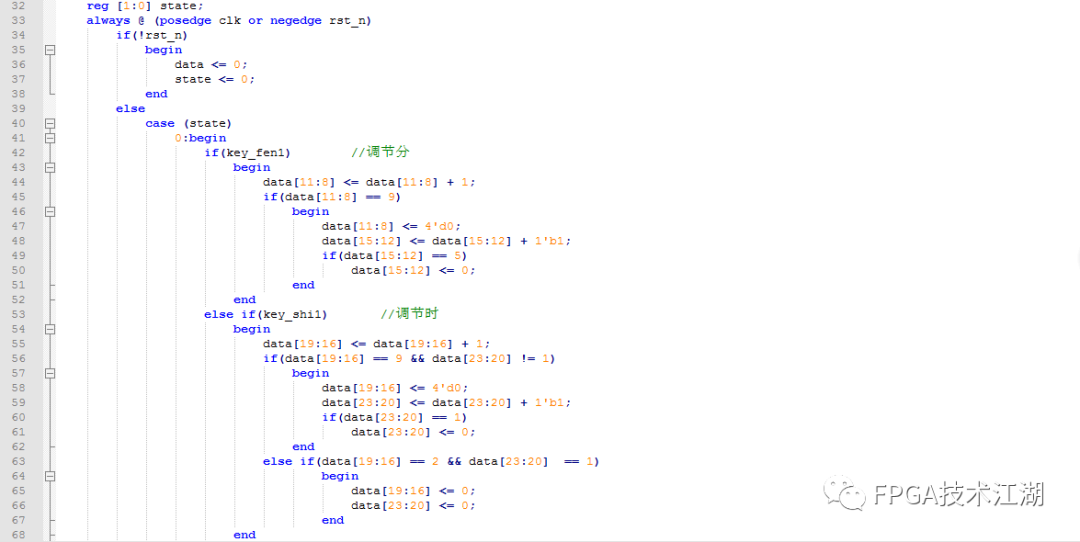

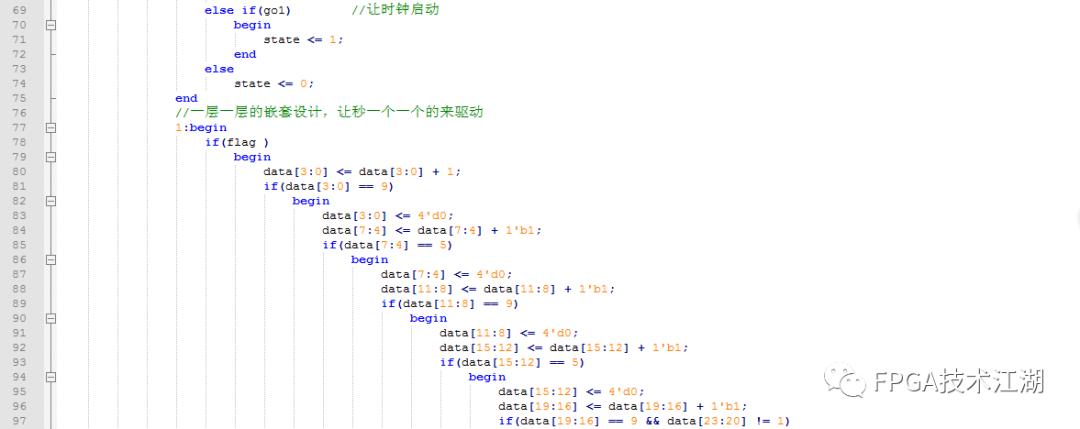

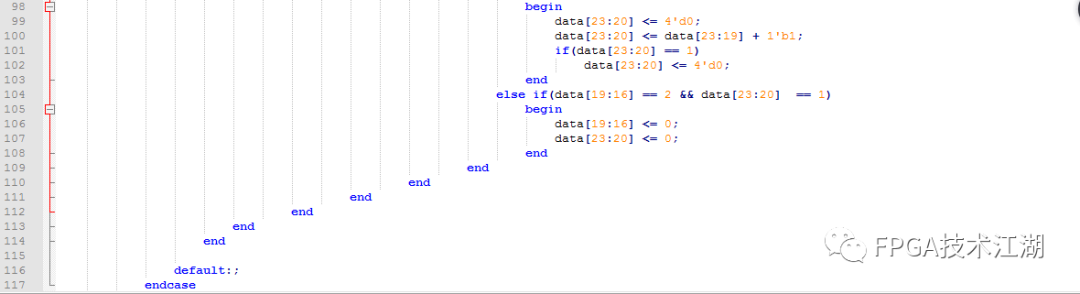

控制模块:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639097 -

代码

+关注

关注

30文章

4976浏览量

74373 -

数字时钟

+关注

关注

2文章

156浏览量

21650

原文标题:源码系列:基于FPGA数字时钟的设计(附源工程)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

如何把握FPGA的数字时钟管理器

,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。赛灵思现有的FPGA中没有一款同时包含这四种资源(见表1)。 这四大类中的每一种都针对特定的应用。例如,数字时钟管理器(DCM)适用于实现延迟锁相

FPGA的数字时钟电路解析

FPGA 在通信领域的应用可以说是无所不能,得益于 FPGA 内部结构的特点,它可以很容易地实现分布式的算法结构,这一点对于实现无线通信中的高速数字信号处理十分有利。

发表于 01-24 13:46

•1694次阅读

FPGA的外部时钟周期性地打开和关闭

嗨,我是FPGA的新手。我想知道我是否可以有一个设计,我的FPGA的外部时钟周期性地打开和关闭。我知道Xilinx FPGA使用数字

发表于 01-10 10:59

基于FPGA的时钟设计

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型

发表于 09-21 18:38

•4259次阅读

FPGA实现数字时钟

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进

发表于 11-29 16:51

•184次下载

基于FPGA的数字时钟

发表于 12-26 10:33

•43次下载

基于fpga的数字时钟设计应用

本工程包括矩阵键盘和数码管显示模块,共同实现一个带有闹钟功能、可以设置时间的数字时钟。具体功能如下:1. 数码管可以显示时十位、时个位、分十位、分个位、秒十位、秒个位。2. 上电后,数码管显示000000,并开始每秒计时。

发表于 04-19 10:27

•1.7w次阅读

基于FPGA的数字时钟实现

EDA技术使得电子线路的设计人员能在计算机上完成电路的功能设计、逻辑设计、时序测试直至印刷电路板的自动设计。本文介绍了以 VHDL 语言和硬件电路为表达方式,以 Quartus II 软件为设计工具,最终通过 FPGA 器件实现数字时钟

发表于 05-25 16:28

•40次下载

基于FPGA的数字时钟设计

基于FPGA的数字时钟设计

评论