一站式PCBA智造厂家今天为大家PCB设计中什么是高速信号?PCB设计中为什么高频会出现信号失真。在电子设备制造中,高速信号的处理成为PCB设计的关键。高速信号通常指频率范围从50 MHz到3 GHz的信号,例如时钟信号。在实际应用中,时钟信号并非理想的方波,而是具有上升和下降时间的梯形波。这些高频信号在传输过程中容易出现失真,影响系统的整体性能。因此,保证信号完整性在高速PCB设计中至关重要。

什么是高速信号?

高速信号通常指频率范围从50 MHz到3 GHz的信号,如时钟信号。尽管理想情况下时钟信号是方波,但实际中由于上升和下降时间的存在,时钟信号在时域中呈现梯形波形,而在频域中,其高频谐波的幅度取决于上升和下降时间。

为什么高频会出现信号失真?

在低频(>1kHz)下,信号保持在数据特征限制范围内。当速度增加时,高频率的影响开始显现,导致振铃、串扰、反射、接地反弹和阻抗不匹配问题。这些问题不仅影响系统的数字特征,还会影响模拟特征,进而影响I/O接口和内存接口的数据速率。通过PCB设计和有效的布局布线,可以避免这些问题。

保证高速PCB设计中信号完整性的7个措施

1. 阻抗控制

影响阻抗控制的三个因素是基板材料、走线宽度和走线距地/电源层的高度。高频信号传输时,走线的电感和电容开始影响性能,过孔存根和走线缺陷导致的阻抗不匹配会引起信号失真。

常见的终端方案:

- 并联终端方案:终端电阻(RT)等于线路阻抗,尽可能靠近负载放置。

- 戴维南终端方案:将终端电阻分成两个独立电阻,减少总电流。

- 有源并联终端:将终端电阻放置在偏置电压的路径上。

- 串联-RC并联终端:电阻和电容组合充当终端阻抗。

- 串联终端:匹配信号源端的阻抗,减少二次反射。

- 差分对端接:在接收端的信号之间需要一个终端电阻,必须匹配差分负载阻抗。

2. 防止传输损耗

- 介电吸收:高频介质中的信号使PCB介电材料吸收信号能量,降低信号强度。

- 集肤效应:高频信号生成的波形在高频时引发感抗增加,导致信号强度衰减。

3. 防止串扰

串扰是由于电流通过电线时在附近产生磁场而导致的信号能量交叉耦合。可以通过以下措施减少串扰:

- 走线间距:两条走线的中心间距至少是走线宽度的3倍。

- 接地层的放置:在不同层之间放置固体接地层。

- 低介电常数材料:通过降低走线之间的互电容/杂散电容来减少串扰。

4. 避免直角走线和注意过孔位置

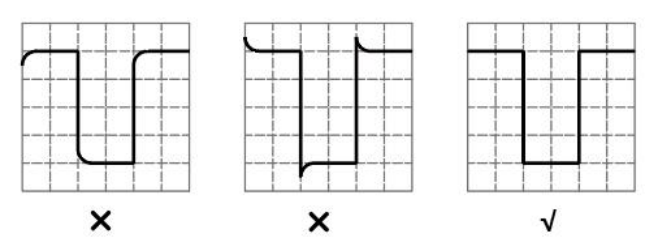

直角走线增加拐角区域的电容值,导致特性阻抗变化,引起反射。通过用两个45°角代替直角弯曲可以减少反射。过孔位置也会影响信号完整性,应尽量减少走线长度,避免不同走线中的过孔。

5. 不同走线

- 正交布线:在不同层上引导信号,最小化耦合区域。

- 短平行走线:减少信号之间的并行长度。

6. 避免接地反弹

数字电路需要快速开关时间,在“0”和“1”信号电平之间切换时会产生地弹,可以通过以下方法减少地弹:

- 引脚转换率控制:减慢驱动器的速度,降低跳动率。

- 多电源和接地引脚:防止靠近接地引脚位置的开关效应。

7. 降低EMI

电磁干扰(EMI)影响系统的EMI/EMC性能。可以通过以下措施减少EMI:

- 低电感元件:使用具体低ESR和有效串联电感(ESL)的表面贴装电容。

- 固体接地平面:在电源信号平面旁边使用实心接地平面。

其他建议

- 确定最高频率网络并计算系统中最快上升时间。

- 考虑走线上受控阻抗值、端接和传播延迟。

- 在带线和带状线路由技术之间进行选择。

- 考虑不同电源电压的数量。

- 为发射器路径、接收器路径、模拟信号、数字信号等功能创建图表。

- 确定两个独立功能组之间的连接,考虑返回电流和其他走线的串扰。

- 考虑空间宽度间隙。

- 确定最小钻孔和过孔要求,评估盲孔和埋孔的可行性。

通过这些措施,设计人员可以在高速PCB设计中有效保证信号完整性,提高系统性能和可靠性。

关于PCB设计中什么是高速信号?PCB设计中为什么高频会出现信号失真的知识点,想要了解更多的,可关注领卓PCBA,如有需要了解更多PCB打样、SMT贴片、PCBA加工的相关技术知识,欢迎留言获取!

审核编辑 黄宇

-

PCBA

+关注

关注

25文章

1961浏览量

57251 -

高速信号

+关注

关注

1文章

278浏览量

18528 -

PCB

+关注

关注

1文章

2355浏览量

13204

发布评论请先 登录

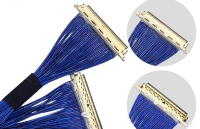

Samtec高速线缆深入解析:高速信号完整性的关键技术

高频PCB布线“避坑指南”:4大核心技巧让信号完整性提升90%

线路板阻抗匹配:实操中要避开的 3 个设计误区

三环电容ESL对高频信号完整性影响?

了解信号完整性的基本原理

深度解析:PCB高速信号传输中的阻抗匹配与信号完整性

深度解析:PCB高速信号传输中的阻抗匹配与信号完整性

评论