光学声子软化是光学声子的振动由“激昂强烈”变得“缓慢柔和”的现象,一般会引起材料的界面退极化效应,但通过拉升原子键降低化学键强度实现光学声子软化可以有效避免界面退极化效应,解决集成电路器件的应用难点,以及发展新原理器件具有重要意义。

光学声子软化,是凝聚态物理中非常重要的现象,与材料介电常数、晶体结构相变、铁电性相变、热电材料的热导率等重要领域相关。

但长期以来理论认为,光学声子软化的产生会同时引发材料的界面退极化效应,严重限制材料在纳米尺度器件大规模集成的实际应用。

近日,中国科学院半导体研究所提出一种光学声子软化新理论,能避免过去八十年来理论认为无法克服的界面退极化效应,有望以源头理论创新,推动高密度电子器件的设计与研发,该成果发表于《自然》。

01 传统认知中的双刃剑

什么是光学声子软化?晶体中的原子并不是静止不动的,光学声子,是晶体中正负离子相对振动时产生的一种特殊声子模式。当晶体光学声子模的振动频率不断降低直至零以下时,会导致晶格的动态不稳定,这种现象就是“光学声子软化”。形象地说,光学声子软化,就是光学声子的振动由“激昂强烈”变得“缓慢柔和”的现象。

然而,长期以来的认知却使光学声子软化的“潜能”得不到发挥,通常认为只有当长程库伦作用(较长距离范围内带电粒子之间的静电相互作用)较强、超越短程原子键强度时,才会产生光学声子软化。

这一过程也会产生“副作用”,引起界面的退极化效应,导致铁电性在纳米尺度消失,以及材料难以同时拥有高介电常数和大带隙。这犹如一道无法跨越的障碍,严重限制了技术的进一步发展。

02 反常中获得新突破

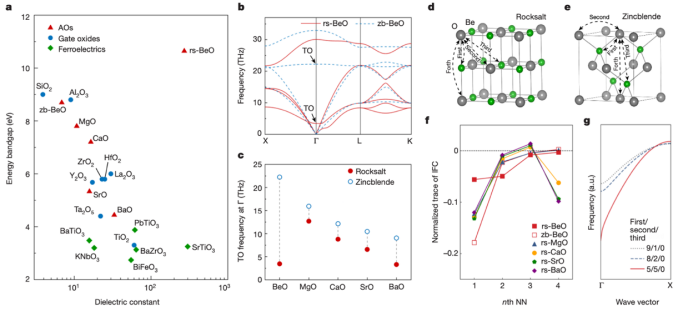

科研人员在工作中注意到,岩盐矿结构的氧化铍(rs-BeO)反常地拥有10.6 eV的超宽带隙和高达271 ɛ0的介电常数,均远高于当前集成电路中使用的新型高k氧化物介电材料二氧化铪(HfO2)的带隙(6 eV)和介电常数(25 ɛ0)。

通过进一步研究,科研人员揭示出这一反常的起源:由于rs-BeO中的Be原子很小导致相邻两个氧原子的电子云高度重叠,产生强烈的库仑排斥力,拉升了原子间距,显著降低了原子键的强度和光学声子模频率,导致其介电常数从闪锌矿相的3.2 ɛ0(闪锌矿相中相邻氧原子相距较远电子云重叠很小)跃升至271 ɛ0。

▲岩盐矿(rs-) BeO的反常现象及起源

基于这一发现,科研人员创新性地提出,通过拉升原子键降低化学键强度实现光学声子软化的新理论。由于这一光学声子软化驱动的铁电相变不依赖于强库仑作用,因此可以有效避免界面退极化效应。

离子半径差异、应变、掺杂、晶格畸变等现有的常规、成熟路径,都可以拉升原子键长度降低原子键强度。也就是说,这一光学声子软化方案具备从理论转向应用的实现基础。

03 新技术应时而生

众所周知的“摩尔定律”认为,集成电路上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。然而,每过一段时间,摩尔定律就会遇到新的障碍,陷入止步不前的局面,应变硅、高k栅介电层、FinFET晶体管等创新不断地拯救摩尔定律。

当前,通过晶体管持续小型化以提升集成度的摩尔定律已接近物理极限,主要问题在于晶体管功耗难以等比例降低。

新的光学声子软化理论,对于解决集成电路晶体管高k介电材料、铁电材料的应用难点,以及发展兼容CMOS工艺的超高密度铁电、相变存储等新原理器件具有重要意义。

相信在不久的将来,这一新理论成果将在高密存储器、传感器和纳米电子器件中得到广泛应用,为我们的生活创造更多便利。

-

晶体管

+关注

关注

78文章

10252浏览量

146279 -

光学

+关注

关注

4文章

833浏览量

37890

原文标题:突破晶体管功耗难题的新希望

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于 onsemi NST856MTWFT 晶体管的通用放大器设计与应用指南

电压选择晶体管应用电路第二期

0.45-6.0 GHz 低噪声晶体管 skyworksinc

多值电场型电压选择晶体管结构

下一代高速芯片晶体管解制造问题解决了!

无结场效应晶体管详解

多值电场型电压选择晶体管结构

晶体管电路设计(下)

晶体管电路设计(下) [日 铃木雅臣]

晶体管电路设计与制作

金刚石基晶体管取得重要突破

互补场效应晶体管的结构和作用

英特尔IEDM 2024大晒封装、晶体管、互连等领域技术突破

突破晶体管功耗难题新希望之光学声子软化

突破晶体管功耗难题新希望之光学声子软化

评论