1. 项目背景

蜜罐技术由来已久,蜜罐(Honeypot)是一种在互联网上运行的计算机系统。它是专门为吸引并诱骗那些试图非法闯入他人计算机系统的人(如电脑黑客)而设计的,蜜罐系统是一个包含漏洞的诱骗系统,它通过模拟一个或多个易受攻击的主机,给攻击者提供一个容易攻击的目标。由于蜜罐并没有向外界提供真正有价值的服务,因此所有对蜜罐尝试都被视为可疑的。蜜罐的另一个用途是拖延攻击者对真正目标的攻击,让攻击者在蜜罐上浪费时间。简单点一说:蜜罐就是诱捕攻击者的一个陷阱。根据蜜罐与攻击者之间进行的交互,可以分为3类:低交互蜜罐,中交互蜜罐和高交互蜜罐。

目前市面上的蜜罐都是利用软件来实现的,软件有它速度慢、依赖性强、程序复杂等弱点,基于蜜罐需要快速大量的数据匹配(入侵审计等)和安全的系统(简单),我们想到可以用硬件FPGA实现蜜罐技术。目前用硬件实现蜜罐技术在网络和相关书籍杂志上都不曾出现过。

2.项目目标

作为我们用XILINUX公司的SPARTEN-3E实验板来做的这次实验,我们在基本的低交互蜜罐的基础上,自己编写了操作系统和内核,做到了高交互的蜜罐系统。

3.项目的主要内容

本项目一共分为三部分

a.蜜墙的设定

功能:

利用FPGA实现IDS和入侵检测、入侵审计的功能

防止黑客利用蜜罐作为跳板攻击服务器

b.蜜罐的构建

功能:

用FPGA模拟出一个真实的操作系统

在FPGA实验板上用操作系统建立一个高交互的蜜罐,让黑客攻击

c.数据的采集和分析

功能:

把蜜罐上的有效数据安全的转移到其他地方

研究并分析黑客或木马病毒的攻击行为

4.项目关键技术及创新点的论述

关键技术包括:IDS入侵检测、入侵审计、蜜罐技术及其相关的日志记录分析,honeynet和蜜墙功能。

国内目前还没有任何用FPGA或者相关的硬件平台来实现蜜罐、蜜墙,所有的蜜罐技术都是基于在软件平台上的实现。同时,FPGA的终端安全防护一直处于被动防护的状态,如果可以用蜜罐技术,就能把终端防护由被动变为主动,能加有效安全得保护终端的安全。

5.项目的成果

我们最终完成了项目主要工作中的功能实现,并对于整个蜜罐蜜墙所组成的系统用不同的攻击手段进行了测试,测试结果表明,我们用FPGA实现的这套系统可以完成期望的目标。

1.采用FPGA实现蜜墙技术,几乎包含现在终端攻击中全部的攻击方式的入侵检测。

2.利用蜜墙将攻击诱导到FPGA实现的蜜罐上。

3.实现了日志记录,检测并分析攻击的特征和方式,来更进一步了解攻击,为今后的防御赢得主动。

需求分析和项目目标

1.1 需求分析

蜜罐发展的3个过程:

低交互蜜罐最大的特点是模拟。蜜罐为攻击者展示的所有攻击弱点和攻击对象都不是真正的产品系统,而是对各种系统及其提供的服务的模拟。由于它的服务都是模拟的行为,所以蜜罐可以获得的信息非常有限,只能对攻击者进行简单的应答,它是最安全的蜜罐类型。

中交互是对真正的操作系统的各种行为的模拟,它提供了更多的交互信息,同时也可以从攻击者的行为中获得更多的信息。在这个模拟行为的系统中,蜜罐可以看起来和一个真正的操作系统没有区别。它们是真正系统还要诱人的攻击目标。

高交互蜜罐具有一个真实的操作系统,它的优点体现在对攻击者提供真实的系统,当攻击者获得ROOT权限后,受系统,数据真实性的迷惑,他的更多活动和行为将被记录下来。缺点是被入侵的可能性很高,如果整个高蜜罐被入侵,那么它就会成为攻击者下一步攻击的跳板。

但是,如果我们有一个蜜墙来有效的防治黑客利用蜜罐作为跳板,那么就可以很好的解决高交互蜜罐的缺点,让蜜罐真正变成一个我们可以控制的安全的陷阱。并且我们用硬件实现蜜罐技术,比用软件在速度上快数百倍,FPGA上可以安装实时性操作系统,并且硬件比软件在程序上更简单、更基础,防护效果更好。

1.2实现的功能目标

用FPGA实现高交互的蜜罐技术并实现蜜墙功能,通过对硬件的底层编程实现

1.3项目可行性分析

因为用硬件实现蜜罐技术在目前世界、至少是中国网站上没有出现过,属于首创,里面的很多技术问题尤其是软件到硬件的编程和实现是我们所面临的主要问题,但是硬件的速度快,结构简单,实时性好,这些特点我们可以充分利用在蜜罐和蜜墙上,来实现我们的硬件蜜罐,比软件实现的优势还是非常的明显的。

项目总体设计

2.1总体结构图

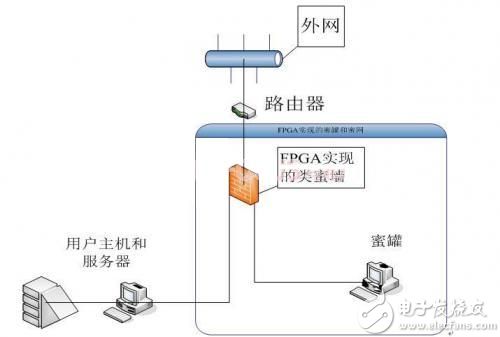

上面是我们大致的系统架构图。我们可以看到,以太网相当于外网通过路由器首先经过我们用FPGA实现的蜜墙。他具有IDS、入侵检测、入侵审计等多种功能,最重要的是,高交互的蜜罐很容易在被攻破以后被黑客作为攻击主服务器的跳板,但是蜜墙就可以做好很好的防止从蜜罐到服务器的攻击,简单的说,他对于蜜罐是一个只进不出的防火墙。

数据流经过了蜜墙以后,我们对数据进行分析,当没有发现攻击信息的时候,数据流作为正常数据通过蜜墙发给服务器,如果我们检测出了入侵攻击,那么蜜墙会利用IP欺骗技术把攻击的数据流引到蜜罐上,这样黑客攻击的就只能是蜜罐而无法接触到真正的服务器。

在蜜罐上,我们进行实时监控,黑客的一举一动都在我们的监视下,通过安全的途径把蜜罐上的信息导出,我们可以分析这些信息对黑客的行为进行了解和掌握,并以此来对未来其他的攻击方式进行主动的防御。

FPGA硬件实现带网络连接的操作系统内核

3.1系统硬件的基本构成与配置

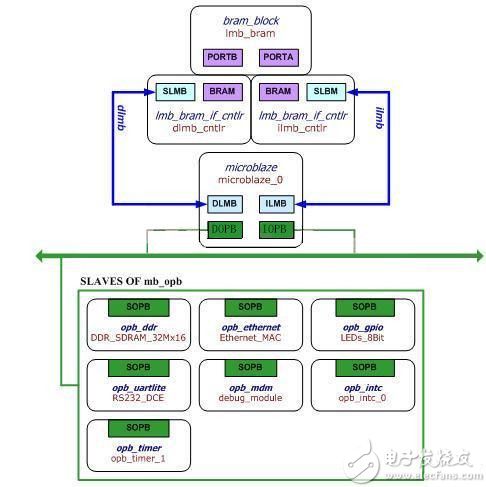

系统的硬件设计使用 Xilinx Platform Studio 集成开发环境中的 Base System Builder 进行配置。完成设计的系统框图如图XX所示。

系统硬件框图

整个系统硬件的核心是Microblaze 处理器,处理器的基本配置和主要外设包括:

3.2 硬件功能与指标

一、Microblaze 处理器:

处理器总线频率: 66.7 MHz;

片上内存(BRAM):16KB;

由于Spartan-3e XC3S500E 的BRAM资源有限,没有选择 Cache 功能;

二、基本外设配置:

波特率:115200,使用中断;

(2)以太网MAC:

使用 Xilinx Ethernet_MAC IP,其配置参数为:No DMA,使用中断,并选择 FIFO 方式,以满足在 Xilkernel 系统下,使用lwIP 进行 socket 编程的需求;

(3)定时器:

采用一个32位定时器,并使用中断。

使用开发板上的 32Mx16内存,并配置为 OPB DDR。

此外,系统硬件中还包括:中断控制器、8个与通用I/O连接的LED,以及调试模块。更为详尽的硬件平台细节,可以参照系统的硬件描述文件(MHS)。

-

FPGA

+关注

关注

1664文章

22508浏览量

639414

发布评论请先 登录

ARK7118 AHD视频输出电路设计要点与硬件实现分析

风扇电机驱动板的调速控制与硬件实现技术

电子工程师设计相关要点与案例分析

FPGA 入门必看:Verilog 与 VHDL 编程基础解析!

总结学习硬件设计要点

ADC模数转换实战:硬件设计与软件开发要点指南!

构建可靠USB应用:硬件设计要点与LuatOS开发技巧!

复杂的软件算法硬件IP核的实现

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

使用Verilog在FPGA上实现FOC电机控制系统

基于Matlab与FPGA的双边滤波算法实现

基于FPGA的压缩算法加速实现

用硬件fpga实现蜜罐技术的这些要点,学到就赚了

用硬件fpga实现蜜罐技术的这些要点,学到就赚了

评论