现代高级雷达系统正在受到多方面的挑战——

频率分配上的最新变化导致

许多雷达系统的工作频率非常接近

通信基础设施和其他频谱要求极高的系统。

未来,频谱拥塞状况预期会更严重

问题将恶化到雷达系统需要在运行时进行调整以适应环境和运行要求,

这使得雷达系统需要向认知化和数字化发展。

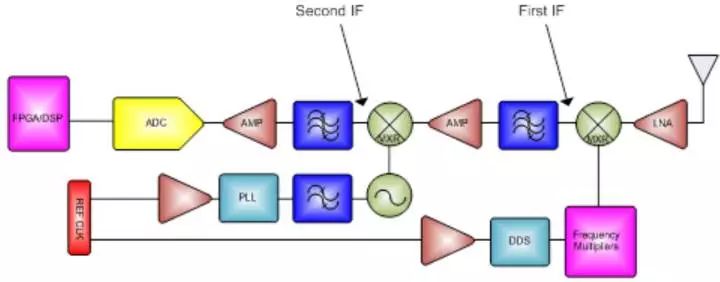

更多数字信号处理的需求推动雷达信号链要尽早向数字化过渡,使得ADC更靠近天线,这进而又会带来若干具挑战性的系统层面难题。为了更深入地讨论这个问题,图1显示了目前典型的X波段雷达系统的高层次概略图。该系统通常使用两个模拟混频级。第一级将脉冲式雷达回波混频至约1 GHz频率,第二级混频至100至200 MHz的中频(IF),以便能够利用200 MSPS或更低的模数转换器对信号进行12位或更高分辨率的采样。

图1. 使用第一和第二中频(IF)的雷达接收机架构示例

在该架构中,频率捷变和脉冲压缩等功能可在模拟域中实现,这可能需要对信号处理进行一些更改和调整,但大体而言,系统功能受限于数字化速率。应当注意,即使以200 MSPS的数据速率进行采样,雷达处理也能向前跨进一大步,但我们正在向新的阶段突破,步子必须再迈大一点,实现全数字化雷达。

挑战

近年来,每秒千兆采样(GSPS) ADC已将系统中的数字化点推进到第一混频级之后,使得数字化转变更接近天线。模拟带宽超过1.5 GHz的GSPS转换器已然能够支持第一中频的数字化,但在许多情况下,当前GSPSADC的性能限制了这种解决方案的接受程度,因为器件的线性度和噪声频谱密度不满足系统要求。

另外,高速ADC与数字信号处理平台(通常是FPGA)之间的数据移动,直到最近还是以并行低压差分信号(LVDS)接口为主要途径。然而,使用LVDS数据总线从转换器输出数据会带来一些技术难题,因为单条LVDS总线所需的工作速率将远远超过IEEE标准的最大速率以及FPGA的处理能力。为了解决这个问题,输出数据需要解复用到两条或(更一般地)四条LVDS总线,以便降低每条总线的数据速率。

例如,采样速率超过2 GSPS的10位ADC通常将需要对输出进行4倍解复用,LVDS总线宽度将达40位。而许多雷达系统,尤其是相控阵,会采用多个GSPS ADC,如此多的通道需要布线和长度匹配,硬件开发很快就会变得无法管理,更不用说互连所需的FPGA引脚数量!

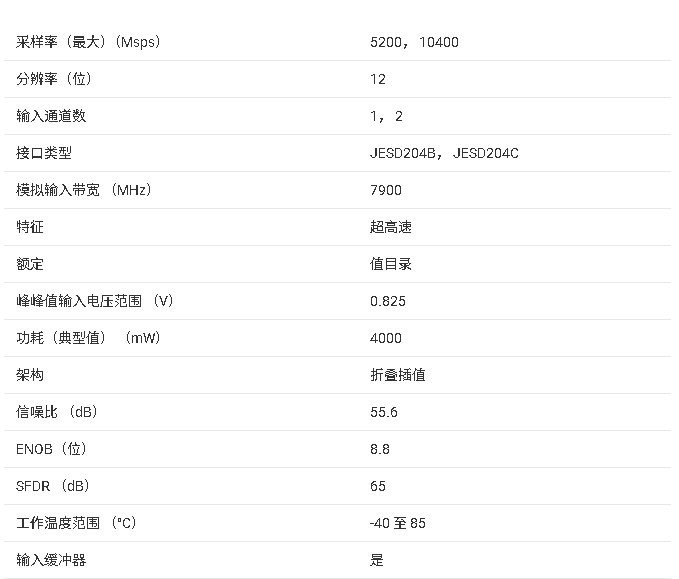

新型GSPS ADC不仅能克服现有挑战,而且可进一步优化系统。为使数字化更接近天线,此类转换器提供无与伦比的线性度和3 GHz以上的模拟带宽,支持L波段和大部分S波段的欠采样。这样,在这些波段内就可以直接进行RF采样,而无需混频器级,器件数量和系统尺寸得以缩减。更高频率的系统也能使用更高中频,从而可以减少混频级和滤波器的数量,并且由于能够使用宽范围的中频,频率规划选项得以增加。

更高的线性度和更低的噪声频谱密度使此类新器件能够用于下一代雷达系统。随着频谱密度提高,必须提供更高的动态范围才能管理雷达回波频率附近的阻塞或干扰信号。

最新的GSPS ADC能够提供75 dBc以上的SFDR,比最近十年面市的器件高出近20 dBc。与新近的通信基础设施频率分配相竞争时,这一跨越式进步显得更加重要。

解决方案

模拟带宽、线性度和噪声方面的改善可以被看作是器件制造商的下一步逻辑发展。不过,新型GSPS ADC的两个新增特性可为系统设计师带来更大的便利,有可能会提高这些器件在未来系统中的接受程度:

JESD204B数据链路接口优势若干高速ADC最近已引入JESD204B数据链路,但它对GSPS转换器最有好处,因为LVDS接口已很难满足系统需求。JESD204B是一种高速串行标准,支持利用更少数量的差分互连(FPGA引脚)实现高速ADC与FPGA或其他处理器之间的数据传输。它是一种开销非常低的协议,基于8b10b编码方案,支持高达12.5 Gbps的波特率。

下面以ADI的新型2.0 GSPS、12位转换器AD9625为例来讨论其优势。该转换器的输出数据速率是24 Gbps。假设LVDS数据总线的最高速率是1Gbps,并且忽略数据包装问题,那么将需要24个LVDS对才能支持此接口,硬件布线时,所有对的PCB走线长度都需要匹配。若采用最大波特率为6.25 Gbps的JESD204B,则只需要6条JESD204B链路就能支持此转换器的输出。图2清楚显示了其优势,AD9625与FPGA之间仅需布设8条JESD204B通道即可支持全数据速率2.0 GSPS。

图2. 采用JESD204B的GSPS FPGA夹层卡(FMC) PCB布线

此外,当使用多条JESD204B通道时,PCB走线长度匹配的要求大幅放松,因为标准仅要求通道间对齐精度达到920 ps,各JESD204B通道的路径延迟允许存在较大的差异。JESD204标准的最新“B”版还支持确定性延迟,可以计算离开高速ADC的数据与到达FPGA的数据之间的延迟。如果该延迟时间可以确定,那么就可以在数字后处理中予以补偿,使数据流重新对齐并同步,这是采用GSPS转换器的相控阵和波束成形系统的关键要求。

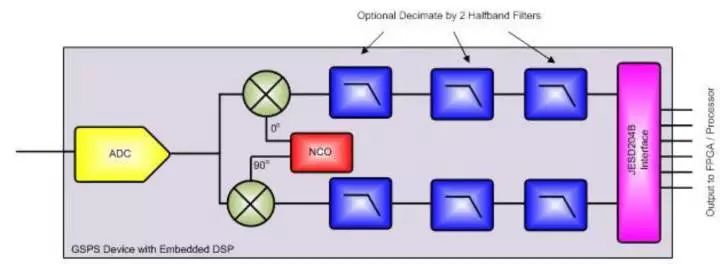

JESD204B对硬件设计师特别有利,但新型高速ADC的最大好处可能是增加了数字信号处理。AD9625等新一代GSPS转换器基于65 nm或更小几何尺寸的CMOS工艺,能够以非常高的数据速率支持各种各样的数字信号处理。近期而言,高速ADC将嵌入运行时可选的数字降频转换器(DDC),如图3所示。

转换器中嵌入的DSP功能雷达波形带宽因应用不同而有很大差异,例如,某些合成孔径成像雷达波形需要数百MHz的带宽,而跟踪雷达使用的波形带宽可能只有数十MHz或更少。过去,若GSPSADC更靠近天线,则意味着在某些情况下会有大量不需要的带宽被传输到FPGA或处理器。在现代FPGA和高速ADC中,如果不是大部分,也有相当一部分功耗与器件的接口相关,因此,毫无用处地传输大量不需要的带宽会提高系统功耗。在未来的多模式雷达中,动态使能DDC的能力将是一大优势,可减轻FPGA的复杂处理负荷。

图3. 带嵌入式DSP的新型GSPS ADCMS-2670

DDC集数字数控振荡器(NCO)和抽取滤波器于一体,能够在高速ADC的奈奎斯特频段内选择信号带宽和信号位置,仅将需要的适当数据传输给信号处理器件。例如,考虑一个在800 MHz的中频使用30 MHz带宽波形的雷达。如果用一个ADC以2.0 GSPS的采样速率进行12位分辨率的采样,则数据输出带宽将是1000 MHz,远远超过信号带宽,转换器的输出数据速率将达3.0 GB/s。如果利用DDC以16倍的比率抽取数据,则不仅能进一步降低噪声,而且输出数据速率降至625 MB/s以下,这样只需使用一条JESD204B通道就能传输数据。整体系统的功耗需求将因此而大幅降低。由于可根据需要动态配置DDC或予以旁路,新型高速ADC可在不同模式之间切换,以便支持针对功耗和机具进行优化的解决方案,并且帮助实现认知式雷达应用所需的特性集合。

结论

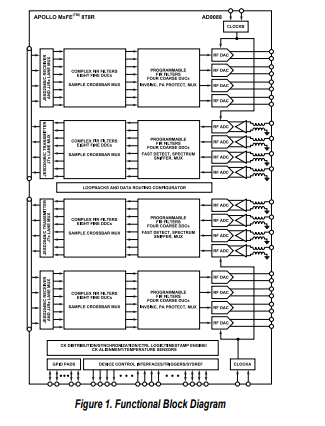

AD9625等新型GSPS ADC为雷达系统架构师提供了多种重要的选项,其模拟带宽和采样速率有助于减少器件数量或进行直接RF采样。JESD204B接口和嵌入式DSP选项使得设计师获取这些优势再也不需要付出提高功耗和板复杂度的代价。动态配置高速ADC的能力可实现多功能支持,满足创建全数字式认知雷达系统的需求。

原文转自亚德诺半导体-

雷达系统

+关注

关注

7文章

259浏览量

29466 -

AD9625

+关注

关注

0文章

6浏览量

13118 -

gsps_adc

+关注

关注

0文章

1浏览量

1825

原文标题:【世说设计】GSPS ADC担纲,两大特性定制雷达系统“瘦身计划”

文章出处:【微信号:Excelpoint_CN,微信公众号:Excelpoint_CN】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

ADC081000:高性能低功耗8位、1GSPS A/D转换器的深度解析

MD6639高速DAC芯片替代TI、ADI

ADC12DJ5200RF 具有双通道 5.2 GSPS 或单通道 10.4 GSPS 的射频采样 12 位 ADC技术手册

MD663B高速12位模数转换器(DAC)替代TI、ADI

DALI数字照明控制的解决方案

DS875替代AD9914/AD9958/AD9102/DAC38J84/LMK04828

4通道12位16GSPS!国产高速ADC再突破!

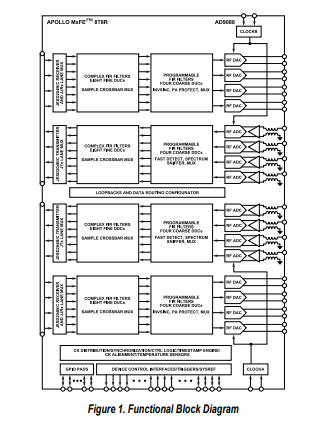

AD9088八通道、16 位、16 GSPS RF DAC和八通道、12位、8 GSPS RF ADC技术手册

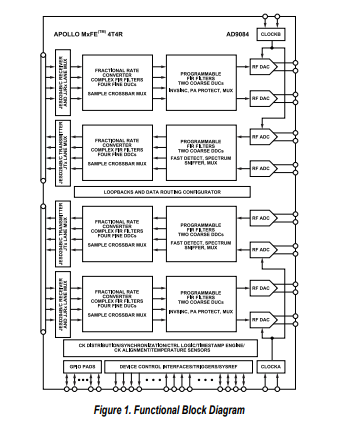

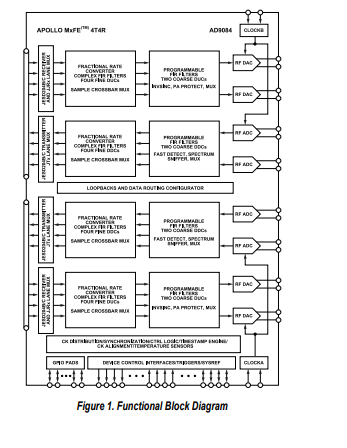

AD9084 Apollo MxFE四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技术手册

AD9088 Apollo MxFE 八通道、16位、16 GSPS RF DAC和八通道、12位、8 GSPS RF ADC技术手册

AD9084 MxFE 四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技术手册

schneeberger测量读数头的分类AMSD 3B数字式/滚柱型

直接数字式频谱分析仪的技术原理和应用场景

ADMV9625: 60 GHz Millimeterwave Short Data Link Preliminary Data Sheet adi

基于ADI新型GSPS ADC AD9625的数字式认知雷达系统解决方案

基于ADI新型GSPS ADC AD9625的数字式认知雷达系统解决方案

评论