MOS(金属氧化物半导体)集成电路由于其高集成度和敏感的氧化层结构,对静电放电(ESD)非常敏感。ESD事件可能会损坏或破坏MOS器件,导致性能下降或设备完全失效。因此,采取有效的ESD防护措施对于保护MOS集成电路至关重要。

1. 设计阶段的ESD防护

在设计MOS集成电路时,需要从多个层面考虑ESD防护:

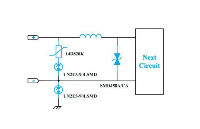

- ESD保护结构 :在芯片的关键部位,如输入/输出(I/O)端口、电源和地线等,设计ESD保护结构,如硅基二极管、多层金属互连、ESD防护二极管等。

- 井区隔离 :使用隔离井区(wells)来隔离不同功能的电路区域,减少ESD事件对敏感区域的影响。

- 器件布局 :合理布局芯片上的器件,将ESD保护结构放置在芯片的边缘或I/O端口附近,以提供第一道防线。

- 电源管理 :设计稳健的电源管理电路,确保电源电压在异常情况下不会超过器件的最大额定值。

- 输入保护 :对输入信号进行保护,使用限流电阻、电压钳位二极管等元件来吸收和分散ESD能量。

2. 制造过程中的ESD防护

在制造过程中,需要采取以下措施来防止ESD对MOS集成电路的损害:

- 洁净室环境 :在无尘、控制湿度的洁净室环境中进行芯片制造,减少静电的产生。

- 接地系统 :确保制造设备和工作台有良好的接地,以导引静电安全地流向地面。

- 防静电材料 :使用防静电垫、防静电包装材料和防静电工作服等,减少静电的积累。

- 操作规范 :制定严格的操作规范,确保操作人员了解ESD的危害和防护措施。

3. 测试和封装阶段的ESD防护

在测试和封装阶段,ESD防护同样重要:

- ESD测试 :对MOS集成电路进行ESD测试,确保其满足规定的ESD标准。

- 防静电设备 :使用防静电设备,如离子风扇、静电消除器等,以减少测试和封装过程中的静电。

- 封装材料 :选择具有良好防静电性能的封装材料。

- 操作培训 :对操作人员进行ESD防护培训,确保他们了解和遵守ESD操作规程。

4. 使用和运输阶段的ESD防护

在MOS集成电路的使用和运输阶段,也需要采取相应的ESD防护措施:

- 防静电包装 :在运输和存储过程中,使用防静电包装材料来保护MOS集成电路。

- 操作环境 :确保使用环境的湿度控制在适当范围内,以减少静电的产生。

- 防静电接地 :在使用设备时,确保设备和操作人员都有良好的防静电接地。

- 防静电标识 :在包装和设备上明确标识ESD防护的注意事项,提醒用户注意ESD问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成电路

+关注

关注

5464文章

12688浏览量

375744 -

ESD

+关注

关注

50文章

2426浏览量

180429 -

静电放电

+关注

关注

4文章

312浏览量

46089 -

MOS

+关注

关注

32文章

1759浏览量

101243

发布评论请先 登录

相关推荐

热点推荐

喜报 | 匠芯创亮相2026珠海集成电路年会 荣膺集成电路杰出人物与创新集成电路人才

4月23日,备受行业关注的“芯聚珠海,智驱未来——2026珠海集成电路产业年会暨产业高质量发展交流会”在珠海圆满落幕。这场由珠海市半导体行业协会主办的行业盛会,汇聚了政府领导、国家级行业专家、企业家

行芯科技亮相IIC 2026国际集成电路展览会暨研讨会

近日,全球集成电路领域的年度标杆盛会——2026国际集成电路展览会暨研讨会(IIC 2026)在上海圆满落幕。

关于“静电放电(ESD)现象”的详解

对于集成电路芯片领域,静电放电就是一个不可忽视的重大问题,因为静电放电可以在短时间内产生几百甚至几千伏高压,虽然持续时间很短,但是足以给半导体芯片(IC)的某个部位造成不可逆的热损伤。

焕新启航·品质跃升 IICIE国际集成电路创新博览会,构建全球集成电路全产业链生态平台

为积极响应国家集成电路创新发展战略部署,加快推进集成电路产业良性发展生态,原“SEMI-e深圳国际半导体展暨集成电路产业创新展”正式升级为“ IICIE国际集成电路创新博览会(简称 I

PDK在集成电路领域的定义、组成和作用

PDK(Process Design Kit,工艺设计套件)是集成电路设计流程中的重要工具包,它为设计团队提供了与特定制造工艺节点相关的设计信息。PDK 是集成电路设计和制造之间的桥梁,设计团队依赖 PDK 来确保设计能够在晶圆厂的工艺流程中正确制造。

100V200V250V MOS管详解 -HCK450N25L

管较强的抗辐射性能,适用于特殊环境。

应用领域

MOS管广泛应用于模拟电路、数字电路及功率电路等领域。凭借其高输入阻抗、制造工艺简单和设计灵活等优势,

发表于 08-29 11:20

设计电源时防止EMI的22个措施

影响到 100M 以下的频段。也可以在 MOS,二极管上加相应吸收回路,但效率 会有所降低。

设计开关电源时防止 EMI 的措施 1.把噪音电路节点的 PCB 铜箔面积最大限度地减小;如开关管的漏极

发表于 06-04 17:45

半导体芯片的ESD静电防护:原理、测试方法与保护电路设计

两个物体间转移(例如从人体到集成电路)。这种电荷转移可能导致极高电流在极短时间内流经芯片,若器件无法快速耗散能量就会造成损坏。ESD威胁贯穿产品全生命周期:在制造组

MOS集成电路防止静电干扰方法详解

MOS集成电路防止静电干扰方法详解

评论