PCIE是一种高速串行总线接口标准,用于连接计算机内部的各种外设和组件。在PCIe架构中,BAR(Base Address Register)空间是用于映射I/O端口或内存地址空间的一组寄存器。

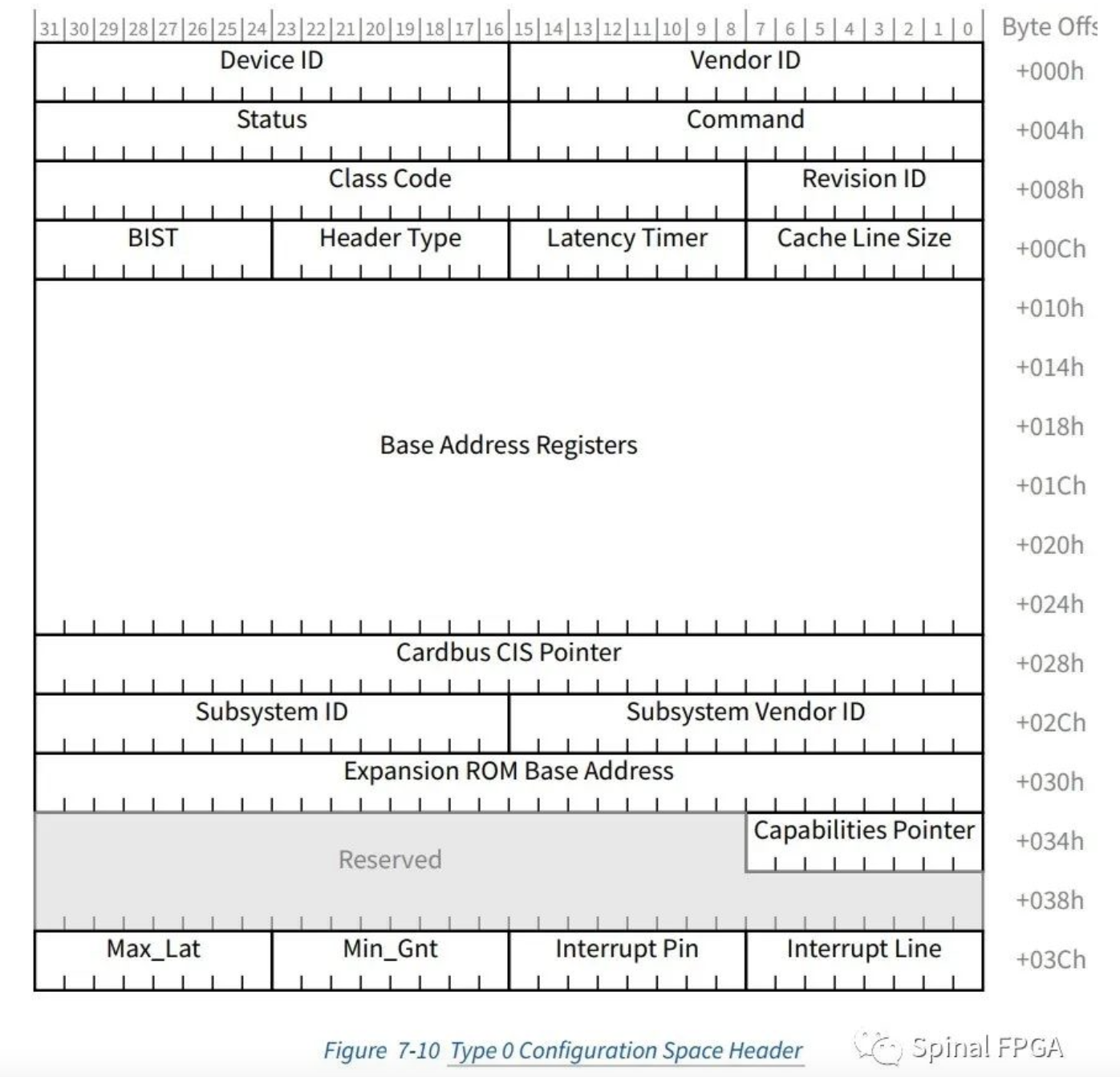

BAR空间是通过PCIe配置空间进行分配和管理的。每个PCIe设备都具有其自己的配置空间,其中包含了一组BAR寄存器。这些寄存器用于告知操作系统和其他设备该设备所需的资源,例如内存地址范围或I/O端口地址范围。

在PCIe设备的BAR寄存器中,可以配置为I/O BAR或者内存BAR。I/O BAR用于映射设备的I/O端口,而内存BAR用于映射设备的内存地址。每个BAR寄存器都包含一个基地址和一些控制位,用于指定地址范围和访问权限。

操作系统在初始化PCIe设备时,会读取BAR寄存器的值,并将相应的资源映射到系统地址空间中,以便应用程序可以通过访问这些地址来与设备进行通信。BAR空间的大小取决于每个BAR寄存器的配置,通常情况下,每个BAR寄存器的大小为32位或64位。

需要注意的是,BAR空间的大小可能会受到一些限制,例如操作系统或主板的限制。因此,在进行PCIe设备设计和驱动程序开发时,需要遵循相关的规范和要求,以确保BAR空间分配的合理性和可用性。

总结起来,PCIe的BAR空间是用于映射设备的I/O端口或内存地址空间的一组寄存器,通过配置寄存器的值,可以告知操作系统和其他设备该设备所需的资源。操作系统会将BAR空间映射到系统地址空间中,以便应用程序可以与设备进行通信。

-

寄存器

+关注

关注

31文章

5620浏览量

130454 -

计算机

+关注

关注

19文章

7841浏览量

93493 -

PCIe接口

+关注

关注

0文章

128浏览量

10657

原文标题:pcie的BAR空间的介绍

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCIE的BAR空间介绍

PCIE的BAR空间介绍

评论