你可能已经在当地道路上亲眼目睹了自动驾驶驱动的汽车系统的进步。5G网络和人工智能(AI)等技术的集成使自动驾驶汽车的性能比以往任何时候都更好,但新的严格安全标准又增加了一层考虑因素。

这些发展带来了芯片复杂性的增加和片上系统(SoC)设计要求的变化,例如重新架构(特别是传统控制器局域网(CAN)的车载电气/电子(E/E)架构)、车载以太网的引入、更高的速度以及与各种标准兼容的实时控制。验证这些复杂的SOC可能会占用高达70%的项目周期,并涉及更多的工程师时间!

瑞萨科技(公司名称)作为面向汽车、工业和信息技术(IT)等应用的微控制器、模拟、电源和SoC产品的全球领导者,就遇到了这一挑战,并计划利用以下优势将成本降低50%Synopsys VSO.ai(验证空间优化),一种AI和机器学习驱动的验证空间优化技术。

瑞萨的验证挑战

尤其是在汽车市场,上市时间的压力可能非常大。这就是为什么瑞萨的核心知识产权部门正在探索不同的方法来自动化其验证周期中的覆盖关闭阶段。工程师们经历了一系列不同的挑战,包括手动分析和分类,以确定未命中覆盖率,并确保产品随时可用,并彻底验证任何逻辑或功能问题。所有这些都必须在每个IP/项目的特定计算预算内完成。

关闭覆盖的“最后一英里”涉及开发针对未命中覆盖的定向测试。瑞萨没有采用编写定向测试来填补覆盖漏洞的手动流程,这可能会导致运行数千次投资回报(ROI)未知的回归,而是渴望通过利用AI/ML技术来尝试一些新奇的东西,这引发了他们对VSO.ai的兴趣。使用机器学习,回归在VSO.ai中进行优化,以便首先运行高投资回报测试,并自动进行分析以定义规定的见解。

瑞萨凭借VSO.ai取得引人注目的成果

在观察到VSO.ai的积极成果后,由于瑞萨目前使用新思VCS功能验证解决方案。无需对设计或测试平台代码进行任何修改,VSO.ai就可以集成到现有的VCS回归环境中。

正如SNUG Japan 2023所强调的那样,瑞萨通过使用VSO.ai,能够使用更少的定向测试,对相同的覆盖率进行更短的回归,并改进对未命中覆盖率的根本原因分析。瑞萨无需对庞大的数据集进行手动分析,就可以利用VSO.ai帮助他们的验证工程师更快地达到覆盖率目标。这使得能够在相同的计算预算内运行更多回归,从而更好地利用硬件并更早地发现缺陷,这是验证的最终目标。

最终结果不言自明:

使用相同数量的测试将覆盖率提高了10%,结果质量更高(QoR)

将回归测试列表缩减2倍

将覆盖漏洞减少90%

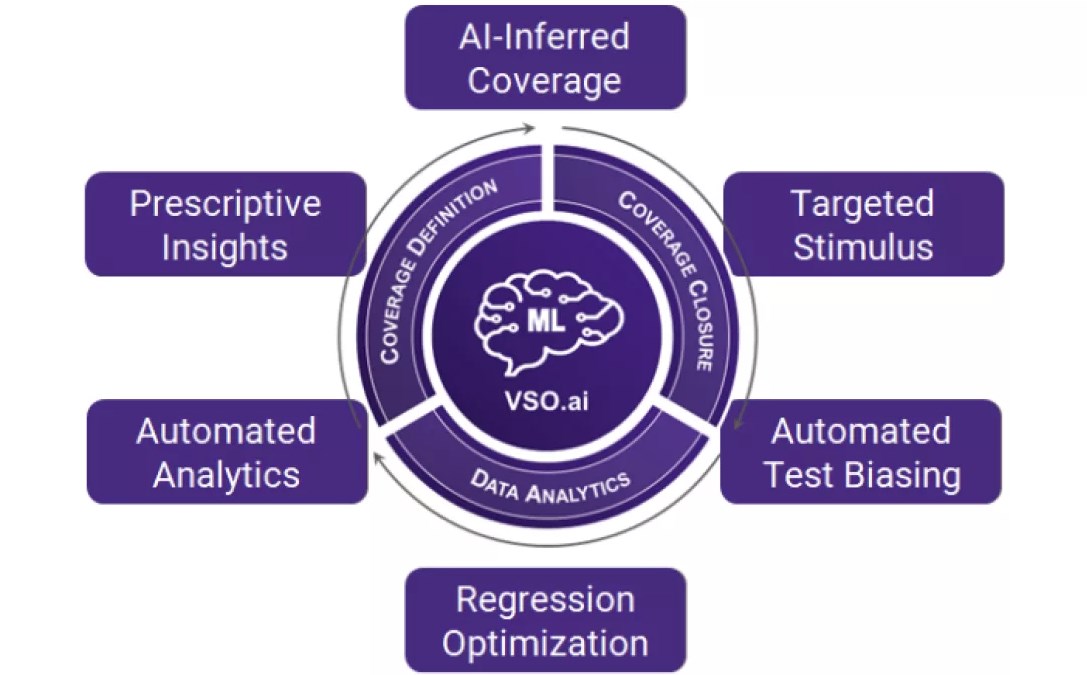

下图突出显示了VSO.ai解决方案的主要使用案例。

瑞萨R&D核心知识产权部门的知识产权开发总监田崎敬浩·池野表示:“由于设计复杂性的增加,使用传统的人在回路技术很快就难以满足质量和上市时间的限制。“使用Synopsys.ai EDA套件的一部分Synopsys VCS进行人工智能驱动的验证,我们在减少功能覆盖漏洞方面实现了高达10倍的改进,IP验证生产率提高了30%,证明了人工智能有能力帮助我们应对日益复杂的设计挑战。”

瑞萨工程团队现在可以专注于设计创新和更高价值的程序,同时击败竞争对手进入市场,而不是花费大量时间编写定向测试,从而延长上市时间并仍可能导致漏洞逃逸。

VSO.ai是Synopsys.ai人工智能驱动的EDA套件这提高了整个EDA流程的效率,以应对市场需求增加的设计复杂性,减少人工劳动,并利用可在整个芯片开发过程中收集的可行见解。

要了解有关VSO.ai的更多信息,请注册SNUG Silicon Valley 2024,参加由NVIDIA举办的技术会议:借助Synopsys VSO.ai、ICO和VCS-UNR公司减少人工工作量并实现覆盖目标。

-

soc

+关注

关注

38文章

4514浏览量

227631 -

瑞萨

+关注

关注

36文章

22431浏览量

89754 -

Synopsys

+关注

关注

2文章

161浏览量

91282

发布评论请先 登录

【瑞萨RA6E2地奇星开发板试用】+初识地奇星

【直播预告】RT-Thread带你首发体验:基于瑞萨RA8P1 MCU的Titan Board | 问学直播

瑞萨电子打造高级BLE、Wi-Fi和NFC解决方案

瑞萨邀您相约elexcon 2025深圳国际电子展

基于瑞萨64位MPU RZ/G2L的uboot串口多波特率支持介绍

Banana Pi 最新边缘 AI 系统模块 BPI-AI2N 采用瑞萨电子 RZ/V2N

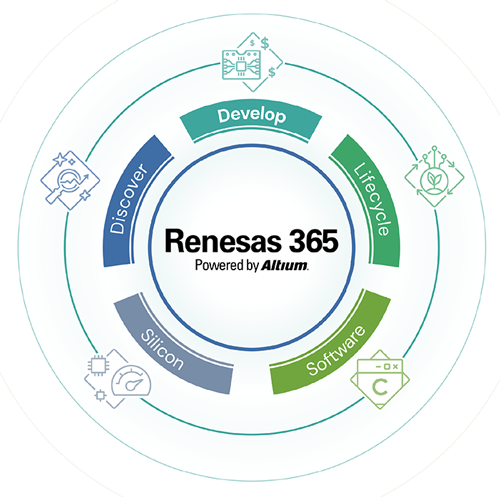

瑞萨365 深度解读

西门子利用AI来缩小行业的IC验证生产率差距

新思科技VSO.ai如何颠覆芯片验证

【RA-Eco-RA4M2开发板评测】初学瑞萨-使用瑞萨flash programmer烧录程序

瑞萨新款RZ/V2N视觉AI MPU产品介绍

Banana Pi 与瑞萨电子携手共同推动开源创新:BPI-AI2N

Imagination GPU为瑞萨R-Car Gen 5系列SoC提供强大高效的算力

江西萨瑞微电子接受江西日报专访,展现蓬勃发展新态势!

瑞萨如何利用Synopsys VSO.ai将SoC验证生产率提高30%

瑞萨如何利用Synopsys VSO.ai将SoC验证生产率提高30%

评论