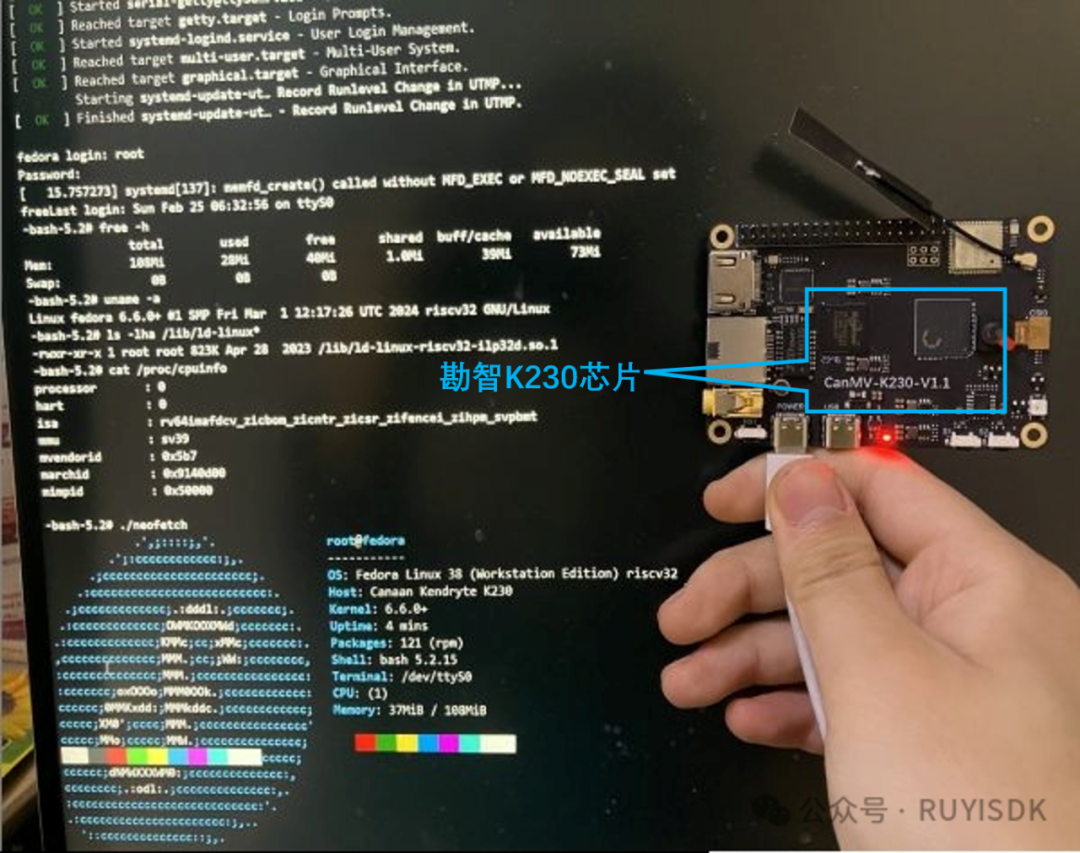

嘉楠科技(Canaan Inc.)(纳斯达克股票代码:CAN)开发的勘智K230芯片在Fedora 团队的努力下完成适配RISC-V 新32位技术,节省内存的同时降低了成本,展示了嘉楠科技勘智K230芯片开发板强大的功能应用能力。同时,PLCT实验室与达摩院-玄铁团队携手,通过采用松弛扩展寻址技术,克服了传统32位架构在现代操作系统中的性能局限,为新32位工具链的创新应用奠定了坚实基础。

松弛扩展寻址

历史上,64ILP32 ABI的实施面临着的主要障碍是:32位指针与64位寄存器之间的不匹配问题,这不仅引起性能损失,还增加了编译器的复杂性。虽然零扩展寻址(Zero-extend Addressing)在x86-x32和aarch64-ilp32 ABI中得到采用,但额外的零扩展指令降低了程序效率。与之相比,32ILP32和64LP64 ABI因指针长度与寄存器宽度一致,避免了这种性能开销。

面对这些挑战,我们首先考虑了符号扩展寻址(Sign-extend Addressing),它在一定程度上减缓了零扩展的性能问题,但增加了编译器和内核实现的复杂度。于是,我们提出了松弛扩展寻址(Relax-extend Addressing)方案,它通过硬件的指针掩码功能,允许在执行32位寻址操作时忽略64位寄存器的高32位,大幅简化了编译器工作,降低指令数量,并保持了安全性与可靠性。我们对以上三种寻址模式总结如下:

●抹零扩展寻址:传统方法,需要编译器生成额外的的指令来清零高32位,导致性能损失。

●符号扩展寻址:改良方案,通过操作系统页表的双重映射,合法化32位符号位扩展,缓解零扩展的性能开销。

●松弛扩展寻址:创新方案,依赖处理器硬件掩码来实现高效寻址,彻底消除了寻址时的性能损失。

因此,松弛扩展被我们选定为 RV64ILP32 ABI 的默认寻址模式,它要求 RISC-V 64位处理器支持寻址掩码功能,对硬件设计提出了新的要求。我们在 QEMU 上实验该功能,并证明了基于松弛扩展寻址模式的 RV64ILP32 工具链的有效性。

新32位内核

新32位工具链基于 RISC-V 64ilp32 ABI,融合了松弛扩展寻址技术,让64位硬件流畅运行新32位软件。我们在 qemu 上实现了硬件松弛扩展寻址模式,并用新工具链构建了业内首款新32位Linux内核。

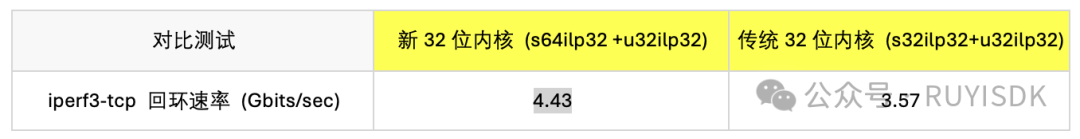

与传统32位对比,尽管新32位和传统32位都是32位Linux操作系统软件,但新32位得益于64位指令集,其性能显著优于传统32位:

如上图所示,新32位内核的 iperf3-tcp 测试大幅领先,在软件 ABI 相同的情况下,使用 64 位指令架构能极大提升操作系统的性能。本次qemu 测试仅供参考,请联系硬件供应商获得真实的性能差距报告,本测试用例已在工具链发布包内,请大家直接下载自行体验,以下动画是测试的全过程:

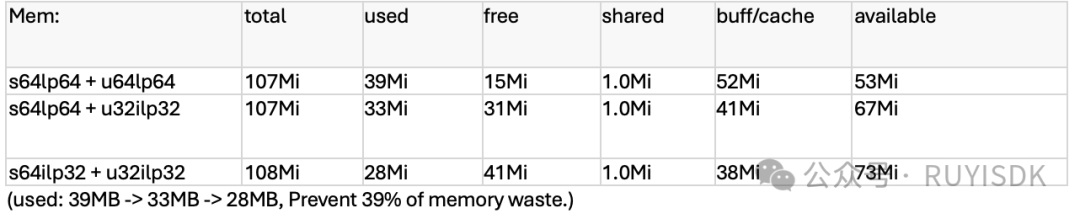

与传统64位对比,Fedora团队完成了RISC-V新32位在嘉楠科技勘智K230芯片硬件平台的适配,新32位避免了39%的内存浪费,其成本优势使 Fedora RISC-V 能在嵌入式领域有更广泛的应用,具体请参考:

新32位工具链

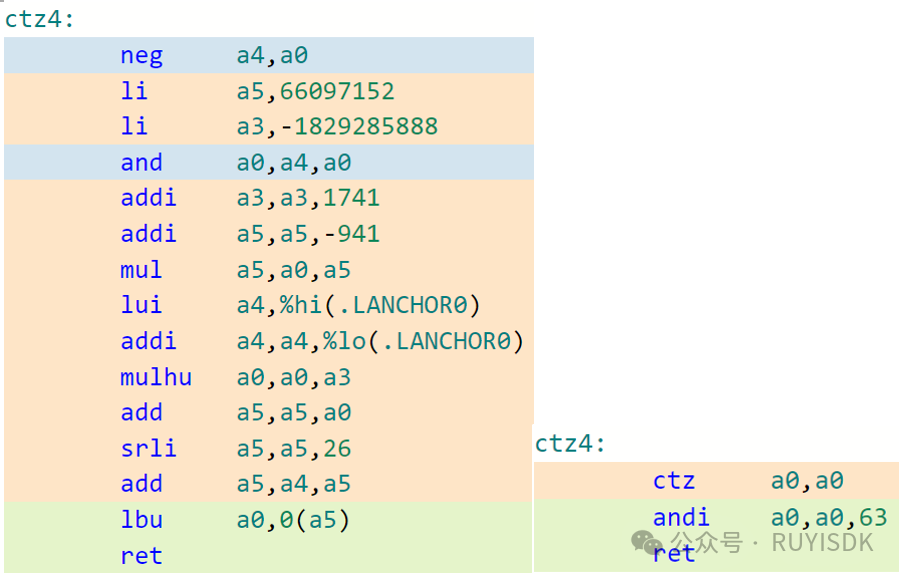

让32位软件运行在64位硬件上不仅更快而且更省,这正是我们新32位编译器的优势所在,不禁让人想起中国古代田忌赛马的故事,与传统32位比性能,与传统64位比成本。换言之,新32位就是要取代传统32位,与64位形成互补。在进一步的测试中,我们观察到了传统32位的明显不足:

如上图所示,在处理长数据类型时,传统32位的编译器生成了超过10条额外指令来操作保存的变量。相反,当采用新32位工具链时,编译器会直接利用64位指令来处理这些数据,大幅度减少了所需指令的数量。

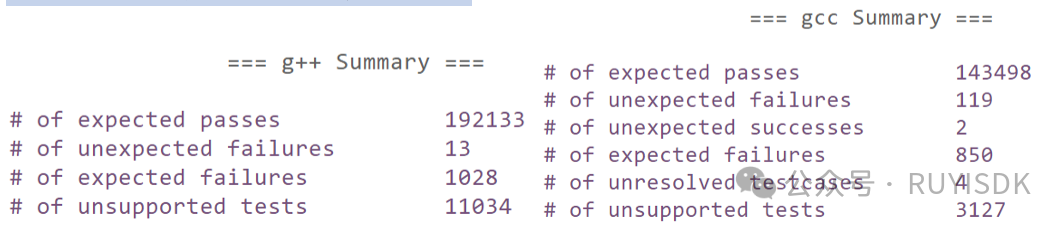

本次发布的新32位工具链通过了33万个测试用例,其中包含 192133 个 g++用例, 与 143498 个 gcc 用例,全面覆盖编译器的各项功能,测试结果与 GCC13 release 保持一致,达到产品级质量要求。相比传统32位,它的优势如下:

●更强大的性能:新32位编译器在处理长数据类型时更加高效,因为它无需进行额外的寄存器拼接或零扩展操作。这可以显著减少指令数量,提高程序的执行效率,特别是在涉及大量长数据类型操作的情况下。

●更好的兼容性:新32位编译器可以与传统64位编译器兼容,因为它们基于相同的硬件指令集。这意味着开发者可以更轻松地将现有的64位汇编代码迁移到新32位平台上,而无需做出太多修改。

●更多的扩展性:随着技术的发展和需求的增长,对更大的内存空间和更高性能的需求也在不断增加。新32位的硬件平台可以为未来的扩展性提供了更好的支持,因为它能无缝切换到传统64位以满足更高要求的应用程序。

●产品级的质量:新32位工具链经过大量测试验证,保证使用的正确性与稳定性,同时在RUYISDK开源仓库中进行维护更新,及时解决用户遇到的各种问题。

结束语

松弛扩展寻址技术在新32位工具链中扮演着关键角色,为嵌入式系统的开发和部署提供了全新的解决方案。作为业内首款基于松弛扩展寻址技术的新32位产品级开源工具链和Linux内核,标志着嵌入式系统开发领域的一次重要创新。我们热切期待开发者们积极参与到新32位的开发和完善中,共同提出宝贵的建议和意见,推动新32位不断发展。我们致力于建立一个健康和活跃的开源社区,将持续投入资源和精力,确保新32位的稳定性和可靠性,并不断改进和完善其功能和性能。在此,我们也呼吁更多的硬件厂商加入我们的阵营,共同推动新32位嵌入式系统的发展和创新,为行业带来更多的可能性和机遇。

关于嘉楠科技勘智K230芯片

嘉楠科技勘智K230芯片是全球首款支持 RISC-V Vector1.0标准的商用SoC,内置双核玄铁C908 CPU,主频高达1.6GHz。作为嘉楠科技勘智Kendryte系列芯片中的最新一代SoC产品,勘智K230芯片内置多个高清视频图像输入处理和智能硬件处理单元,兼顾高性能、低功耗和高安全性特点,可广泛应用于各类智能产品,如边缘侧大模型多模态接入终端、3D结构光深度感知模组、交互型机器人、开源硬件、智能制造、智能家居和智能教育硬件等众多领域。

审核编辑:刘清

-

机器人

+关注

关注

213文章

30580浏览量

219584 -

寄存器

+关注

关注

31文章

5589浏览量

129064 -

SoC芯片

+关注

关注

2文章

662浏览量

36832 -

RISC-V

+关注

关注

48文章

2793浏览量

51911 -

嘉楠科技

+关注

关注

1文章

32浏览量

5639

原文标题:嘉楠科技勘智K230芯片获玄铁团队与PLCT实验室新32位产品级工作链及Linux内核适配

文章出处:【微信号:CanaanTech,微信公众号:嘉楠科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【作品合集】嘉楠科技01 Studio K230开发板测评

【BPI-CanMV-K230D-Zero开发板体验】开箱以及开发板简介

【嘉楠堪智K230开发板试用体验】K230 AI 功能体验

嘉楠线上训练平台下载的文件,无法正常导入K230的SDCARD。请问该怎么解决

【嘉楠堪智K230开发板试用体验】CanMV K230 开发环境搭建

【嘉楠堪智K230开发板试用体验】开箱测评

【嘉楠堪智K230开发板试用体验】+03+巡线+舵机方向控制

【嘉楠堪智K230开发板试用体验】+02+基本功能测试

【嘉楠堪智K230开发板试用体验】高校竞赛-K230开发板-1

【嘉楠堪智K230开发板试用体验】+开箱测评+通电及点灯

【BPI-CanMV-K230D-Zero开发板体验】介绍、系统安装、工程测试

搭载双核玄铁C908 RISC-V CPU,BPI-CanMV-K230D-Zero开发板试用

RT-Thread Smart携手K230/K230D打造多核RISC-V高性能嵌入式操作系统

嘉楠科技勘智K230芯片完成适配RISC-V新32位技术

嘉楠科技勘智K230芯片完成适配RISC-V新32位技术

评论